RTL Finite State Machines in System Verilog

Published 10/2024

Duration: 57m | .MP4 1280x720, 30 fps(r) | AAC, 44100 Hz, 2ch | 382 MB

Genre: eLearning | Language: English

Published 10/2024

Duration: 57m | .MP4 1280x720, 30 fps(r) | AAC, 44100 Hz, 2ch | 382 MB

Genre: eLearning | Language: English

Finite State Machines are a fundamental building block in digital hardware designs.

What you'll learn

Learn the design pattern for Register Transfer Level (RTL) descriptions of Finite State Machines in Digital Hardware

Hands on simulation of RTL Finite State Machine with a self checking test bench

Synthesis of RTL Finite State Machines

Optimization of RTL Finite State Machine to reduce Latency

Requirements

Background in Digital Hardware Design (Electrical or Computer Engineering)

Exposure to an HDL (Verilog or VHDL) would be helpful

Taken course RTL Fundamentals in System Verilog (Recommended)

Description

This hands-on course on writing RTL (Register Transfer Level) for Finite State Machines (FSM) in System Verilog provides a structured approach to mastering FSM design for digital logic applications. The course builds on RTL fundamentals and is designed for those with a background in Digital Logic Design or Computer/Electrical Engineering at an intermediate level.

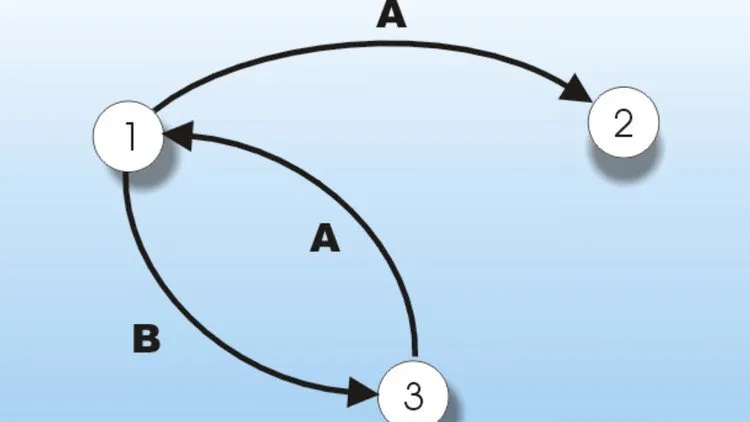

The course begins by introducing FSMs as a computational model for sequential processes, where a system transitions between finite states based on inputs and predefined rules. FSMs are used in both hardware and software to control processes such as communication protocols, power management, and error handling.

A core focus is on the "RTL FSM Design Pattern," which offers a structured method for describing FSMs in RTL. It includes key steps like defining state encoding, assigning next states using always_ff, and managing state transitions in always_comb. One practical application covered is the implementation of the Greatest Common Divisor (GCD) using the FSM pattern, with detailed discussions on simulation, synthesis, and optimization to minimize states.

The course also emphasizes the efficiency of FSM design, introducing techniques such as one-hot encoding, which simplifies logic and reduces power consumption. However, the trade-offs between one-hot and binary encoding are discussed based on state count and application needs.

The course is supplemented with hands-on examples and simulations, leveraging platforms like a custom built docker image for simulation + synthesis or edaplayground dot com for practical experience.

Who this course is for:

Hardware Engineers (EE, CE or CS) who want to enter the Chip Design field

Practicing FPGA and ASIC engineers who want to build on their existing skills

More Info