Randomization and IPC in SystemVerilog

Duration: 12h 42m | .MP4 1280x720, 30 fps(r) | AAC, 44100 Hz, 2ch | 3.8 GB

Genre: eLearning | Language: English

Duration: 12h 42m | .MP4 1280x720, 30 fps(r) | AAC, 44100 Hz, 2ch | 3.8 GB

Genre: eLearning | Language: English

Simple course to learn advanced verification technique of Randomization and IPC in SystemVerilog.

What you'll learn

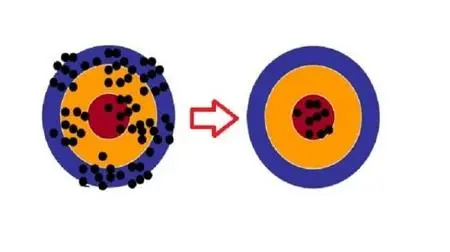

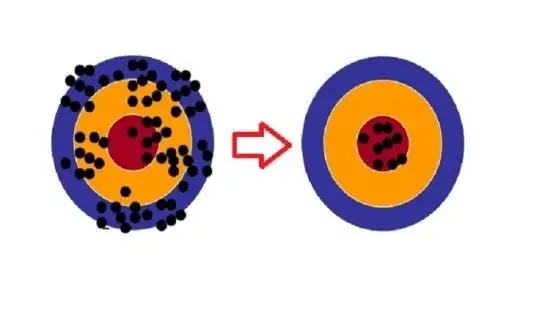

Difference between directed and random testing

What is randomization and why verifiation engineer should know it

How to do ramdomization in SystemVerilog

How to do constrained randomization

Various options available during randomization

How control thread execution happens in Verilog

Event communication in SystemVerilog

Semaphore in SystemVerilog

Mailboxes in SystemVerilog

How to write Testbench using IPC

Requirements

It is expected that knowledge of fundamentals of verification and basic constructs of SystemVerilog are known

Familiarity with Object Oriented Programming is an added advantage

Verilog programming and fundamentals of FPGA programming are supposed to be already known

Description

VLSI industry requires more verification engineers and less design engineers. Roughly this ratio is around 70 to 30 percent respectively. Because todays designs are not only very complex but also challenging to verify due to technological advancements at all the levels of design. There are many techniques that are required to be known to today's verification engineers. How to design powerful and flexible test bench is always a challenge for verification engineers. SystemVerilog provides various constructs which can ease the job of verification engineer. However one should have basic knowledge about those constructs.

This course is introduced for learners who wants to learn advanced verification techniques of randomization and inter-process communication (IPC) in SystemVerilog. It is assumed that learner is aware of the basic constructs of SystemVerilog and object oriented programming. In this course, students will learn when to do randomization, how to do constraint randomization, what are various inter-process communication techniques etc. Various IPC techniques like events, semaphores and mailboxes will be introduced. Course is being taught with various examples and learner can monitor self-progress by attempting quiz in each section. Students can try to simulate all the examples discussed in the course in EDA Playground and verify the theoretical concepts. After learning this course, students will be able to apply randomization and IPC techniques while designing test bench.

Who this course is for

This course is for students and engineers who wants to learn basics of randomization and IPC in short time.

Verification engineers who wants to refresh concepts of randomization and IPC.

More Info