FPGA Design Learning VHDL

MP4 | Video: AVC 1280x720 | Audio: AAC 44KHz 2ch | Duration: 6 Hours | 1.66 GB

Genre: eLearning | Language: English

MP4 | Video: AVC 1280x720 | Audio: AAC 44KHz 2ch | Duration: 6 Hours | 1.66 GB

Genre: eLearning | Language: English

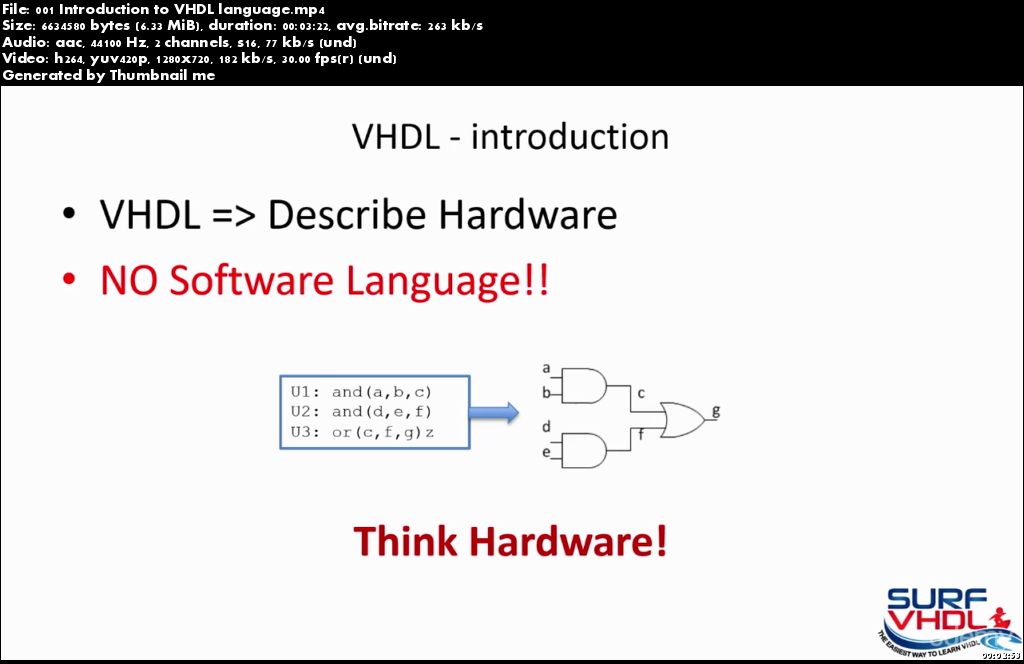

From zero to VHDL designer. Learn how to implement your VHDL design on FPGA starting from scratch

How many times you waste your time in finding some examples useful to resolve your VHDL problems and didn't get anything useful?

Nowadays we are in a “lucky period” because we can get any information we need with few clicks of the mouse. With respect to few years ago, when the access to the information was very difficult, now we can have the possibility to have good material fast and for free.

But… There is the other side of the coin.

It is true that we have a lot of information for free, but not all the information we have is a good stuff. Many times we need a huge amount of time to filter good stuff from a useless material. Even if we get the information for free we often don't think about to the time we are wasting and to the "equivalent money" we are losing wasting this time.

In Surf-VHDL, we have more than 15 years in FPGA/ASIC VHDL design.

In this course, you will learn the basic rules to implement and efficient hardware design and how to apply these rules using VHDL.

You will learn all the basic of the VHDL syntax:

Entity / Architecture pair definition

Concurrency

VHDL Coding Style: Structural, Behavioral, Sequential

Event and Transaction

Delay Modeling: Inertial vs Transport delay

Concurrent Conditional Signal Assignment

Understanding Driver & Source concept

Parametric Design: Generics

VHDL Types and Data object

VHDL Types of Data Object: Signal, Variable, Constant and FILE

Type bit vs ulogic vs std_logic

Signed and Unsigned Data Types

Type Conversion and Type Casting

Subtype definition

Process Statement

Sequential Conditional Statement: IF and CASE

Sequential-Iterative Statement: FOR and WHILE

The Assert Statement

Sequential WAIT Statement

Sensitivity List vs WAIT Statement

Procedure and Function

Packages

Concurrent iterative Statement FOR GENERATE

Concurrent conditional Statement IF GENERATE

TextIO package: Read/Write from file

Test bench design and simulation

In the LAB section you will learn how to implement:

Heart-bit design: let's start with a blinking led

Seven segment display: write a VHDL code and drive a seven segment display

UART: learn how to implement a UART 16650 compatible with internal FIFO

Command Parser: VHDL design that contains the LAB above. Connect your board to a PC and start communicate with it.

All the LABs are provided with the VHDL code that you have to complete and simulate.

In the LAB videos there will be addressed the exercise solution: you will learn how to implement the lab VHDL code, simulate and layout on FPGA