Digital Design using Verilog HDL programming with practical

Video: .mp4 (1280x720, 30 fps(r)) | Audio: aac, 44100 Hz, 2ch | Size: 1.63 GB

Genre: eLearning Video | Duration: 34 lectures (3 hour, 58 mins) | Language: English

design & verification with examples & applications

Video: .mp4 (1280x720, 30 fps(r)) | Audio: aac, 44100 Hz, 2ch | Size: 1.63 GB

Genre: eLearning Video | Duration: 34 lectures (3 hour, 58 mins) | Language: English

design & verification with examples & applications

What you'll learn

Learning Verilog HDL Programming concepts with examples

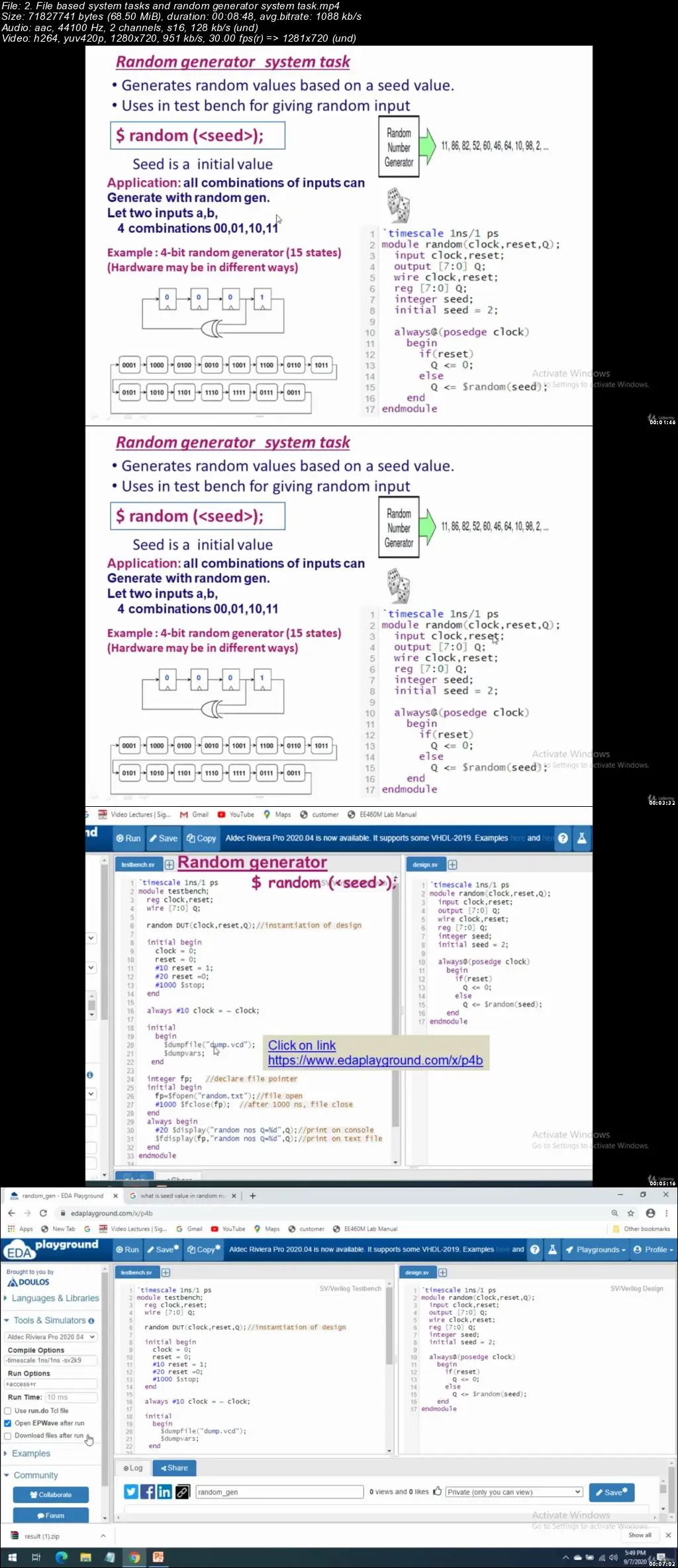

Writing complete design & test bench programming for modules like Memory controllers, FIFO controller, Random data generators, Error detection correction using Hamming code and file representation input & output etc.

How to use task & system tasks in Test bench

How to draw Finite state machine (FSM) and how to write verilog program for any FSM and Sequence detector FSM

Requirements

basic in C-programming

basics Digital design ( we are designing digital circuits, but no need of digital knowledge to design a complex circuits)

Description

This is a complete Verilog HDL programming course for beginners as well as higher level, as it is from scratch to the application level. This course not only discuss the concepts in Verilog HDL programming but also discuss the applications.

This course gives clear picture on simulation and writing a test bench using task and system task and illustrated with examples. For that, it provides file based examples like writing data in to file, reading data from file and loading data in to memory. Also some general examples like counter, clock diver using counter, pulse generator and random generator.

This course used to build Finite State Machines (FSM) diagram from the requirements and realization of FSM in to hardware model, then translation of hardware model FSM into verilog code for both Mealy & Moore and demonstrated with examples.

This course also shows some projects like Memory controller, FIFO controller and Error detection & correction using Hamming code. and finally it gives basic knowledge on FPGA's.

Who this course is for:

Undergraduate Electronics and computer science engineering students

Graduate students who planning their career in VLSI domain front end (Design & verification)

Advanced under graduate students, who willing to do project in front end VLSI design