Ic/Fpga Design P2: Verilog For Design And Verification

Published 1/2025

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 4.90 GB | Duration: 9h 1m

Published 1/2025

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 4.90 GB | Duration: 9h 1m

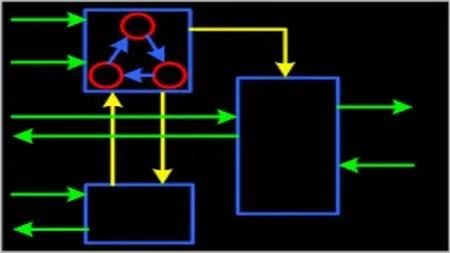

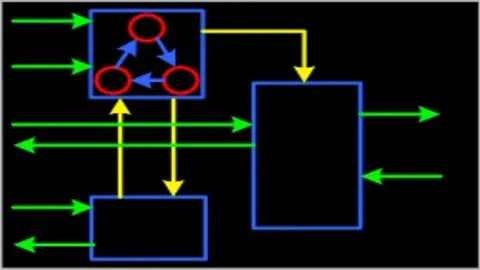

Consistency between circuit diagram, RTL code and waveform

What you'll learn

Common used Verilog syntaxes for design and verification

Install Verilator and GTKwave on windows OS(using WSL)

Descript combination logic (basic logic gates, MUX, decoder, one-hot decoder)

Descript sequential logic (DFF with sync/async reset, ounter, edge detect, shift registers, sequence check, sync_fifo)

Design finite state machine (FSM)

Write testbench

Using Verilator and GTKwave to debug a design

Common mistakes for synthesis (incomplete sensitive list, latch, multi-driven, combination logic loop)

Practice time: z-scan, complex sequence check (FSM)

Requirements

Basic C or C++ programing language

Basic knowledge of digital fundamental

Description

If you don't need Q&A, you can also find a free version of this chapter at my homepage of Udemy.Quick master through examples and coding exercises, in videos less than 10 hours. After study, you can have the ability of consistency between circuit schematic, Verilog code and waveform. That’s given anyone of them, you can figure out the other two. In this chapter (will be divided to several free sections), I’ll explain:1: Digital IP/IC design flow;2: Quick review of digital fundamental3: Install Verilator and GTKwave4: Common used Verilog syntax for design and verification5: Design combination logic(basic gates, MUX, decoder, one-hot decoder)6: Design sequential logic(sync-DFF, async-DFF)7: Design small but useful block(counter, edge detect, shift registers, sequence check, sync_fifo)8: Design FSM(finite state machine)9: Design basic testbench10: Common mistakes for synthesis(incomplete sensitive list, latch, multi-driven, combination logic loop)11: Practice time: design and verify z-scan and complex sequence check(FSM)This is chapter 2, section 1 of whole Digital IC and FPGA design course.In the whole course, I will introduce fundamentals of digital IC and FPGA design, with 12+ coding exercises and 3 course projects.Theory part: MOS transistor -> logic cells -> arithmetic data path -> Verilog language -> common used HW function blocks and architecture -> STA -> on-chip-bus(APB/AHB-Lite/AXI4) -> low power design -> DFT -> SOC(MCU level).Function blocks and architecture: FSM, pipeline, arbiter, CDC, sync_fifo, async_fifo, ping-pong, pipeline with control, slide window, pipeline hazard and forward path, systolic.Project: SHA-256 algorithm with simple interface, SHA-256 with APB/AXI interface, 2D DMA controller with APB/AXI interface.After explaining of each HW architecture, I will give you a coding exercise, with reference code. Coding difficulty will begin from several lines to fifty lines, more than 100 lines, then around 200 lines. While the final big project will be 1000+ lines.I suppose these should be essential knowledge and skills you need master to enter this area.I will try my best to explain what-> how-> why and encourage you to do it better in this course.Please browse to my homepage on Udemy to obtain information about each chapter of this course.

Overview

Section 1: Introduction and Preparation

Lecture 1 Introduction

Lecture 2 Digital IP and IC Design Flow

Lecture 3 Quick Review of Digital Fundamental

Lecture 4 Install Verilator and GTKwave

Section 2: Using Verilog to Describe Basic Logic Gates and Simulation

Lecture 5 Hello World in Verilog

Lecture 6 Describe Combination Logic and Sim

Lecture 7 Describe Sync and Async DFF and Sim

Lecture 8 Power-Up sim value difference for Verilator and other sim tools

Section 3: Common Used Verilog Syntaxes

Lecture 9 Verilog Syntanx: Declare and Operators

Lecture 10 if-else if-else and case statement

Lecture 11 sign extension and one-hot decoder

Section 4: Describe counter, edge detect, shift regs and common mistakes for RTL

Lecture 12 Describe small but usefull circuit: counter, edge detect, shift regs

Lecture 13 Common mistakes: Incomplete Sensitive list, Latch, Comb. loop, Multi-driven

Section 5: Practice time: design and verify z-scan function

Lecture 14 design and verify z-scan function

Lecture 15 Reference design and verification code for z-scan

Lecture 16 Project Directoies and Makefile

Section 6: Finite States Machine Design

Lecture 17 Design Finite States Machine

Lecture 18 Using FSM to Design Sequence Detect Function

Lecture 19 Sequence Detect by Shift Regs

Section 7: Function and Task

Lecture 20 Function and Task Syntax

Lecture 21 Task example in testbench

Section 8: Execution Order of Verilog in SW View

Lecture 22 Execution Order of Verilog in SW View

Section 9: Concept of Design Testbench

Lecture 23 Concept of Design Testbench

Section 10: Advanced Topics

Lecture 24 Generate and Parameter Construct

Lecture 25 Concept of Design Large Scale Designs

Section 11: Final Exercise: Complex Sequence Detection

Lecture 26 Bonus Section

Anyone who wants to study Verilog and digital IC/FPGA design