Advance Physical Design Workshop Using Openlane/Sky130Pdk

Published 1/2024

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 6.08 GB | Duration: 12h 3m

Published 1/2024

MP4 | Video: h264, 1920x1080 | Audio: AAC, 44.1 KHz

Language: English | Size: 6.08 GB | Duration: 12h 3m

Sky130-pd-workshop

What you'll learn

Getting familiar to EDA tools

Beginning with floorplan

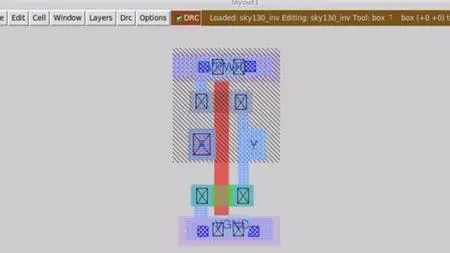

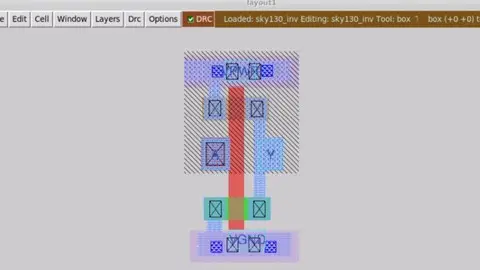

Spice model of the cmos inverter and its characterization using ngspice

Merging our inverter with the design

Finally we do Routing

Requirements

No prerequisties

Description

Welcome to the Advanced Physical Design Workshop leveraging openLANE and the sky130 Process Design Kit (PDK). This intensive course is designed for experienced VLSI engineers and digital design professionals seeking to deepen their understanding of physical design methodologies.Throughout the workshop, participants will delve into advanced topics, including but not limited to floorplanning, placement, clock tree synthesis, routing, and signoff checks. The course places a strong emphasis on hands-on experience, providing participants with practical insights into the nuances of using open-source EDA tools and the sky130 PDK.The curriculum is structured to guide participants through the entire physical design flow, fostering a comprehensive understanding of the challenges and optimizations involved. Real-world case studies and industry best practices will be explored, ensuring that participants gain valuable insights applicable to their professional endeavors.By the end of the workshop, attendees will have the expertise to navigate intricate physical design scenarios, optimize designs for performance and power, and effectively utilize open-source tools for tape-out readiness. Join us on this journey to elevate your skills and stay at the forefront of VLSI design with openLANE and the sky130 PDK.Furthermore, the workshop explores emerging trends in physical design, touching upon topics like machine learning-driven optimization and design for manufacturability (DFM). Engage with industry experts, network with fellow professionals, and gain insights into the evolving landscape of advanced VLSI physical design. This workshop equips participants with the skills and confidence to tackle complex design projects and contribute meaningfully to the ever-evolving field of semiconductor technology.

Overview

Section 1: Day1

Lecture 1 Video1

Lecture 2 Video2

Lecture 3 Video3

Lecture 4 Video4

Lecture 5 Video5

Lecture 6 Video6

Lecture 7 Video7

Lecture 8 Video9

Lecture 9 Video8

Lecture 10 Video10

Lecture 11 Video11

Lecture 12 Video12

Section 2: Day2

Lecture 13 Video13

Lecture 14 Video14

Lecture 15 Video15

Lecture 16 Video16

Lecture 17 Video17

Lecture 18 Video18

Lecture 19 Video19

Lecture 20 Video20

Lecture 21 Video21

Lecture 22 Video22

Lecture 23 Video23

Section 3: Day3

Lecture 24 Video24

Lecture 25 Video25

Lecture 26 Video26

Lecture 27 Video27

Lecture 28 Video28

Lecture 29 Video29

Lecture 30 Video30

Lecture 31 Video31

Lecture 32 Video32

Lecture 33 Video33

Lecture 34 Video34

Lecture 35 Video35

Lecture 36 Video36

Lecture 37 Video37

Lecture 38 Video38

Lecture 39 Video39

Lecture 40 Video40

Lecture 41 Video41

Lecture 42 Video42

Lecture 43 Video43

Lecture 44 Video45

Lecture 45 Video44

Lecture 46 Video46

Lecture 47 Video47

Section 4: Day4

Lecture 48 Video48

Lecture 49 Video49

Lecture 50 Video50

Lecture 51 Video51

Lecture 52 Video52

Lecture 53 Video53

Lecture 54 Video54

Lecture 55 Video55

Lecture 56 Video56

Lecture 57 Video57

Lecture 58 Video58

Lecture 59 Video59

Lecture 60 Video61

Lecture 61 Video60

Lecture 62 Video62

Lecture 63 Video63

Lecture 64 Video64

Lecture 65 Video65

Lecture 66 Video66

Lecture 67 Video67

Lecture 68 Video68

Lecture 69 Video69

Lecture 70 Video70

Lecture 71 Video71

Lecture 72 Video72

Lecture 73 Video73

Lecture 74 Video74

Lecture 75 Video75

Section 5: Day5

Lecture 76 Video76

Lecture 77 Video77

Lecture 78 Video78

Lecture 79 Video79

Lecture 80 Video80

Lecture 81 Video81

Lecture 82 Video82

Lecture 83 Video83

Lecture 84 Video84

VLSI Engineers