Designing Digital Systems using Verilog - RAHDG438

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz

Language: English | Size: 4.53 GB | Duration: 14h 39m

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz

Language: English | Size: 4.53 GB | Duration: 14h 39m

Build the foundation needed on becoming an expert in Verilog in 4 weeks - Rahsoft Electrical Engineering Department

What you'll learn

a good understanding of Verilog

Basic Concepts of Digital

State Diagrams

Moore vs Mealy Model

Flip Flop

JK Latch

SR Latch

Registers

Quartus Software

Counters

Node Finder

Multiplexer

Quartus Simulation

Functional Block Diagram

ALU

Always@

FSM

Description

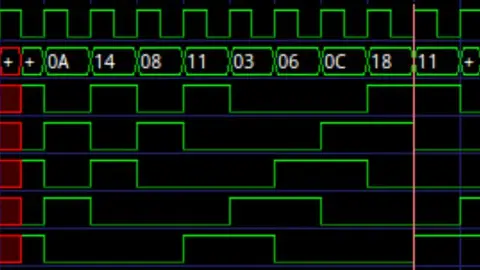

In RAHDG 438 we’ll Focus on designing different types of digital systems using Verilog language code then we simulate those in the Quartus software and at the end we do the implementation. It includes Design and analysis of latches and flip-flops. Number of digital designs have been designed in Verilog language to make you understand them better.

This course goes over different learning objectives in Verilog such as Fundamental Verilog Construct, Creating simple designs and developing Verilog test environment of significant capability and complexity. The design and analysis of synchronous state machines. Each topic will have many examples which goes over them briefly with different parts. By end of each chapter there will be a quiz for you to test your understanding of that specific chapter.

Core subject of this course is digital design flow. Topics include operators, Blocking and non-blocking assignments, RTL coding process, registers, flip flop, and latches. By end of the course, you should be able to design, simulate, implement, and troubleshoot our Verilog codes using appropriate techniques and test bench.

This course is mostly for academic level Engineering students in different universities around the world.

Since you would be having a lifetime access to this course you would be able to revisit during your career as year passes to refresh your memory.

Instructor

The instructor of this course is Mehrad Nahouri. He has an Associates in Electrical Engineering concentration on digital field and is a lecturer at Rahsoft.

What is the target audience?

This course is for students working in Verilog field.

Undergraduate students

Electrical Engineer

Computer Engineer

Graduate students taking Verilog course

Researchers in Verilog field

Course content

Introduction

Basic Concepts of Digital

State Diagrams

Moore vs Mealy Model

Flip Flop

JK Latch

SR Latch

Verilog

Registers

Quartus Software

Counters

Node Finder

Multiplexer

Quartus Simulation

Functional Block Diagram

ALU

Always@

FSM

Who this course is for

Electrical Engineers

Computer Engineers

Electrical Engineering Students

Computer Engineering Students

Who this course is for

This course is for students working in Verilog field.

Electrical Engineering Undergraduate students

Electrical Engineer

Computer Engineer

Graduate students taking Verilog course

Researchers in Verilog field