Cadence SSV Release Version 20.20.000 | 5.6 Gb

The SSV Release Team has unveiled the Cadence Silicon Signoff and Verification (SSV) 20.20.000. This solution encapsulates a set of tools that address a series of electrical and physical signoff and verification steps that designers must perform on their design before tapeout.

Featured Enhancements

Here is a list of some of the important updates made to Tempus Timing Signoff Solution for the 20.2 production release:

Tempus

Tempus Power Integrity Flow

The Tempus Power Integrity Analysis (Tempus PI) solution provides the capability to run IR analysis that is timing-aware, and timing analysis that is IR-aware. The Tempus PI is a seamless integration of the Tempus static timing analysis (STA) and Voltus power and IR drop technologies.

Infinite Depth Path-Based Analysis (IPBA)

The Tempus software supports infinite depth path-based analysis (IPBA). This feature runs faster analysis (vs full depth exhaustive PBA (EPBA)) and attains PBA design coverage with no depth limit per endpoint.

SmartScope Supports Timing Context Models

The Tempus SmartScope feature allows you to perform timing analysis with block context models - which is a top-down hierarchical STA technique. The context model feature allows block timing/glitch analysis and closure with realistic constraints instead of pessimistic block budgeted constraints.

Large Number of Active Timing Views Using SmartMMMC

The Tempus software provides the ability to handle a large number of active timing views using the SmartMMMC feature. This feature is used to enable reduced memory and faster run time when many timing views are enabled during timing or power ECO fixing stage.

New Metal ECO Flow

A new Metal ECO flow, also called Post-Mask ECO, using the Gate Array filler cells has been introduced. In this flow, the timing closure engine performs the netlist change without touching the base layer mask.

2340489 Delay increase for instance in session with SIV -pg_pin and single list library set

2321299 Errors during post mask Tempus ECO

2320990 Tempus errors out during update_library_set after read_design in some cases

2319731 If useOrigIdxForSubsetWeight:true fixLCSubset:true are not default with LC, then user control is needed

2319569 Protect default change in bus attacker so that it does not change results unexpectedly

2318070 Tempus shows out of memory issue

2313446 report_noise -threshold not being reflected properly in the glitch report

2309701 Wrong PBA delay for PAD cell having bidi pin

2309001 accumulated_small_attacker_factor should have no influence with accumulated_small_attacker_mode current

2308365 set_si_mode -individual_glitch_simulation_mode 1 causes Cpl from PI not to combine with Prp

2307946 signoffOptDesign -drv: misleading "could not be fixed" message

2304384 The software exits without a message at create_glitch_boundary_model

2304384 Tempus exits without a message at create_glitch_boundary_model

2303761 Tempus issues in some cases

2303761 Tempus errors out in some cases

2302359 Voltage mismatch between MSV and RT/AAE due to incorrect related ground net

2302329 Port does not inherit correct voltage from set_driving_cell

2299400 In Tempus GUI ECO - using interactive ECO or timing debug - generates invalid ECO commands

2294298 set_glitch_threshold commands for non-bmod nets are being saved

2291921 Tempus issues TA-1024 ERROR even though timing_hierarchical_context_continue_on_top_block_clock_mismatch is set to true

2287435 report_slack_histogram flags IMPSYT-644 with -infile option

2279317 Tempus ECO opt_signoff -hold ends with **ERROR: (IMPSE-110): command returned bad code: 5

2275663 Stack track in create_timing_budget

2275191 CUI: opt_signoff stops in Innovus/CUI: opt_signoff got a SEGV in Innovus

2275188 Tempus ECO timing does not match with report_timing

2274123 Enhance SLBBV flow to allow different voltage specifications for clock and data

2274027 Issues with get_cells -filter "full_name"

2264247 Scope Analysis - SCOPE-2213 errors out due to incorrect netlist at a corner case in BM generation

2263678 Tempus ECO flow errors out while reading libraries

2263288 Clock buffer delay time mismatch between baseline and multi library voltage interpolation

2262796 LEF/DEF - def reader should filter out the Block Pin in PINPROPERTIES section in the DEF

2259758 Rail analysis error

2258257 Tempus errors out with update_timing with SI turned on

2257050 Modules that contain zero-pin instances get an empty module complaint because zero-pin instances are discarded by default

2256195 optDesign -drv is not fixing high fanout nets when max fanout is set using set_max_fanout

2255774 Block port's case_value is not applied to the pin connected to port in context run

2255281 Slack difference because of CPPR difference between flat and block with context on reg-out paths

2253802 IMPESI-3423 should not be applied to multi-stage cells

2253693 Enhance set_driving_cell for voltage interpolation

2253459 Tempus errors out after report_timing in some cases

2252234 Hierarchical STA: PBA incremental delay difference between flat and context runs

2249613 set_disable_timing is not working for linked library cells (LPPI libraries)

2249371 IPBA setup reporting is stuck for several hours

2246611 Issue in printing the current value of alias

2246489 Unconstrained Skew check: -through instance is not working , with -to path is reported instead of -through

2246200 Spice mode - The simulation time is too large (1.2us) for a net with clock frequency at 1GHz in Spice Deck

2245791 Errors with global timing_path_based_exhaustive_max_paths_limit

2242840 Odd time_design -expanded_views results

2242463 Skew Checks Script on Unconstrained Paths: -max_slack INFINITY returns no path exists and capturing_clk_latency is NA

2241451 Derates application is getting lost in save/restore flow in Tempus

2239599 IMPESI-3423 is printing on multi-stage cells - also preventing ROP from being performed

2238138 VH run_path_simulation SPICE deck grabs area from 1st result rather than worst glitch SPICE result and shows NaN

2237532 optDesign -PostCTS errors out

2237050 Tempus errors out in some designs

2236947 Tempus errors out while sourcing constraints after **WARN: (TCLCMD-1531): 'set_false_path' has been applied

2235477 Restoring DB takes a long time while loading the last AOCV file

2228168 Logical correlation causes significant slowdown in update_glitch

2225262 set_quiet_attacker is not being honored in 2nd iteration, even though report_noise -quiet_nets shows it quiet

2224523 High runtime for Tempus session restore when saved with UPF

2223965 report_noise -sort_by rcvr_peak is no longer working in some cases

2223760 report_timing -through <hier pin> errors out with -not_through [get_ports *]

2222121 create_cell_signal_em_model errors out with DIAG and pstack

2220186 Tempus errors out in reporting delay calculation in some cases

2220139 CCOPT creates clock opens on the pre-routed clock wires

2219493 CUI: time_design_signoff stops in some Innovus builds

2218744 Tempus errors out after command redirect 1.chk {check_timing…}

2215930 Tempus AOCV GBA mode stage count different when changed from SMSC to CMMMC

2215569 Tempus errors out for missing output_ccb definition in the input library

2214793 Stack trace during reading constraints

2209298 Tempus errors out when loading dotlibs without double quote data

2209149 TCL procedure errors out when copy-pasted in Tempus shell

2208886 report_case_analysis verbose: ERROR: (TA-115): Internal Error

2207763 Tempus errors out with constraints file with cms2sdc conversion flow

2205464 Tempus errors out in some cases

2205402 Valus error with TECHLIB-1230

2195265 WARN IMPESI-3047 is output only if DB is timed, need to be an ERROR and output in all cases

2187241 GBA and PBA reporting different timing for a path with all 1-input cells

2184757 check_timing command is reporting broken pattern (output->input->input->output) with loop option on some designs

2181322 create_spice_deck -run_path_simulation should pick the worst ROP corresponding to the worst RIP

2181282 All I/O paths are unconstrained when using the new timing context scope model

2177719 Stylus get_distributed_variables not working properly

2155484 Elaborate and improve the message IMPESI-3201 (Delay calculation failed for net) dump for different scenarios

2121432 Clock skew enabled ECO run errors out

1999024 create_spice_deck condition not matching the when condition from glitch report

1898471 Errors for range_collection command

December 2, 2020

2321299 Errors during post mask Tempus ECO

2320990 Tempus errors out during update_library_set after read_design in some cases

2319731 If useOrigIdxForSubsetWeight:true fixLCSubset:true are not default with LC, then user control is needed

2319569 Protect default change in bus attacker so that it does not change results unexpectedly

2318070 Tempus shows out of memory issue

2313446 report_noise -threshold not being reflected properly in the glitch report

2309701 Wrong PBA delay for PAD cell having bidi pin

2309001 accumulated_small_attacker_factor should have no influence with accumulated_small_attacker_mode current

2308365 set_si_mode -individual_glitch_simulation_mode 1 causes Cpl from PI not to combine with Prp

2307946 signoffOptDesign -drv: misleading "could not be fixed" message

2304384 The software exits without a message at create_glitch_boundary_model

2304384 Tempus exits without a message at create_glitch_boundary_model

2303761 Tempus issues in some cases

2303761 Tempus errors out in some cases

2302359 Voltage mismatch between MSV and RT/AAE due to incorrect related ground net

2302329 Port does not inherit correct voltage from set_driving_cell

2299400 In Tempus GUI ECO - using interactive ECO or timing debug - generates invalid ECO commands

2294298 set_glitch_threshold commands for non-bmod nets are being saved

2291921 Tempus issues TA-1024 ERROR even though timing_hierarchical_context_continue_on_top_block_clock_mismatch is set to true

2287435 report_slack_histogram flags IMPSYT-644 with -infile option

2279317 Tempus ECO opt_signoff -hold ends with **ERROR: (IMPSE-110): command returned bad code: 5

2275663 Stack track in create_timing_budget

2275191 CUI: opt_signoff stops in Innovus/CUI: opt_signoff got a SEGV in Innovus

2275188 Tempus ECO timing does not match with report_timing

2274123 Enhance SLBBV flow to allow different voltage specifications for clock and data

2274027 Issues with get_cells -filter "full_name"

2264247 Scope Analysis - SCOPE-2213 errors out due to incorrect netlist at a corner case in BM generation

2263678 Tempus ECO flow errors out while reading libraries

2263288 Clock buffer delay time mismatch between baseline and multi library voltage interpolation

2262796 LEF/DEF - def reader should filter out the Block Pin in PINPROPERTIES section in the DEF

2259758 Rail analysis error

2258257 Tempus errors out with update_timing with SI turned on

2257050 Modules that contain zero-pin instances get an empty module complaint because zero-pin instances are discarded by default

2256195 optDesign -drv is not fixing high fanout nets when max fanout is set using set_max_fanout

2255774 Block port's case_value is not applied to the pin connected to port in context run

2255281 Slack difference because of CPPR difference between flat and block with context on reg-out paths

2253802 IMPESI-3423 should not be applied to multi-stage cells

2253693 Enhance set_driving_cell for voltage interpolation

2253459 Tempus errors out after report_timing in some cases

2252234 Hierarchical STA: PBA incremental delay difference between flat and context runs

2249613 set_disable_timing is not working for linked library cells (LPPI libraries)

2249371 IPBA setup reporting is stuck for several hours

2246611 Issue in printing the current value of alias

2246489 Unconstrained Skew check: -through instance is not working , with -to path is reported instead of -through

2246200 Spice mode - The simulation time is too large (1.2us) for a net with clock frequency at 1GHz in Spice Deck

2245791 Errors with global timing_path_based_exhaustive_max_paths_limit

2242840 Odd time_design -expanded_views results

2242463 Skew Checks Script on Unconstrained Paths: -max_slack INFINITY returns no path exists and capturing_clk_latency is NA

2241451 Derates application is getting lost in save/restore flow in Tempus

2239599 IMPESI-3423 is printing on multi-stage cells - also preventing ROP from being performed

2238138 VH run_path_simulation SPICE deck grabs area from 1st result rather than worst glitch SPICE result and shows NaN

2237532 optDesign -PostCTS errors out

2237050 Tempus errors out in some designs

2236947 Tempus errors out while sourcing constraints after **WARN: (TCLCMD-1531): 'set_false_path' has been applied

2235477 Restoring DB takes a long time while loading the last AOCV file

2228168 Logical correlation causes significant slowdown in update_glitch

2225262 set_quiet_attacker is not being honored in 2nd iteration, even though report_noise -quiet_nets shows it quiet

2224523 High runtime for Tempus session restore when saved with UPF

2223965 report_noise -sort_by rcvr_peak is no longer working in some cases

2223760 report_timing -through <hier pin> errors out with -not_through [get_ports *]

2222121 create_cell_signal_em_model errors out with DIAG and pstack

2220186 Tempus errors out in reporting delay calculation in some cases

2220139 CCOPT creates clock opens on the pre-routed clock wires

2219493 CUI: time_design_signoff stops in some Innovus builds

2218744 Tempus errors out after command redirect 1.chk {check_timing…}

2215930 Tempus AOCV GBA mode stage count different when changed from SMSC to CMMMC

2215569 Tempus errors out for missing output_ccb definition in the input library

2214793 Stack trace during reading constraints

2209298 Tempus errors out when loading dotlibs without double quote data

2209149 TCL procedure errors out when copy-pasted in Tempus shell

2208886 report_case_analysis verbose: ERROR: (TA-115): Internal Error

2207763 Tempus errors out with constraints file with cms2sdc conversion flow

2205464 Tempus errors out in some cases

2205402 Valus error with TECHLIB-1230

2195265 WARN IMPESI-3047 is output only if DB is timed, need to be an ERROR and output in all cases

2187241 GBA and PBA reporting different timing for a path with all 1-input cells

2184757 check_timing command is reporting broken pattern (output->input->input->output) with loop option on some designs

2181322 create_spice_deck -run_path_simulation should pick the worst ROP corresponding to the worst RIP

2181282 All I/O paths are unconstrained when using the new timing context scope model

2177719 Stylus get_distributed_variables not working properly

2155484 Elaborate and improve the message IMPESI-3201 (Delay calculation failed for net) dump for different scenarios

2121432 Clock skew enabled ECO run errors out

1999024 create_spice_deck condition not matching the when condition from glitch report

1898471 Errors for range_collection command

December 2, 2020

Silicon signoff and verification (SSV) encapsulates a set of tools that address a series of electrical and physical signoff and verification steps that designers must perform on their design before tapeout. These steps report errors that require iterative and incremental fixes, also called engineering change orders (ECOs), ensuring the design integrity from an electrical and physical standpoint. All of Cadence’s signoff tools or capabilities are integrated in the Virtuoso platform, providing the same capabilities for mixed-signal and custom designs.

Knowledge and Learning

Learn about the latest Cadence offerings and solutions directly from our developers and experts. View interesting videos covering feature demos, troubleshooting information, flow launches, and more.

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world’s most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications.

Owner: Cadence

Product Name: Silicon Signoff and Verification (SSV)

Version: 20.20.000 Base Release

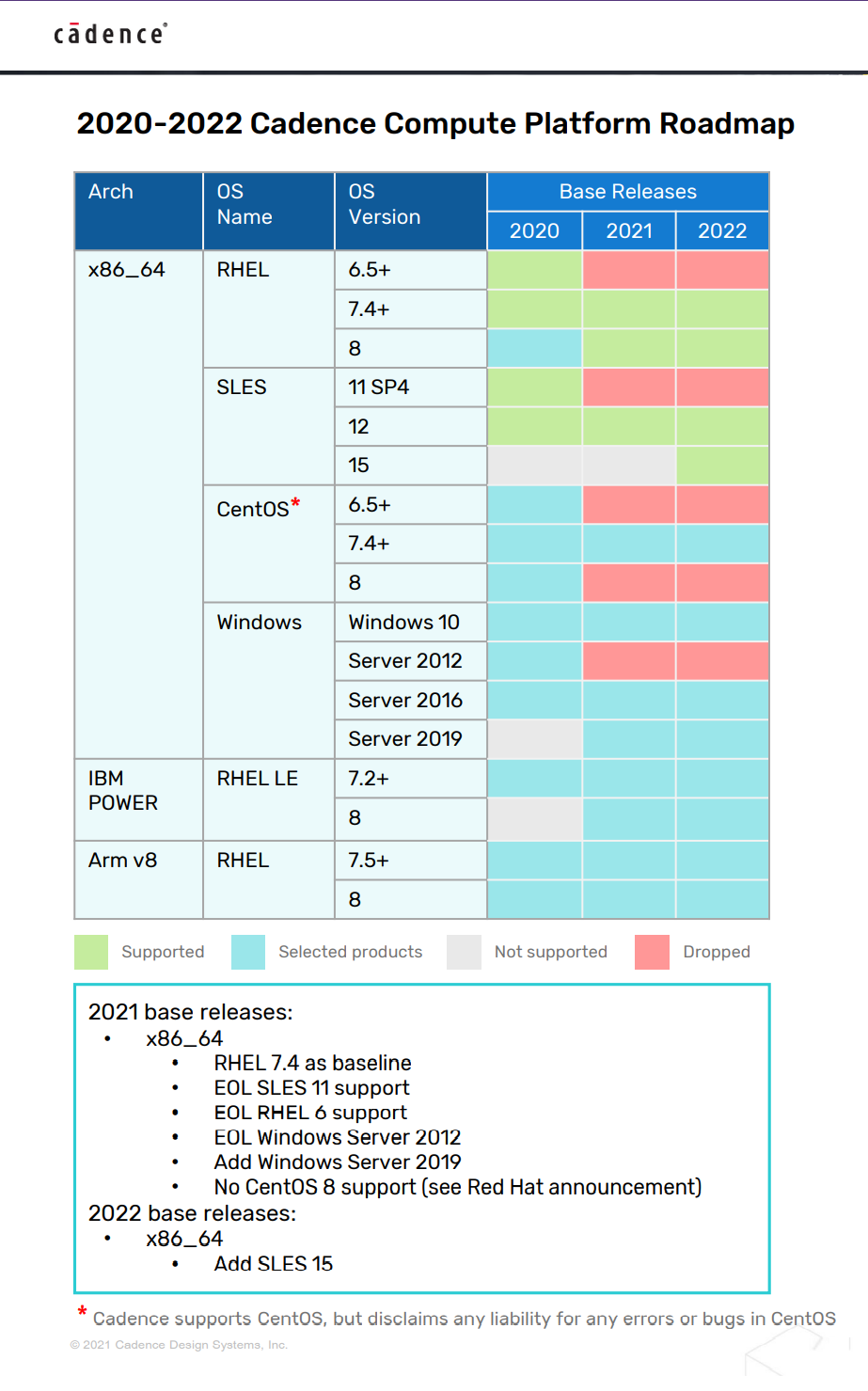

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 5.6 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please