Xilinx Vivado Design Suite 2022.1.2 | 59.4 Gb

Xilinx, Inc., the leader in adaptive and intelligent computing, is pleased to announce the availability of Xilinx Vivado Design Suite 2022.1.2 is a software suite for the design, synthesis and analysis of HDL for its line of FPGAs and SoCs.

Vivado ML Edition 2022.1.2 (Update 2) Release Highlights

This is a common updater. You do not need to re-run it for Vivado if you have already run it for Vitis and vice versa.

Vivado ML Edition 2022.1.2 adds support for the following devices:

Versal prime series:

Support for VFVC1596 Package for XCVM1402 and XCVM1302

Artix UltraScale+ FPGAs

Support for UBVA368 Package for XCAU15P and XCAU10P in Vivado ML Standard Edition

For customers using this device, AMD Xilinx recommends installing Vivado 2022.1.2 For other devices, please continue to use Vivado ML 2022.1

Vivado Design Suite is a software suite designed by Xilinx for the design, synthesis and analysis of HDL for its line of FPGAs and SoCs. Vivado Design Suite includes many tools, like Vivado, Vitis, Vitis HLS and many others.

The Vivado Design Suite offers many ways to accomplish the tasks involved in Xilinx FPGA design and verification. In addition to the traditional RTL to bitstream FPGA design flow, the Vivado Design Suite provides new system-level integration flows that focus on IP-centric design. Design analysis and verification is enabled at each stage of the flow. Design analysis features include logic simulation, I/O and clock planning, power analysis, timing analysis, design rule checking (DRC), visualization of design logic and implementation results, and programming and debugging.

The entire solution is integrated within a graphical user interface (GUI) known as the Vivado Integrated Design Environment (IDE). The Vivado IDE provides an interface to assemble, implement, and validate the design and the IP. In addition, all flows can be run using the Tcl application programming interface (API). Tcl commands can be interactively entered using the Tcl prompt or saved in a Tcl script. You can use Tcl scripts to run the entire design flow, including design analysis, or to run just part of the flow

Vivado QuickTake Tutorials

Short "How To" videos on utilizing the Xilinx Vivado Design Suite

Accelerating the development of smarter systems requires levels of automation that go beyond RTL level design. With the introduction of the Vivado Design Suite, Xilinx delivers a SoC-strength, IP-and system centric, next generation development environment that has been built from the ground up to address the productivity bottlenecks in system-level integration and implementation

Xilinx develops highly flexible and adaptive processing platforms that enable rapid innovation across a variety of technologies – from the endpoint to the edge to the cloud. Xilinx is the inventor of the FPGA, hardware programmable SoCs, and the ACAP, designed to deliver the most dynamic processor technology in the industry and enable the adaptable, intelligent, and connected world of the future

Xilinx is now part of AMD. AMD now has the industry's broadest product portfolio and a highly complementary set of technologies, reaching customers in a diverse set of markets. Together, AMD and Xilinx leverage the right engine for the right workload to address the compute needs for our customers.

Product: Xilinx Vivado Design Suite

Version: 2022.1.2 (Update 2)

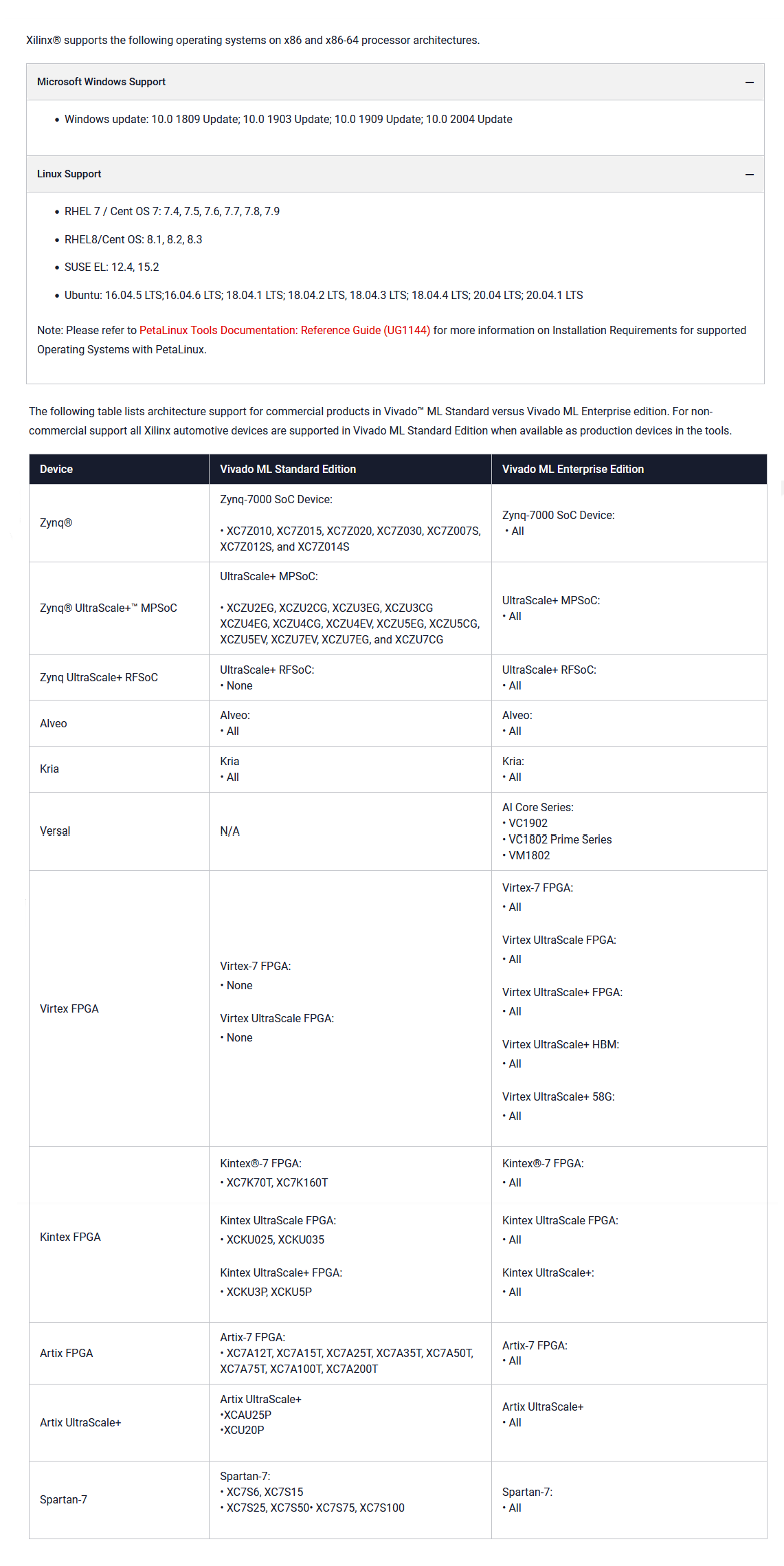

Supported Architectures: x86 and x86-64

Website Home Page : www.xilinx.com

Languages Supported: english

System Requirements: Linux *

Size: 59.4 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please