Xilinx Vitis Core Development Kit 2019.2 | 32.5 Gb

Xilinx, Inc., the leader in adaptive and intelligent computing, is pleased to announce the availability of Vitis (pronounced Vī-tis) Core Development Kit 2019.2, a unified software platform that enables a broad new range of developers – including software engineers and AI scientists – to take advantage of the power of hardware adaptability.

Vitis Core Development Kit 2019.2 - Date: Nov 12, 2019

Xilinx introduces the first release of the Vitis Unified Software Platform in 2019.2

- Unification of Xilinx SDK, SDSoC and SDAccel Development Environment into an all-in-one software platform for embedded software and application acceleration development

- Unified design methodology for Xilinx Embedded Processor Platforms and Data Center Accelerator Cards

- Vitis Core Development Kit 2019.2 Installation includes Vitis Compilers (V++), Host Compilers for ARM and x86 hosts, Vitis Analyzer

- Vitis Accelerated Libraries, Xilinx Runtime library(XRT) and Vitis Target Platforms Available as separate downloads

Hardware-Accelerated Application Development Flow

For FPGA-based acceleration, the Vitis core development kit lets you build a software application using an API, such as the OpenCL API, to run hardware (HW) kernels on accelerator cards, like the Xilinx Alveo Data Center acceleration cards. The Vitis core development kit also supports running the software application on an embedded processor platform running Linux, such as on Zynq UltraScale+ MPSoC devices. For the embedded processor platform, the Vitis core development kit execution model also uses the OpenCL API and the Linux-based Xilinx Runtime (XRT) to schedule the HW kernels and control data movement.

The Vitis core development kit tools support the Alveo U50, U200, U250, and U280 Data Center accelerator cards, as well as the zcu102_base, zcu104_base, zc702_base, and zc706_base embedded processor platforms. In addition to these off-the-shelf platforms, custom platforms are also supported.

The Vitis software platform allows you to migrate data center applications to embedded platforms. The Vitis core development kit includes the v++ compiler for the hardware kernel on all platforms, the g++ compiler for compiling the application to run on an x86 host, and an Arm® compiler for cross-compiling the application to run on the embedded processor of a Xilinx device.

Embedded Software Development Flow

The Vitis IDE is designed to be used for the development of embedded software applications targeted towards Xilinx embedded processors. The Vitis IDE works with hardware designs created with Vivado Design Suite. Embedded platforms for the hardware acceleration flow can also be used in embedded software development.

For FPGA-based acceleration, the Vitis core development kit lets you build a software application using an API, such as the OpenCL API, to run hardware (HW) kernels on accelerator cards, like the Xilinx Alveo Data Center acceleration cards. The Vitis core development kit also supports running the software application on an embedded processor platform running Linux, such as on Zynq UltraScale+ MPSoC devices. For the embedded processor platform, the Vitis core development kit execution model also uses the OpenCL API and the Linux-based Xilinx Runtime (XRT) to schedule the HW kernels and control data movement.

The Vitis core development kit tools support the Alveo U50, U200, U250, and U280 Data Center accelerator cards, as well as the zcu102_base, zcu104_base, zc702_base, and zc706_base embedded processor platforms. In addition to these off-the-shelf platforms, custom platforms are also supported.

The Vitis software platform allows you to migrate data center applications to embedded platforms. The Vitis core development kit includes the v++ compiler for the hardware kernel on all platforms, the g++ compiler for compiling the application to run on an x86 host, and an Arm® compiler for cross-compiling the application to run on the embedded processor of a Xilinx device.

Embedded Software Development Flow

The Vitis IDE is designed to be used for the development of embedded software applications targeted towards Xilinx embedded processors. The Vitis IDE works with hardware designs created with Vivado Design Suite. Embedded platforms for the hardware acceleration flow can also be used in embedded software development.

Vivado Design Suite 2019.2 - Date: Nov 12, 2019

- Introducing UVM 1.2 support in Vivado Simulator(XSIM)

- Improved layer visibility in IP Integrator

- Physical Optimization and other QoR improvement features

- 10% reduction in design compilation runtime

- New high bandwidth ICAP IP for enhancing Dynamic Function eXchange

Device Support

The following production devices are in production:

- Virtex UltraScale+ HBM:- XCVU31P, XCVU33P, XCVU35P, XCVU37P

Install and Licensing

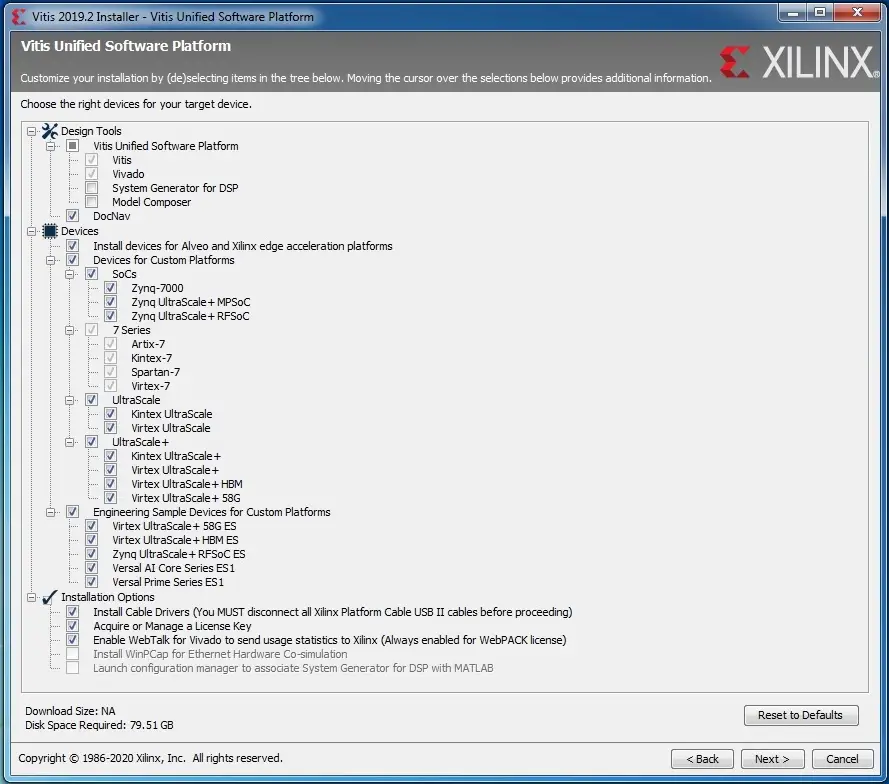

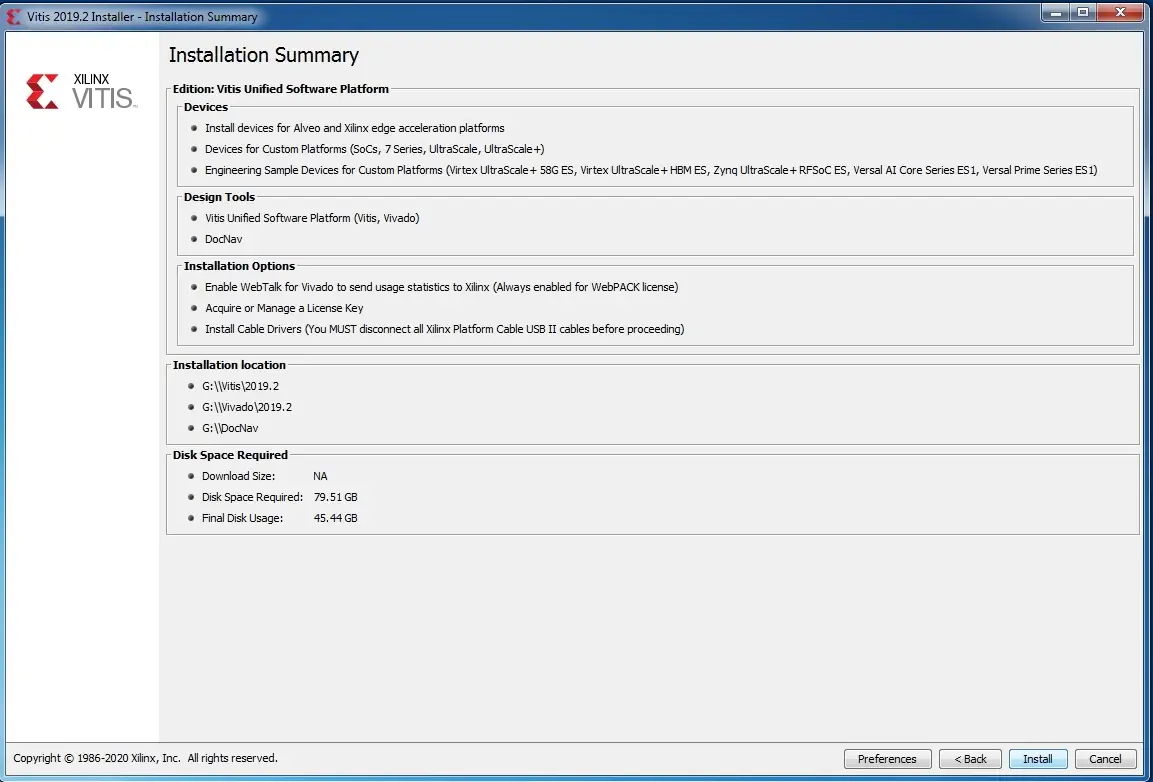

- Introducing Xilinx Unified installer for an easier install of all Xilinx tools. The single unified installer enables users to install all Xilinx tools such as Vitis, Vivado, On-premise Install for Cloud Deployments, Bootgen, Lab Edition, Hardware Server and Document Navigator.

IDE Enhancements

Next gen linter in text editor (Sigasi based)

- Improved syntax checking

- Autocompletion

- Go to definition

- Find usages

- Auto formatting / indenting

- Enabled by project settings

Model Composer

Improved Support for Vector Signal Dimensions: Improvements to code generation infrastructure to handle vector [N] signals in the design, resulting in improved performance

Constant Block Enhanced for Vector Parameters: Constant block now supports interpreting vectors parameters as 1-D, similar to corresponding Constant block in Simulink library

New Example Designs with Optimized DSP Blocks

- MRI Image Reconstruction with 2D-FFT

- Low-pass Filter design using FIR Block

- Image Smoothing filter using FIR Block

Enhancements to C/C++ Function Import: Improved error and warning messages displayed in Diagnostic Viewer, enabling better troubleshooting of issues with custom code.

Customize IP Properties for IP Catalog Export Type: Specify IP Properties including name, version and hardware description language (VHDL or Verilog) for the IP packaged from the synthesized design.

Search Capabilities in Device Chooser: Quickly search for parts and boards, based on multiple criteria, using the Device Chooser dialog on the Model Composer Hub block.

FIR Block Supports Multi-Channel Processing: Enhancements to the FIR block support processing columns in the incoming signal as independent channels of data for multi-channel filtering operations.

Supported MATLAB Versions: R2018a, R2018b, R2019a and R2019b

IP Integrator

- Versal support and block automation for GT wizard with IPs. Allows for mixing IP protocols in a GT Quad.

- Hide or color nets / blocks for better visibility in the block diagram

IP Enhancements

SmartConnect Enhancements

- New area optimization for smaller switch configurations

- LinkBlaze Topology support

- SystemC model now available

URAM Readback/Writeback IP for UltraScale+ Devices

- Solves the problem of accessing URAM data for debug

- Allows data initialization

HBICAP

- Enables embedded processors to access FPGA configuration memory through the Internal Configuration Access Port (ICAPEx)

- Gives users the ability to modify circuit functionality during operation

FIR Compiler

- Versal optimization to DSP58 new features and wider bus widths

Discrete Fourier Transform (DFT)

- Enhancements for 5G

- Support all point sizes to satisfy 38.211

- Async release to 2019.2 (EA only)

LTE Downlink Channel Encoder

- Bug fix: issue with incorrect behaviour if tvalid input de-asserted on a particular cycle resolved

Video and Imaging IPs

- MIPI DSI TX: Add 2.5Gb/s DPHY and DCS long packet support

- MIPI CSI RX: new resources optimization option by removing register interface.

- Spartan 701 MIPI CSI RX to DSI TX based application example design

- DisplayPort Subsystems: HDCP2.2 example design

- SDI Subsystems add YUV 444 support

RTL Synthesis

SystemVerilog Virtual Interface support

VHDL language support enhancements

- Support for the TIME physical type

- Faster compile times for functions

- Improved error handling

XPM_MEMORY

- Asynchronous resets on output registers of asymmetric RAMs

- Supported for both Block RAM and UltraRAM

Allow optimization of instances with MARK_DEBUG pins

- Previously treated as DONT_TOUCH

Retiming control sets of register pipelines to enable mapping to SRLs

Implementation

Dynamic Function eXchange (DFX)

Partial Reconfiguration (PR) is part of the overall DFX solution

- DFX includes silicon capabilities, Vivado design flows, Partial Reconfiguration IP and more

- Across all architectures, from 7 series through Versal

- New features to aid designers coming in future releases

- Read more on Xilinx.com

AXI High-Bandwidth ICAP interface IP

- Supports AXI read and write bursts of 256 beats per transaction

- Optional AXI4-Stream master interface for read datapath with unlimited burst per transaction

- Memory mapped AXI4 slave interface

- Supports write and read transfers up to 230 bytes in size

- Documented in PG349

Implementation Design Flow

PhysOpt is now enabled by default in Vivado Implementation Defaults strategy

New phys_opt Default directive

- Fewer optimized paths than prior releases

- Focuses on addressing timing outliers

- Very quick runtime

LUT combining optimization added to "Physical-Synthesis-in-Placer" (PSIP)

New optimization for BUFG/CE path in opt_design

- Reduces clock skew for timing closure

Design Analysis and Timing Closure

RQS Strategy Prediction

= Uses ML to predict top 3 Implementation Strategies

= report_qor_suggestions -strategy

RQA (report_qor_assessment)

= Provides guidance for using incremental compile and RQS implementation strategies

= Adds report_failfast summary to catch design issues before implementation

New congestion metric: interconnect congestion level for improved congestion visualization (Windows -> Metrics)

report_ram_utilization addition of LUTRAM reporting

New UltraFast methodologies to check for unsafe CDC between MMCMs

Incremental Compile

Incremental Implementation directives

- Quick: fastest runtime with minimal timing effort

- RuntimeOptimized: fast runtime while maintaining timing

- TimingClosure: tries to meet timing

- No need to modify place and route directives

. Tools automatically decide to run Incremental or default with original directives

Improved phys_opt_design performance in Incremental Implementation flow

- More pinpointed optimization

- Overall better P&R reuse

Incremental Synthesis: design reuse now considers changes to synth_design options

Vivado Simulator

Simulation

- Introducing UVM 1.2 support in Vivado Simulator(XSIM) to enable users to create high quality verification environment using UVM-based testbenches

The following production devices are in production:

- Virtex UltraScale+ HBM:- XCVU31P, XCVU33P, XCVU35P, XCVU37P

Install and Licensing

- Introducing Xilinx Unified installer for an easier install of all Xilinx tools. The single unified installer enables users to install all Xilinx tools such as Vitis, Vivado, On-premise Install for Cloud Deployments, Bootgen, Lab Edition, Hardware Server and Document Navigator.

IDE Enhancements

Next gen linter in text editor (Sigasi based)

- Improved syntax checking

- Autocompletion

- Go to definition

- Find usages

- Auto formatting / indenting

- Enabled by project settings

Model Composer

Improved Support for Vector Signal Dimensions: Improvements to code generation infrastructure to handle vector [N] signals in the design, resulting in improved performance

Constant Block Enhanced for Vector Parameters: Constant block now supports interpreting vectors parameters as 1-D, similar to corresponding Constant block in Simulink library

New Example Designs with Optimized DSP Blocks

- MRI Image Reconstruction with 2D-FFT

- Low-pass Filter design using FIR Block

- Image Smoothing filter using FIR Block

Enhancements to C/C++ Function Import: Improved error and warning messages displayed in Diagnostic Viewer, enabling better troubleshooting of issues with custom code.

Customize IP Properties for IP Catalog Export Type: Specify IP Properties including name, version and hardware description language (VHDL or Verilog) for the IP packaged from the synthesized design.

Search Capabilities in Device Chooser: Quickly search for parts and boards, based on multiple criteria, using the Device Chooser dialog on the Model Composer Hub block.

FIR Block Supports Multi-Channel Processing: Enhancements to the FIR block support processing columns in the incoming signal as independent channels of data for multi-channel filtering operations.

Supported MATLAB Versions: R2018a, R2018b, R2019a and R2019b

IP Integrator

- Versal support and block automation for GT wizard with IPs. Allows for mixing IP protocols in a GT Quad.

- Hide or color nets / blocks for better visibility in the block diagram

IP Enhancements

SmartConnect Enhancements

- New area optimization for smaller switch configurations

- LinkBlaze Topology support

- SystemC model now available

URAM Readback/Writeback IP for UltraScale+ Devices

- Solves the problem of accessing URAM data for debug

- Allows data initialization

HBICAP

- Enables embedded processors to access FPGA configuration memory through the Internal Configuration Access Port (ICAPEx)

- Gives users the ability to modify circuit functionality during operation

FIR Compiler

- Versal optimization to DSP58 new features and wider bus widths

Discrete Fourier Transform (DFT)

- Enhancements for 5G

- Support all point sizes to satisfy 38.211

- Async release to 2019.2 (EA only)

LTE Downlink Channel Encoder

- Bug fix: issue with incorrect behaviour if tvalid input de-asserted on a particular cycle resolved

Video and Imaging IPs

- MIPI DSI TX: Add 2.5Gb/s DPHY and DCS long packet support

- MIPI CSI RX: new resources optimization option by removing register interface.

- Spartan 701 MIPI CSI RX to DSI TX based application example design

- DisplayPort Subsystems: HDCP2.2 example design

- SDI Subsystems add YUV 444 support

RTL Synthesis

SystemVerilog Virtual Interface support

VHDL language support enhancements

- Support for the TIME physical type

- Faster compile times for functions

- Improved error handling

XPM_MEMORY

- Asynchronous resets on output registers of asymmetric RAMs

- Supported for both Block RAM and UltraRAM

Allow optimization of instances with MARK_DEBUG pins

- Previously treated as DONT_TOUCH

Retiming control sets of register pipelines to enable mapping to SRLs

Implementation

Dynamic Function eXchange (DFX)

Partial Reconfiguration (PR) is part of the overall DFX solution

- DFX includes silicon capabilities, Vivado design flows, Partial Reconfiguration IP and more

- Across all architectures, from 7 series through Versal

- New features to aid designers coming in future releases

- Read more on Xilinx.com

AXI High-Bandwidth ICAP interface IP

- Supports AXI read and write bursts of 256 beats per transaction

- Optional AXI4-Stream master interface for read datapath with unlimited burst per transaction

- Memory mapped AXI4 slave interface

- Supports write and read transfers up to 230 bytes in size

- Documented in PG349

Implementation Design Flow

PhysOpt is now enabled by default in Vivado Implementation Defaults strategy

New phys_opt Default directive

- Fewer optimized paths than prior releases

- Focuses on addressing timing outliers

- Very quick runtime

LUT combining optimization added to "Physical-Synthesis-in-Placer" (PSIP)

New optimization for BUFG/CE path in opt_design

- Reduces clock skew for timing closure

Design Analysis and Timing Closure

RQS Strategy Prediction

= Uses ML to predict top 3 Implementation Strategies

= report_qor_suggestions -strategy

RQA (report_qor_assessment)

= Provides guidance for using incremental compile and RQS implementation strategies

= Adds report_failfast summary to catch design issues before implementation

New congestion metric: interconnect congestion level for improved congestion visualization (Windows -> Metrics)

report_ram_utilization addition of LUTRAM reporting

New UltraFast methodologies to check for unsafe CDC between MMCMs

Incremental Compile

Incremental Implementation directives

- Quick: fastest runtime with minimal timing effort

- RuntimeOptimized: fast runtime while maintaining timing

- TimingClosure: tries to meet timing

- No need to modify place and route directives

. Tools automatically decide to run Incremental or default with original directives

Improved phys_opt_design performance in Incremental Implementation flow

- More pinpointed optimization

- Overall better P&R reuse

Incremental Synthesis: design reuse now considers changes to synth_design options

Vivado Simulator

Simulation

- Introducing UVM 1.2 support in Vivado Simulator(XSIM) to enable users to create high quality verification environment using UVM-based testbenches

Vitis unified software platform automatically tailors the Xilinx hardware architecture to the software or algorithmic code without the need for hardware expertise. Rather than imposing a proprietary development environment, the Vitis platform plugs into common software developer tools and utilizes a rich set of optimized open source libraries, enabling developers to focus on their algorithms.

Vitis is separate to the Vivado Design Suite, which will still be supported for those who want to program using hardware code, but Vitis can also boost the productivity of hardware developers by packaging hardware modules as software-callable functions.

The Vitis platform is built on a stack-based architecture that plugs seamlessly into open-source standard development systems and build environments, but most importantly, it includes a rich set of standard libraries.

The base layer is the Vitis target platform, which includes a board and preprogrammed I/O. The second layer, called the Vitis core development kit, encompasses the open-source Xilinx runtime library to manage the data movement between different domains, including the subsystems, the AI Engine in the forthcoming Versal ACAP, as well as an external host, if required. This layer also includes the core development tools such as compilers, analyzers and debuggers. While Xilinx provides a world-class design environment, these tools are designed to integrate seamlessly with industry-standard build systems and development environments.

In the third layer are more than 400 optimized and open-source applications across eight Vitis libraries.

These include the Vitis Basic Linear Algebra Subprograms (BLAS) library, the Vitis Solver library, the

Vitis Security library, the Vitis Vision library, the Vitis Data Compression library, the Vitis Quantitative Finance library, the Vitis Database library and the Vitis AI library. These enable software developers to call pre-accelerated functions using a standard application programming interface (API).

The base layer is the Vitis target platform, which includes a board and preprogrammed I/O. The second layer, called the Vitis core development kit, encompasses the open-source Xilinx runtime library to manage the data movement between different domains, including the subsystems, the AI Engine in the forthcoming Versal ACAP, as well as an external host, if required. This layer also includes the core development tools such as compilers, analyzers and debuggers. While Xilinx provides a world-class design environment, these tools are designed to integrate seamlessly with industry-standard build systems and development environments.

In the third layer are more than 400 optimized and open-source applications across eight Vitis libraries.

These include the Vitis Basic Linear Algebra Subprograms (BLAS) library, the Vitis Solver library, the

Vitis Security library, the Vitis Vision library, the Vitis Data Compression library, the Vitis Quantitative Finance library, the Vitis Database library and the Vitis AI library. These enable software developers to call pre-accelerated functions using a standard application programming interface (API).

The fourth and most game-changing element of the platform is Vitis AI, which integrates a domainspecific architecture (DSA). The DSA configures Xilinx hardware to be optimized and programmed using industry-leading frameworks like TensorFlow and Caffe. Vitis AI provides the tools to optimize, compress and compile trained AI models running on a Xilinx device in about one minute. It also delivers specialized APIs for deployment from edge to cloud, all with best-in-class inference performance and efficiency. Xilinx will soon be releasing another DSA, called Vitis Video, to enable video encoding directly from FFmpeg for the same, ultra-simple, highly powerful end-to-end solution. DSAs available from partner companies include Illumina, which integrates with GATK for genome analysis, and BlackLynx, which integrates with ElasticSearch for big data analytics, along with proprietary DSAs that are currently being utilized by our customers.

The new Vivado Design Suite supply design teams with the tools and methodology needed to leverage C-based design and optimized reuse, IP sub-system reuse, integration automation and accelerated design closure. When coupled with the UltraFast High-Level Productivity Design Methodology Guide, this unique combination is proven to accelerate productivity by enabling designers to work at a high level of abstraction while facilitating design reuse.

The Vivado Design Suite offers a new approach for ultra-high productivity with next generation C/C++ and IP-based design. When coupled with the new UltraFast High-Level Productivity Design Methodology Guide, users can realize a 10-15X productivity gain over traditional approaches.

Starting with Vivado 2019.1, Dynamic Function eXchange is included at within all Vivado Editions, including WebPack.

In this training you will learn, in-depth: HDL coding recommendations targeting hardware, constraint creation and validation best practices, utilization of the planning and analysis tool for physical constraints such as clock and pin planning, as well as, floorplanning for maximum performance. If you are new to Vivado or FPGA design we encourage you to review this video.

Xilinx is the inventor of the FPGA, programmable SoCs, and now, the ACAP. Our highly-flexible programmable silicon, enabled by a suite of advanced software and tools, drives rapid innovation across a wide span of industries and technologies - from consumer to cars to the cloud. Xilinx delivers the most dynamic processing technology in the industry, enabling rapid innovation with its adaptable, intelligent computing.

Product: Xilinx Vitis Core Development Kit

Version: 2019.2_1106_2127 *

Supported Architectures: x64

Website Home Page : www.xilinx.com

Language: english

System Requirements: PC / Linux **

Supported Operating Systems: **

Size: 32.5 Gb

- There will be no 2019.2 or future releases of Xilinx SDK, SDSoC and SDAccel Development Environment.

- To install, select Vitis on the Xilinx Unified Installer. Vitis installation includes Vivado Design Suite – There is no need to install Vivado separately.

- To install, select Vitis on the Xilinx Unified Installer. Vitis installation includes Vivado Design Suite – There is no need to install Vivado separately.

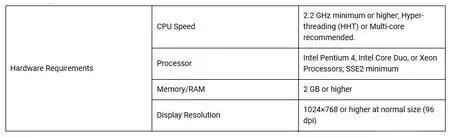

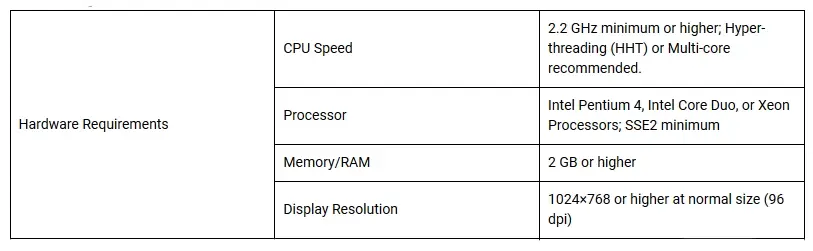

System Requirements

Supported Operating Systems

Xilinx supports the following operating systems on x86 and x86-64 processor architectures.

- Microsoft Windows 7 SP1 Professional (64-bit), English/Japanese *

- Microsoft Windows 10.0 1809 Update; 10.0 1903 Update (64-bit), English/Japanese

- Red Hat Enterprise Workstation/Server 7.4, 7.5, and 7.6 (64-bit)

- SUSE Linux Enterprise 12.4 (64-bit)

- CentOS 7.4, 7.5, and 7.6 (64-bit)

- Ubuntu Linux 16.04.5 LTS; 16.04.6 LTS; 18.04.1 LTS; 18.04.02 LTS (64-bit)

- Amazon Linux 2 LTS (64-bit)

* In alignment with Microsoft’s end of life support for Windows 7, Xilinx will also end Windows 7 support for our tools beginning with 2020.1 release.

2019.2 release of Vivado, Vitis, Model Composer & System Generator, will be the last release to support Windows 7. Beginning with 2020.1 release, Xilinx will no longer support Windows 7.

In addition to this, beginning with 2020.1, Xilinx will also drop support for 32-bit HW server tools.

Supported Operating Systems

Xilinx supports the following operating systems on x86 and x86-64 processor architectures.

- Microsoft Windows 7 SP1 Professional (64-bit), English/Japanese *

- Microsoft Windows 10.0 1809 Update; 10.0 1903 Update (64-bit), English/Japanese

- Red Hat Enterprise Workstation/Server 7.4, 7.5, and 7.6 (64-bit)

- SUSE Linux Enterprise 12.4 (64-bit)

- CentOS 7.4, 7.5, and 7.6 (64-bit)

- Ubuntu Linux 16.04.5 LTS; 16.04.6 LTS; 18.04.1 LTS; 18.04.02 LTS (64-bit)

- Amazon Linux 2 LTS (64-bit)

* In alignment with Microsoft’s end of life support for Windows 7, Xilinx will also end Windows 7 support for our tools beginning with 2020.1 release.

2019.2 release of Vivado, Vitis, Model Composer & System Generator, will be the last release to support Windows 7. Beginning with 2020.1 release, Xilinx will no longer support Windows 7.

In addition to this, beginning with 2020.1, Xilinx will also drop support for 32-bit HW server tools.

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please