Synopsys SpyGlass vQ-2020.03 SP2-3 | 16.0 Gb

Synopsys, Inc., the world leader in semiconductor design software, has unveiled Synopsys SpyGlass vQ-2020.03 SP2-3 – Early Design Analysis Tools Enable Efficient Static Verification of FPGA Designs.

SpyGlass Core

The following enhancement has been made:

- Enhanced SpyGlass by adding an option, named ignore_waiver_file_attr, to ignore the file related attributes (such as -file, -fileline, -filelineblock) in awl file/swl file or both. To enable this feature, set the following option: set_option ignore_waiver_file_attr <awl|swl|all>

Base SpyGlass

The SpyGlass lint, morelint, openmore, starc, and starc2005 products have been enhanced in this release.

SpyGlass lint

The following enhancements have been made:

- W576: Enhanced the W576 rule by adding a parameter, named ignore_conditional_expressions, which when set to yes, enables the rule to not report a violation for conditional expressions of if, generate if, for, generate for, repeat, while, wait and condopstatements.

- W240: Enhanced the W240 rule by adding a parameter, named checkfullstruct, which when set to yes, enables the rule to not report a violation for struct if at least one element of the struct is read.

- W495: Enhanced the W495 rule by adding a parameter, named check_unread parameter, which when set to yes, enables the rule to report a violation for inout ports that are not read. The default value of the check_unread parameter is set to no.

- W224: Enhanced the W224 rule by adding the report_only_from_one_hierarchy parameter which when set to yes, enables the rule to report only one violation per assignment.

- W164a, W164b: Enhanced the W164a and W164b rules to check assign pattern statements where the elements are assigned names or indexes. However, values assigned through data types and default labels are not checked due to the complexity. This feature is enabled when the check_assign_pattern parameter is set to yes.

- W164a, W164a_a, W164a_b, W164b: Enhanced the rules to perform the following when the nocheckoverflow parameter is set to nofor addition, subtraction and concatenation operators:

. W164a, W164a_a, W164a_b: The W164a, W164a_a, and W164a_b rules will not report a violation if the maximum value of the RHS expression is within the width of the LHS signal.

. W164b: The W164b rule will not report a violation if the LHS width lies in between the natural width and the LRM width.

. W164a: The W164a rule reports a violation width that will be the natural width when the LRM width of the RHS is more than the natural width.

. W164b: The W164b rule reports a violation width that will be the LRM width when the LRM width of the RHS is more than the natural width.

SpyGlass morelint

The following enhancements have been made:

- ParamValueOverride-ML: Enhanced the ParamValueOverride-ML rule to report entries related to the module only if there are overridden parameters in the module in the ParamValueOverride_Report.rptreport.

- ImproperRangeIndex-ML: Enhanced the ImproperRangeIndex-MLrule by adding a parameter, named report_loop_var_expr, which when set to yes, enables the rule to report a violation for index expressions with for loop variables by considering the maximum value of the loopvariable. The maximum value of the loop variable is determined using the initial and conditional expressions of the for loop. The rule reports a violation for the integer loop variable when both the report_loop_var_expr and ignoreInteger parameters are set to yes.

SpyGlass openmore

The following enhancement has been made:

- CombLoop: Enhanced the CombLoop rule to report mutually exclusive loops in the default flow and added a parameter, named check_loop_breakers, which when set to yes, enables the rule to not report a violation for mutually exclusive loops.

SpyGlass starc, starc2005

The following enhancements have been made:

- STARC-2.10.3.2b: Enhanced the STARC-2.10.3.2b rule to report a violation width (when the nocheckoverflow parameter is set to no for addition and subtraction operators) that will be the LRM width when the LRM width of the RHS is more than the natural width.

- STARC05-2.1.2.4: Enhanced the STARC05-2.1.2.4 rule by adding a parameter, named ignore_system_tasks, which when set to yesenables the rule to not report a violation for system tasks.

- STARC05-2.1.1.2: Enhanced the STARC05-2.1.1.2 rule by adding a parameter, named report_only_from_one_hierarchy, which when set to yes, enables the rule to report only one violation for the function, when the same function is included in different hierarchies.

SpyGlass CDC

The following enhancements have been made:

- License Changes: For all features that require the Advanced_CDC license, SpyGlass CDC now requires the following additional license key:

. cdc_adv_checker

For the RDC flow, SpyGlass CDC now requires the following additional license keys:

. cdc_adv_checker

. rdc_adv_checker

Refresh the existing license file to access the new features.

- Clock_info05, Clock_info05b: Enhanced the Clock_info05 and Clock_info05b rules by adding a constraint, named filter_clock_overlap, to specify the hierarchical nets and hierarchical pins for filtering converging clocks.

. SGDC_filter_clock_overlap01: Enhanced SpyGlass CDC by adding a rule, named SGDC_filter_clock_overlap01 to report a violation if non-existent objects are specified in the -clocks argument of the filter_clock_overlap constraint.

. SGDC_filter_clock_overlap02: Enhanced SpyGlass CDC by adding a rule, named SGDC_filter_clock_overlap02 to report a violation if non-existent objects are specified in the -conv_net argument of the filter_clock_overlap constraint.

. FilterClockOverlapSetup: Enhanced SpyGlass CDC by adding a rule, named FilterClockOverlapSetup to report cases in which the filter_clock_overlap constraint is not used to waive any of the clock_info05 / clock_info05b violations in the design.

- Clock_info05, Clock_info05b: Enhanced the Clock_info05 and Clock_info05b rules by adding a parameter, named report_unused_converging_clocks, which when set to yes, reports all the clock overlaps on a mux/gate. These clock overlaps are not used by the sequential elements and they reach another clock.

- Ac_Abstract_validation02, Ac_glitch03: In the hierarchical SoC flow, SpyGlass includes the -single_non_quasi argument in the generated abstract_port constraint if a non-quasi source is reaching the output port through a combinational logic. This enables the Ac_Abstract_validation02 and the Ac_glitch03 rules to consider such combinational paths as buffers and therefore the rules do not report a violation for such cases.

The following enhancement has been made:

- Enhanced SpyGlass by adding an option, named ignore_waiver_file_attr, to ignore the file related attributes (such as -file, -fileline, -filelineblock) in awl file/swl file or both. To enable this feature, set the following option: set_option ignore_waiver_file_attr <awl|swl|all>

Base SpyGlass

The SpyGlass lint, morelint, openmore, starc, and starc2005 products have been enhanced in this release.

SpyGlass lint

The following enhancements have been made:

- W576: Enhanced the W576 rule by adding a parameter, named ignore_conditional_expressions, which when set to yes, enables the rule to not report a violation for conditional expressions of if, generate if, for, generate for, repeat, while, wait and condopstatements.

- W240: Enhanced the W240 rule by adding a parameter, named checkfullstruct, which when set to yes, enables the rule to not report a violation for struct if at least one element of the struct is read.

- W495: Enhanced the W495 rule by adding a parameter, named check_unread parameter, which when set to yes, enables the rule to report a violation for inout ports that are not read. The default value of the check_unread parameter is set to no.

- W224: Enhanced the W224 rule by adding the report_only_from_one_hierarchy parameter which when set to yes, enables the rule to report only one violation per assignment.

- W164a, W164b: Enhanced the W164a and W164b rules to check assign pattern statements where the elements are assigned names or indexes. However, values assigned through data types and default labels are not checked due to the complexity. This feature is enabled when the check_assign_pattern parameter is set to yes.

- W164a, W164a_a, W164a_b, W164b: Enhanced the rules to perform the following when the nocheckoverflow parameter is set to nofor addition, subtraction and concatenation operators:

. W164a, W164a_a, W164a_b: The W164a, W164a_a, and W164a_b rules will not report a violation if the maximum value of the RHS expression is within the width of the LHS signal.

. W164b: The W164b rule will not report a violation if the LHS width lies in between the natural width and the LRM width.

. W164a: The W164a rule reports a violation width that will be the natural width when the LRM width of the RHS is more than the natural width.

. W164b: The W164b rule reports a violation width that will be the LRM width when the LRM width of the RHS is more than the natural width.

SpyGlass morelint

The following enhancements have been made:

- ParamValueOverride-ML: Enhanced the ParamValueOverride-ML rule to report entries related to the module only if there are overridden parameters in the module in the ParamValueOverride_Report.rptreport.

- ImproperRangeIndex-ML: Enhanced the ImproperRangeIndex-MLrule by adding a parameter, named report_loop_var_expr, which when set to yes, enables the rule to report a violation for index expressions with for loop variables by considering the maximum value of the loopvariable. The maximum value of the loop variable is determined using the initial and conditional expressions of the for loop. The rule reports a violation for the integer loop variable when both the report_loop_var_expr and ignoreInteger parameters are set to yes.

SpyGlass openmore

The following enhancement has been made:

- CombLoop: Enhanced the CombLoop rule to report mutually exclusive loops in the default flow and added a parameter, named check_loop_breakers, which when set to yes, enables the rule to not report a violation for mutually exclusive loops.

SpyGlass starc, starc2005

The following enhancements have been made:

- STARC-2.10.3.2b: Enhanced the STARC-2.10.3.2b rule to report a violation width (when the nocheckoverflow parameter is set to no for addition and subtraction operators) that will be the LRM width when the LRM width of the RHS is more than the natural width.

- STARC05-2.1.2.4: Enhanced the STARC05-2.1.2.4 rule by adding a parameter, named ignore_system_tasks, which when set to yesenables the rule to not report a violation for system tasks.

- STARC05-2.1.1.2: Enhanced the STARC05-2.1.1.2 rule by adding a parameter, named report_only_from_one_hierarchy, which when set to yes, enables the rule to report only one violation for the function, when the same function is included in different hierarchies.

SpyGlass CDC

The following enhancements have been made:

- License Changes: For all features that require the Advanced_CDC license, SpyGlass CDC now requires the following additional license key:

. cdc_adv_checker

For the RDC flow, SpyGlass CDC now requires the following additional license keys:

. cdc_adv_checker

. rdc_adv_checker

Refresh the existing license file to access the new features.

- Clock_info05, Clock_info05b: Enhanced the Clock_info05 and Clock_info05b rules by adding a constraint, named filter_clock_overlap, to specify the hierarchical nets and hierarchical pins for filtering converging clocks.

. SGDC_filter_clock_overlap01: Enhanced SpyGlass CDC by adding a rule, named SGDC_filter_clock_overlap01 to report a violation if non-existent objects are specified in the -clocks argument of the filter_clock_overlap constraint.

. SGDC_filter_clock_overlap02: Enhanced SpyGlass CDC by adding a rule, named SGDC_filter_clock_overlap02 to report a violation if non-existent objects are specified in the -conv_net argument of the filter_clock_overlap constraint.

. FilterClockOverlapSetup: Enhanced SpyGlass CDC by adding a rule, named FilterClockOverlapSetup to report cases in which the filter_clock_overlap constraint is not used to waive any of the clock_info05 / clock_info05b violations in the design.

- Clock_info05, Clock_info05b: Enhanced the Clock_info05 and Clock_info05b rules by adding a parameter, named report_unused_converging_clocks, which when set to yes, reports all the clock overlaps on a mux/gate. These clock overlaps are not used by the sequential elements and they reach another clock.

- Ac_Abstract_validation02, Ac_glitch03: In the hierarchical SoC flow, SpyGlass includes the -single_non_quasi argument in the generated abstract_port constraint if a non-quasi source is reaching the output port through a combinational logic. This enables the Ac_Abstract_validation02 and the Ac_glitch03 rules to consider such combinational paths as buffers and therefore the rules do not report a violation for such cases.

The following STARs have been fixed in this release:

3220508 How to make SpyGlass Lint report all the Structural CombLoop

3277342 Report providing for info for STX_VE_690

3282450 STX_VE_481 for v2k config file

3298999 checkfullbus does not work in W240

3304357 W123 random behavior

3313642 CombLoop is not reported but STARC-1.2.1.3

3314253 Missing ImproperRangeIndex-ML

3314967 Width mismatch is not detected with struct assignments

3315571 False violation for STARC-2.1.1.2

3318954 <SpyGlass>structure array is not checked by ImproperRangeIndex-ML

3331663 False W336 error

3339784 FalsePathSetup false violations

3340587 Provide Error message when user specifies virtual clock in format SG_VCLK_#

3357413 Getting "Assertion Failure" messages on screen when tracing

signals in Incremental Schematic

3357436 Data domain not shown in Debug Data on signal receiving side of always_comb assignment

3359896 clkname parameter regex doesn't work with brackets

3371650 cdc_false_path accepted/applied

3375484 Applying waivers from waiver editor taking long time

3376397 CombLoop missing violation

3380096 Waiver not applied for RDC run

3388184 Enhancement to ignore -file argument in AWL waivers

3389357 Missing STARC05-2.2.3.1 in SpyGlass

3389520 Inconsistency in W164b when 'logic' is used

3413282 STX reported on file when encrypted

3415924 SPG-LINT result mismatch in GUI vs moresimple rp

3420901 path_logic inferencing to be buf instead of combo with quasi sources

3425072 False ARC01 when quasi_static_rdc removes one reset at source, other source reset is same as dest reset

3426151 Waive clock_info05/clock_info05b report for exclusive relation clocks

3426157 Report clock_info05/clock_info05b when define clock at internal cell

3426210 False violation for W164a

3427410 False pass for QUASI_STATIC_SYNC_Check_mod assertion

3429652 math_real produces incorrect results with UFE

3431330 Reset_info09e rule is not running with rdc/rdc_verify_struct goal

3434369 False 362 Violation

3437615 Missing W164a with check_explicit_width parameter

3441018 Invalid entries in ParamValueOverride_Report Report

3442469 FileHdr waiver mechanism doesn't work

3448388 False violation on Ac_abstract01 rule for input-only I/O port

3452740 Usage of quasi_static -des_clk leads to false SGDC_quasi_static02 error at parent

3454281 Add disabling condition for X->1 transitions on from_rst in RFP_DYN_MARGIN_Check_mod

3455143 False violation for STARC-2.1.1.2

3455226 Crash during W146 checking

3456343 Wire referenced in assertions file before declaration

3465252 Missing violation for signal with multiple drivers

3466714 SVA instances for QUASI_STATIC_SYNC_Check_mod are creating undeclared signals which cause simulator compile errors

3467567 SpyGlass Design Read ends with SYNTH_5407 Error

3473238 SpyGlass Lint false UndrivenInterm-ML and W415 violations

3475624 The crash issue

3480600 Hierarchical RDC SoC run memory issue

3481516 SPYGLASS UFE TERMINATED WHILE Checking "W416" Rule

3482062 Crash-2 during W146 rule checking

3482118 False Combo mismatch AAV02 for quasi_static multi-bit MUX cell

3482560 Crash in dynamic goal split when further run time improvements are not available

3510297 Refinements to rdc_reduce_pessimism to address custom design cases

3514986 Crash during report generation/waiver application

3220508 How to make SpyGlass Lint report all the Structural CombLoop

3277342 Report providing for info for STX_VE_690

3282450 STX_VE_481 for v2k config file

3298999 checkfullbus does not work in W240

3304357 W123 random behavior

3313642 CombLoop is not reported but STARC-1.2.1.3

3314253 Missing ImproperRangeIndex-ML

3314967 Width mismatch is not detected with struct assignments

3315571 False violation for STARC-2.1.1.2

3318954 <SpyGlass>structure array is not checked by ImproperRangeIndex-ML

3331663 False W336 error

3339784 FalsePathSetup false violations

3340587 Provide Error message when user specifies virtual clock in format SG_VCLK_#

3357413 Getting "Assertion Failure" messages on screen when tracing

signals in Incremental Schematic

3357436 Data domain not shown in Debug Data on signal receiving side of always_comb assignment

3359896 clkname parameter regex doesn't work with brackets

3371650 cdc_false_path accepted/applied

3375484 Applying waivers from waiver editor taking long time

3376397 CombLoop missing violation

3380096 Waiver not applied for RDC run

3388184 Enhancement to ignore -file argument in AWL waivers

3389357 Missing STARC05-2.2.3.1 in SpyGlass

3389520 Inconsistency in W164b when 'logic' is used

3413282 STX reported on file when encrypted

3415924 SPG-LINT result mismatch in GUI vs moresimple rp

3420901 path_logic inferencing to be buf instead of combo with quasi sources

3425072 False ARC01 when quasi_static_rdc removes one reset at source, other source reset is same as dest reset

3426151 Waive clock_info05/clock_info05b report for exclusive relation clocks

3426157 Report clock_info05/clock_info05b when define clock at internal cell

3426210 False violation for W164a

3427410 False pass for QUASI_STATIC_SYNC_Check_mod assertion

3429652 math_real produces incorrect results with UFE

3431330 Reset_info09e rule is not running with rdc/rdc_verify_struct goal

3434369 False 362 Violation

3437615 Missing W164a with check_explicit_width parameter

3441018 Invalid entries in ParamValueOverride_Report Report

3442469 FileHdr waiver mechanism doesn't work

3448388 False violation on Ac_abstract01 rule for input-only I/O port

3452740 Usage of quasi_static -des_clk leads to false SGDC_quasi_static02 error at parent

3454281 Add disabling condition for X->1 transitions on from_rst in RFP_DYN_MARGIN_Check_mod

3455143 False violation for STARC-2.1.1.2

3455226 Crash during W146 checking

3456343 Wire referenced in assertions file before declaration

3465252 Missing violation for signal with multiple drivers

3466714 SVA instances for QUASI_STATIC_SYNC_Check_mod are creating undeclared signals which cause simulator compile errors

3467567 SpyGlass Design Read ends with SYNTH_5407 Error

3473238 SpyGlass Lint false UndrivenInterm-ML and W415 violations

3475624 The crash issue

3480600 Hierarchical RDC SoC run memory issue

3481516 SPYGLASS UFE TERMINATED WHILE Checking "W416" Rule

3482062 Crash-2 during W146 rule checking

3482118 False Combo mismatch AAV02 for quasi_static multi-bit MUX cell

3482560 Crash in dynamic goal split when further run time improvements are not available

3510297 Refinements to rdc_reduce_pessimism to address custom design cases

3514986 Crash during report generation/waiver application

The Synopsys FPGA design solution comprises high-quality, high-performance, and easy-to-use FPGA implementation, verification, and debug tools. Designers using the Synopsys FPGA design tools gain fast time-to-results for complex FPGAs, area optimization for cost and power reduction, leading HDL language support, and incremental and team design capabilities for faster FPGA design development. The Synopsys FPGA design tools provide additional value by offering DesignWare IP integration, links to high-performance functional verification with VCS , static verification for clock domain crossing analysis and lint with SpyGlass, integration with Synphony Model Compiler, and an ASIC compatible synthesis flow for FPGA-based prototyping.

The SpyGlass platform provides designers with insight about their design, early in the process at RTL using many advanced algorithms and analysis techniques. SpyGlass functions like an interactive guidance system for design engineers and managers, finding the fastest and least expensive path to implementation for complex FPGAs with both in house and third-party IP. SpyGlass Lint and CDC delivers a static verification solution to address the issues related to RTL coding best practices, design reusability and multiple asynchronous clock domain crossings (CDC) such as metastability, data re-convergence, FIFO integrity, and more.

Spyglass Quickstart

Here's how you can quickly run SpyGlass Lint checks on your design.

Synopsys, Inc. is the world leader in electronic design automation (EDA) software for semiconductor design. The company delivers technology-leading semiconductor design and verification platforms and IC manufacturing software products to the global electronics market, enabling the development and production of complex systems-on-chips (SoCs). Synopsys also provides intellectual property and design services to simplify the design process and accelerate time-to-market for its customers. Synopsys is headquartered in Mountain View, California and has offices in more than 60 locations throughout North America, Europe, Japan and Asia.

Product: Synopsys SpyGlass

Version: vQ-2020.03 SP2-3 *

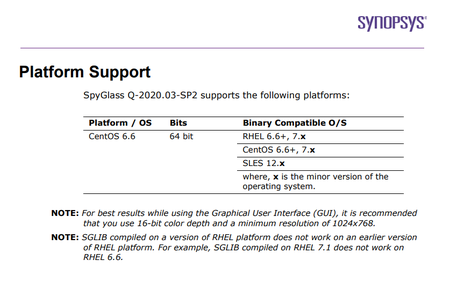

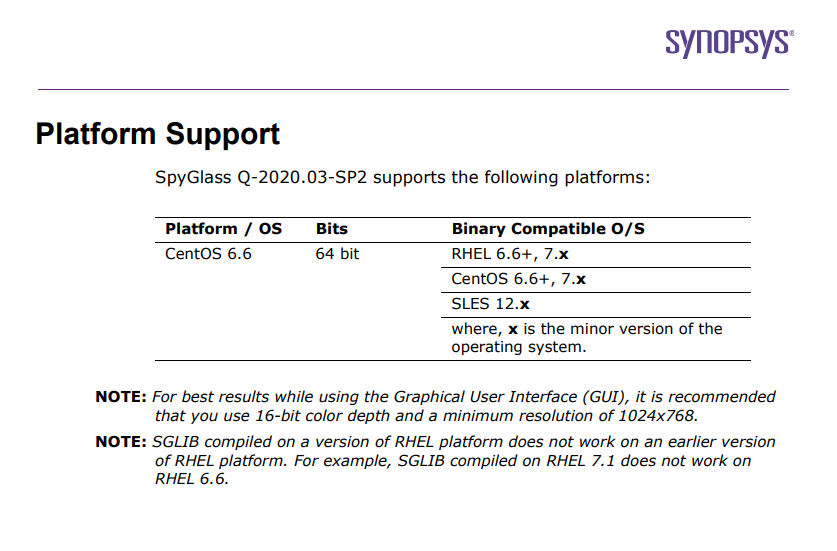

Supported Architectures: x86_x64

Website Home Page : www.synopsys.com

Languages Supported: english

System Requirements: Linux **

Size: 16.0 Gb

spyglass_vQ-2020.03-SP2-3_common.spf

spyglass_vQ-2020.03-SP2-3_docs.tar.gz

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.csh

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part00

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part01

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part02

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part03

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.README

spyglass_INSTALL_README.txt

spyglass_vQ-2020.03-SP2-3_docs.tar.gz

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.csh

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part00

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part01

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part02

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.part03

ufe_optional_spyglass-vcs_vQ-2020.03-SP2-3_common.spf.README

spyglass_INSTALL_README.txt

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please