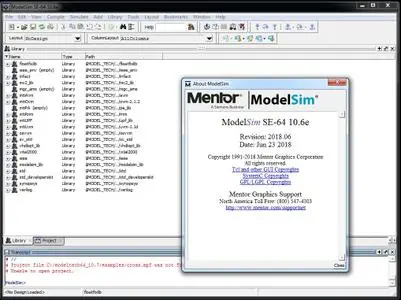

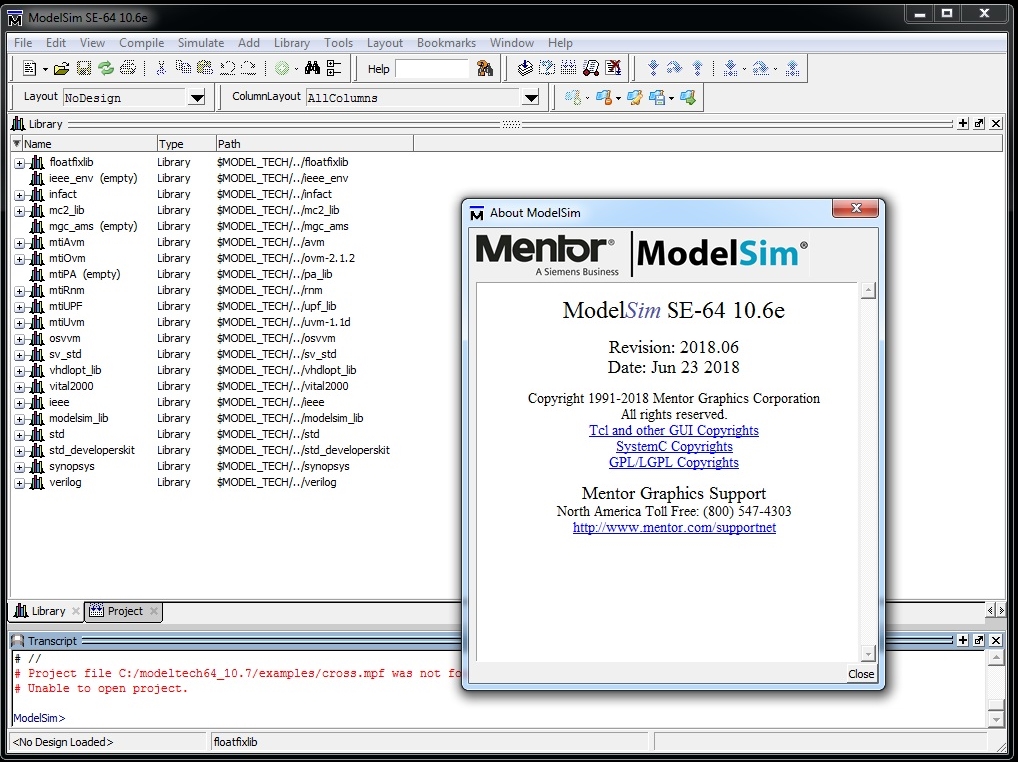

Mentor Graphics ModelSim SE-64 10.6e | 814.2 mb

Mentor, a Siemens business, has unveiled ModelSim 10.6e, is unified debug and simulation environment gives today's FPGA designers advanced capabilities in a productive work environment.

New Features Contained in this Release:

- Improved Verilog/VHDL performance and optimizations

- Improved profiling tools (option)

Compatibility Issues with Release 10.6e

SystemVerilog Compatibility

- [nodvtid] - (source) An issue with incorrect precedence in the &&& and "matches" operations in SV has been fixed. This may cause SV HDL code to be compiled differently than with previous versions. Any differences will be flagged by the compiler with an error.

- dvt110034 - (source, results) Added a SV extension vlog/vopt -svext=[+-]ifslvbefr to allow solve/before constraint within an IfElse constraint with constant condition. By default, this extension is on and no compile-time check is triggered. vlog/vopt -pedanticerrors or -svext=-ifslvbefr will revert back to the legacy behavior. A compile error (vlog-2919) will be thrown if solve/before constraint is under an IfElse constraint. When the condition expression of IfElse constraint is NOT constant, a new runtime error (vsim-16056) will be thrown, i.e.

Error: (vsim-16056) ../src/iter1b.sv(11): Illegal use of solve/before constraint in conditional/implication constraint context.

- dvt110375 - (results) In some cases simulation result differ between optimized and unoptimized cells with optimize cells selecting the wrong path delay when negative timing checks are present.

General Compatibility

- dvt94468 - (results) When using vsim -batch mode, the transcript (stdout) output could contain NUL and CR characters that are otherwise filtered out when using other vsim modes. The transcript output in -batch mode now matches the output when using -c or -i modes in this regard.

Release Announcements Compatibility

- [nodvtid] - (source, results) The -novopt command line switch will be deprecated in the next major release 10.7 following normal deprecation process:

- The -novopt switch will be accepted in 10.7 with a deprecation suppressible error message.

- In 10.8 or a subsequent release, the -novopt switch will not be accepted by the tool and cause tool to exit with error message.

- Customer scripts using this switch will have to be changed. This legacy switch forces incremental mode (pre-6.0 behavior) which is sub-optimal, and it is no longer maintained.

General Defects Repaired in 10.6e

- dvt84893 - The simulation timescale is incorrect in some circumstances when running in -batch mode.

- dvt94468 - (results) When using vsim -batch mode, the transcript (stdout) output could contain NUL and CR characters that are otherwise filtered out when using other vsim modes. The transcript output in -batch mode now matches the output when using -c or -i modes in this regard.

User Interface Defects Repaired in 10.6e

- dvt108473 - From the Message Viewer, when opening the source file referenced in a message, if the file cannot be found, a dialog box will pop up, requesting the user to select the location of the file.

- dvt106889 - "vmap" fails silently when there is a leftover lock file. Now it will report a warning 5 times, 5 seconds apart, before giving up and returning an error status.

- dvt109082 - Repaired GUI crash when associative arrays are present in automatic functions.

- dvt109387 - The Coverage HTML Report dialog box sometimes fails with an "# ** Error: (vsim-4003) Invalid option '-code '." message. This issue has been repaired.

- dvt109672 - The vsim GUI crashes when displaying certain comments in VHDL source code. This issue has been resolved.

- [nodvtid] - Enabled class instance window in view mode

SystemVerilog Defects Repaired in 10.6e

- dvt110375 - (results) In some cases simulation result differ between optimized and unoptimized cells with optimize cells selecting the wrong path delay when negative timing checks are present.

- [nodvtid] - (source) An issue with incorrect precedence in the &&& and "matches" operations in SV has been fixed. This may cause SV HDL code to be compiled differently than with previous versions. Any differences will be flagged by the compiler with an error.

VHDL Defects Repaired in 10.6e

- dvt107650 - Reference to a package constant defined within a package instance that is itself defined within a simple package could cause the compiler to produce an internal error.

- dvt108324 - The compiler could crash when encountering a composite assignment, where the left-hand side contains a variable whose type is an interface type.

- dvt109476 - The vcom compiler "-just" and "-skip" options now allow the specification 'x', which means VHDL 2008 "context" declarations.

User Interface Enhancements in 10.6e

- dvt109197 - Added PrefWave(LineWidth) preference define the width of waveform lines. The default is '1'. Defining larger widths are useful for high density monitors where a single pixel wide line is too narrow to see clearly.

SystemVerilog Enhancements in 10.6e

- dvt110034 - (source, results) Added a SV extension vlog/vopt -svext=[+-]ifslvbefr to allow solve/before constraint within an IfElse constraint with constant condition. By default, this extension is on and no compile-time check is triggered. vlog/vopt -pedanticerrors or -svext=-ifslvbefr will revert back to the legacy behavior. A compile error (vlog-2919) will be thrown if solve/before constraint is under an IfElse constraint. When the condition expression of IfElse constraint is NOT constant, a new runtime error (vsim-16056) will be thrown, i.e.

Error: (vsim-16056) ../src/iter1b.sv(11): Illegal use of solve/before constraint in conditional/implication constraint context.

SystemVerilog Compatibility

- [nodvtid] - (source) An issue with incorrect precedence in the &&& and "matches" operations in SV has been fixed. This may cause SV HDL code to be compiled differently than with previous versions. Any differences will be flagged by the compiler with an error.

- dvt110034 - (source, results) Added a SV extension vlog/vopt -svext=[+-]ifslvbefr to allow solve/before constraint within an IfElse constraint with constant condition. By default, this extension is on and no compile-time check is triggered. vlog/vopt -pedanticerrors or -svext=-ifslvbefr will revert back to the legacy behavior. A compile error (vlog-2919) will be thrown if solve/before constraint is under an IfElse constraint. When the condition expression of IfElse constraint is NOT constant, a new runtime error (vsim-16056) will be thrown, i.e.

Error: (vsim-16056) ../src/iter1b.sv(11): Illegal use of solve/before constraint in conditional/implication constraint context.

- dvt110375 - (results) In some cases simulation result differ between optimized and unoptimized cells with optimize cells selecting the wrong path delay when negative timing checks are present.

General Compatibility

- dvt94468 - (results) When using vsim -batch mode, the transcript (stdout) output could contain NUL and CR characters that are otherwise filtered out when using other vsim modes. The transcript output in -batch mode now matches the output when using -c or -i modes in this regard.

Release Announcements Compatibility

- [nodvtid] - (source, results) The -novopt command line switch will be deprecated in the next major release 10.7 following normal deprecation process:

- The -novopt switch will be accepted in 10.7 with a deprecation suppressible error message.

- In 10.8 or a subsequent release, the -novopt switch will not be accepted by the tool and cause tool to exit with error message.

- Customer scripts using this switch will have to be changed. This legacy switch forces incremental mode (pre-6.0 behavior) which is sub-optimal, and it is no longer maintained.

General Defects Repaired in 10.6e

- dvt84893 - The simulation timescale is incorrect in some circumstances when running in -batch mode.

- dvt94468 - (results) When using vsim -batch mode, the transcript (stdout) output could contain NUL and CR characters that are otherwise filtered out when using other vsim modes. The transcript output in -batch mode now matches the output when using -c or -i modes in this regard.

User Interface Defects Repaired in 10.6e

- dvt108473 - From the Message Viewer, when opening the source file referenced in a message, if the file cannot be found, a dialog box will pop up, requesting the user to select the location of the file.

- dvt106889 - "vmap" fails silently when there is a leftover lock file. Now it will report a warning 5 times, 5 seconds apart, before giving up and returning an error status.

- dvt109082 - Repaired GUI crash when associative arrays are present in automatic functions.

- dvt109387 - The Coverage HTML Report dialog box sometimes fails with an "# ** Error: (vsim-4003) Invalid option '-code '." message. This issue has been repaired.

- dvt109672 - The vsim GUI crashes when displaying certain comments in VHDL source code. This issue has been resolved.

- [nodvtid] - Enabled class instance window in view mode

SystemVerilog Defects Repaired in 10.6e

- dvt110375 - (results) In some cases simulation result differ between optimized and unoptimized cells with optimize cells selecting the wrong path delay when negative timing checks are present.

- [nodvtid] - (source) An issue with incorrect precedence in the &&& and "matches" operations in SV has been fixed. This may cause SV HDL code to be compiled differently than with previous versions. Any differences will be flagged by the compiler with an error.

VHDL Defects Repaired in 10.6e

- dvt107650 - Reference to a package constant defined within a package instance that is itself defined within a simple package could cause the compiler to produce an internal error.

- dvt108324 - The compiler could crash when encountering a composite assignment, where the left-hand side contains a variable whose type is an interface type.

- dvt109476 - The vcom compiler "-just" and "-skip" options now allow the specification 'x', which means VHDL 2008 "context" declarations.

User Interface Enhancements in 10.6e

- dvt109197 - Added PrefWave(LineWidth) preference define the width of waveform lines. The default is '1'. Defining larger widths are useful for high density monitors where a single pixel wide line is too narrow to see clearly.

SystemVerilog Enhancements in 10.6e

- dvt110034 - (source, results) Added a SV extension vlog/vopt -svext=[+-]ifslvbefr to allow solve/before constraint within an IfElse constraint with constant condition. By default, this extension is on and no compile-time check is triggered. vlog/vopt -pedanticerrors or -svext=-ifslvbefr will revert back to the legacy behavior. A compile error (vlog-2919) will be thrown if solve/before constraint is under an IfElse constraint. When the condition expression of IfElse constraint is NOT constant, a new runtime error (vsim-16056) will be thrown, i.e.

Error: (vsim-16056) ../src/iter1b.sv(11): Illegal use of solve/before constraint in conditional/implication constraint context.

About Mentor Graphics ModelSim. Modelsim HDL simulator provides FPGA customers with and easy cost-effective way to speed up FPGA development, lab bring up and test. Many FPGA designers go to the lab before adequately vetting their design. This means weeks or even months of inefficient debugging time in the lab. Testing in the lab has limited visibility of the signals in design. It can take 8 hours to do a place and route just instrument additional signals or make a small bug fix. With simulation the debug loop is much faster and there is complete visibility into the signals in the design. Simulation enables a much higher quality FPGA design before entering the lab allowing time spent during lab debug much more productive and focused.

In addition to supporting standard HDLs, ModelSim increases design quality and debug productivity. ModelSim’s award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Its architecture allows platform-independent compile with the outstanding performance of native compiled code.

The graphical user interface is powerful, consistent, and intuitive. All windows update automatically following activity in any other window. For example, selecting a design region in the Structure window automatically updates the Source, Signals, Process, and Variables windows. You can edit, recompile, and re-simulate without leaving the ModelSim environment. All user interface operations can be scripted and simulations can run in batch or interactive modes. ModelSim simulates behavioral, RTL, and gate-level code, including VHDL VITAL and Verilog gate libraries, with timing provided by the Standard Delay Format (SDF).

About Mentor Graphics. Mentor Graphics Corporation is a world leader in electronic hardware and software design solutions, providing products, consulting services and award-winning support for the worlds most successful electronic, semiconductor and systems companies. Established in 1981, the company reported revenues in the last fiscal year in excess of $1.15 billion. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Product: Mentor Graphics ModelSim

Version: SE 10.6e

Supported Architectures: x64

Website Home Page : www.mentor.com

Language: english

System Requirements: PC

Supported Operating Systems: Windows 7even or newer

Size: 814.2 mb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration and the volume for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration and the volume for the restoration

No mirrors please