Intel Quartus Prime Professional Edition 25.1.0 (129) | 82.8 Gb

Altera, now part of intel, has released Quartus Prime Pro 25.1, which supports the newest Agilex family, Agilex 3. This update equips developers with advanced tools for building high-performance, power-efficient edge and embedded applications.

Quartus Prime Pro 25.1 delivers major improvements across Agilex 3 support, debugging tools, AI acceleration, IP cores, and overall usability. Whether you're optimizing for high-speed interfaces, AI workloads, or embedded applications, this release enhances performance, efficiency, and flexibility.

What' new in Quartus Prime Pro Edition Software Version 25.1

Quartus Prime Pro Edition Software Version 25.1 includes the following new features and enhancements:

Quartus Prime Pro Edition Software Version 25.1 includes the following new features and enhancements:

- Introduced device support for Agilex 3 C-Series devices.

- Added device support for additional Agilex 5 E-Series devices.

- Added device support for additional Agilex 7 F-Series and I-Series devices.

- Enhanced Nios V processors as follows:

. Enhanced Nios V/g processor with beta implementation of RISC-V Core Local Interrupt Controller (CLIC).

. Enhanced Nios V/gprocessor with beta implementation of Shadow Register.

. Reduced resource utilization of Nios V/c cores.

- Reduced memory required for device modeling.

- The Programming File Generator now provides a checksum value for the SOF file. Use this value to ensure that you use the correct SOF file. For example, you can compare the checksums in the RBF and SOF files to confirm they are same.

- Enabled debugging over a streaming interface, including Signal Tap debugging over a streaming interface.

- Added Functional Safety Separation Design Flow.

- Enhanced Advanced Link Analyzer as follows:

. Added support support for Agilex 3 C-Series devices.

. Improved F-Tile support.

- The IP Catalog provides a new icon to indicate whether an IP has a corresponding. Example Design that you can generate.

Comprehensive Support for Agilex 3 FPGAs

The Agilex 3 FPGA family brings high performance, power efficiency, and cost optimization to edge and embedded applications. With this release you can design, test, and deploy solutions more effectively utilizing the Agilex 3 higher-speed transceivers for improved connectivity, on-chip dual Cortex-A55 ARM cores, adding powerful processing capabilities, and expanded memory support, including LPDDR4.

For applications where board space is limited, Agilex 3 utilizes Intel’s variable pitch BGA packaging to enable more compact and efficient designs. This technology allows developers to fit more functionality into smaller footprints while maintaining performance and power efficiency.

Security is essential for protecting intellectual property and sensitive data in FPGA applications. Agilex 3 includes new features that strengthen encryption, authentication, and physical security, making designs more resilient to tampering and attacks.

Nios V Soft Processor Enhancements

The Nios V plays a crucial role in embedded applications, and this release brings performance and efficiency improvements. These updates enable developers to build more compact, higher-performing embedded systems.

- Nios V/g Core Performance Boost –Improved task execution efficiency and optimized overall performance

- Nios V/c Core Area Reduction – Achieves an 8% area reduction, making designs more compact.

- Ashling RISCFree IDE VS Code Extension – Provides a Visual Studio Code extension for streamlined Nios® V software development using Ashling RiscFree IDE.

- TinyML Example Design using Nios V Application Note – Enables developers to integrate machine learning (ML) capabilities into FPGA designs using microcontrollers

Embedded Software Features

FPGA-based embedded applications require robust OS and virtualization support. Quartus Prime Pro 25.1 expands compatibility for Linux, RTOS, and hypervisors, allowing developers to create scalable, real-time, and virtualized embedded solutions.

- Linux Hardware Reference Designs – Standard and regular editions for seamless Linux development.

- Xen Hypervisor Support – Allows developers to build virtualized environments for FPGA applications.

- RTOS Support – Supports Zephyr and Bare Metal, with FreeRTOS coming in Q2 (May release).

Installer Improvements: Faster, More Flexible Setup

Installing FPGA software should be efficient and customizable. Quartus Prime Pro 25.1 improves the installation experience with parallel processing, flexible component selection, and better file management.

- Parallel Installation – Reduces setup time by allowing multiple components to install simultaneously.

- Dynamic Component Selection – Lets users choose only the components they need, optimizing disk space and installation time.

Streaming Debug: High-Speed Hardware Debugging

Effective debugging is key to reducing development cycles. The Streaming Debug IP for Signal Tap provides real-time, high-bandwidth data capture, improving how developers analyze and troubleshoot FPGA designs.

- High-Speed Streaming for Hardware Debugging – Enables efficient data transfer for real-time analysis.

- Configurable Streaming via STP – Use Signal Tap Logic Analyzer (STP) to configure the streaming method and select the appropriate debug host.

Simulation Improvements

Quartus Prime Pro 25.1 introduces new native Altera AXI4 Bus Functional Models (BFMs), delivering improved simulation performance, integration, and long-term support.

- Native Altera AXI4 BFMs – Optimized for Quartus simulation workflows, ensuring better compatibility and performance.

- Seamless Transition – Users can switch to the new Altera AXI4 BFMs without significant modifications, benefiting from tighter toolchain integration.

Quartus Prime Pro 25.1 brings significant simulation performance improvements, particularly for transceiver protocol IP, leading to faster and more efficient debugging and verification.

- Improved Transceiver Protocol IP Simulation – Enhances support for PCIe, Ethernet, Serial Lite, JESD, and other transceiver protocols.

- Beta Models in 25.1 – The new simulation models are in Beta for this release, with a focus on Ethernet and PCIe.

- Enhanced Performance – Improvements of up to 50% or more are typical, reducing simulation time and accelerating verification.

These simulation updates make Quartus Prime Pro 25.1 a more powerful tool for transceiver-based FPGA designs by delivering faster, more efficient simulations and reducing overall verification time.

The Agilex 3 FPGA family brings high performance, power efficiency, and cost optimization to edge and embedded applications. With this release you can design, test, and deploy solutions more effectively utilizing the Agilex 3 higher-speed transceivers for improved connectivity, on-chip dual Cortex-A55 ARM cores, adding powerful processing capabilities, and expanded memory support, including LPDDR4.

For applications where board space is limited, Agilex 3 utilizes Intel’s variable pitch BGA packaging to enable more compact and efficient designs. This technology allows developers to fit more functionality into smaller footprints while maintaining performance and power efficiency.

Security is essential for protecting intellectual property and sensitive data in FPGA applications. Agilex 3 includes new features that strengthen encryption, authentication, and physical security, making designs more resilient to tampering and attacks.

Nios V Soft Processor Enhancements

The Nios V plays a crucial role in embedded applications, and this release brings performance and efficiency improvements. These updates enable developers to build more compact, higher-performing embedded systems.

- Nios V/g Core Performance Boost –Improved task execution efficiency and optimized overall performance

- Nios V/c Core Area Reduction – Achieves an 8% area reduction, making designs more compact.

- Ashling RISCFree IDE VS Code Extension – Provides a Visual Studio Code extension for streamlined Nios® V software development using Ashling RiscFree IDE.

- TinyML Example Design using Nios V Application Note – Enables developers to integrate machine learning (ML) capabilities into FPGA designs using microcontrollers

Embedded Software Features

FPGA-based embedded applications require robust OS and virtualization support. Quartus Prime Pro 25.1 expands compatibility for Linux, RTOS, and hypervisors, allowing developers to create scalable, real-time, and virtualized embedded solutions.

- Linux Hardware Reference Designs – Standard and regular editions for seamless Linux development.

- Xen Hypervisor Support – Allows developers to build virtualized environments for FPGA applications.

- RTOS Support – Supports Zephyr and Bare Metal, with FreeRTOS coming in Q2 (May release).

Installer Improvements: Faster, More Flexible Setup

Installing FPGA software should be efficient and customizable. Quartus Prime Pro 25.1 improves the installation experience with parallel processing, flexible component selection, and better file management.

- Parallel Installation – Reduces setup time by allowing multiple components to install simultaneously.

- Dynamic Component Selection – Lets users choose only the components they need, optimizing disk space and installation time.

Streaming Debug: High-Speed Hardware Debugging

Effective debugging is key to reducing development cycles. The Streaming Debug IP for Signal Tap provides real-time, high-bandwidth data capture, improving how developers analyze and troubleshoot FPGA designs.

- High-Speed Streaming for Hardware Debugging – Enables efficient data transfer for real-time analysis.

- Configurable Streaming via STP – Use Signal Tap Logic Analyzer (STP) to configure the streaming method and select the appropriate debug host.

Simulation Improvements

Quartus Prime Pro 25.1 introduces new native Altera AXI4 Bus Functional Models (BFMs), delivering improved simulation performance, integration, and long-term support.

- Native Altera AXI4 BFMs – Optimized for Quartus simulation workflows, ensuring better compatibility and performance.

- Seamless Transition – Users can switch to the new Altera AXI4 BFMs without significant modifications, benefiting from tighter toolchain integration.

Quartus Prime Pro 25.1 brings significant simulation performance improvements, particularly for transceiver protocol IP, leading to faster and more efficient debugging and verification.

- Improved Transceiver Protocol IP Simulation – Enhances support for PCIe, Ethernet, Serial Lite, JESD, and other transceiver protocols.

- Beta Models in 25.1 – The new simulation models are in Beta for this release, with a focus on Ethernet and PCIe.

- Enhanced Performance – Improvements of up to 50% or more are typical, reducing simulation time and accelerating verification.

These simulation updates make Quartus Prime Pro 25.1 a more powerful tool for transceiver-based FPGA designs by delivering faster, more efficient simulations and reducing overall verification time.

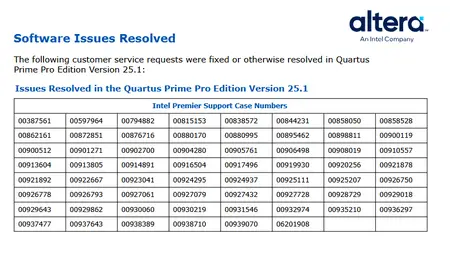

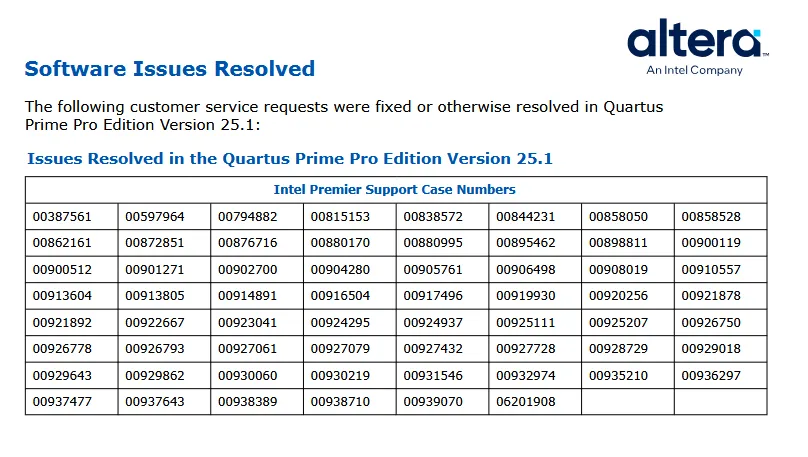

Quartus Prime Pro Edition Software Version 25.1 also include bug fixes.

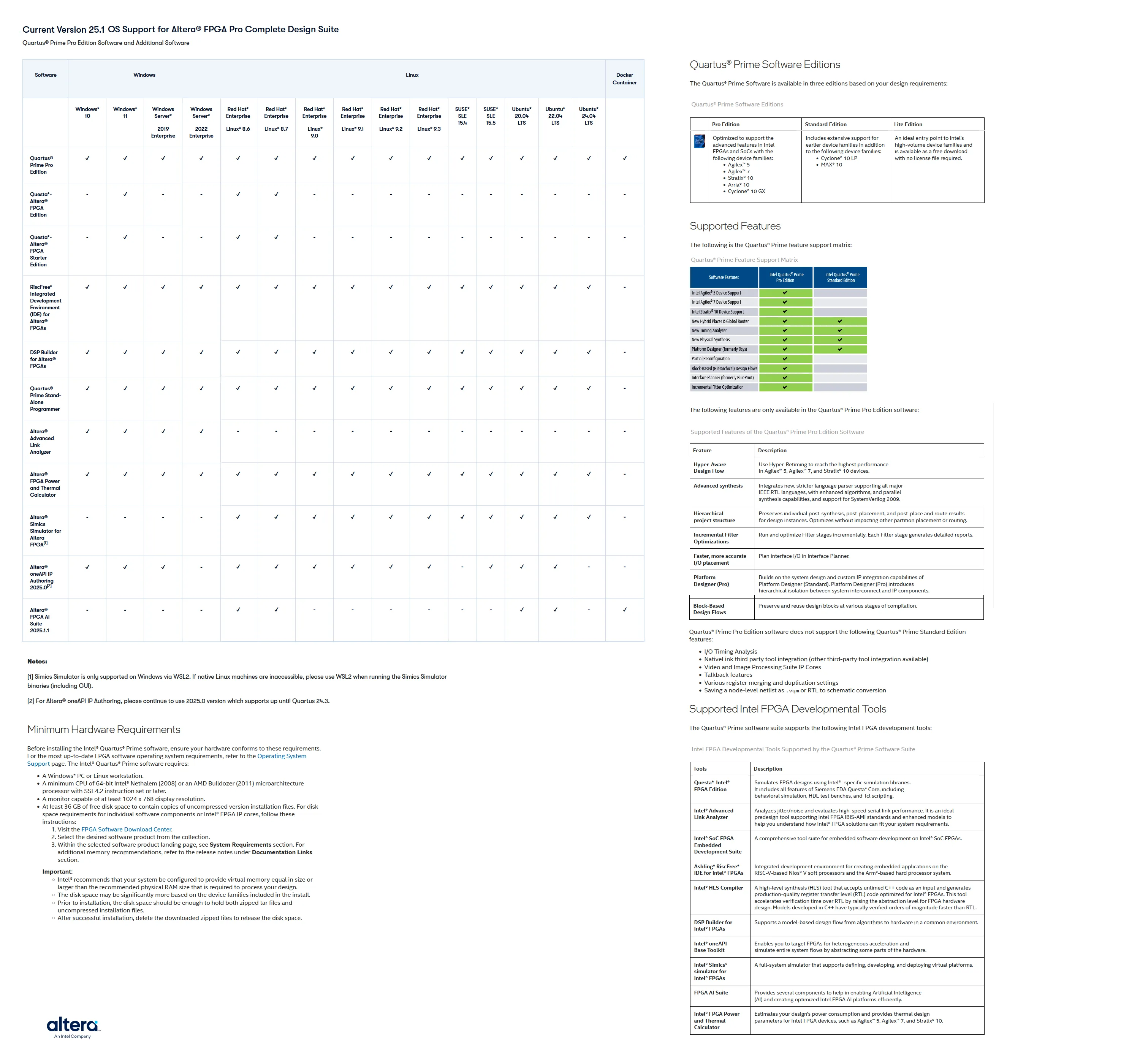

Altera Quartus Prime Design Software supports the latest Agilex 3, Agilex 7 and Agilex 5 FPGA and SoC families, ensuring a seamless development experience for cutting-edge applications. Also introduces concurrent analysis support, enabling designers to analyze results timing, netlist views, and compilation reports while compilation is still running. Partial Reconfiguration (PR) allows dynamic updates to sections of the FPGA; at the same time the rest of the design continues to function, and the Design Assistant helps catch potential design issues early by providing real-time guidance and recommendations, improving overall design quality and efficiency. Additionally, designers can leverage cloud-based Quartus' FPGA programming tools, available in Dockers containers, for high-performance application acceleration in a cloud computing environment.

Introduction to Platform Designer

The Platform Designer system integration tool saves design time and improves productivity by automatically generating interconnect logic to connect intellectual property (IP) functions and subsystems. In this training, you will receive an introduction to system design and get an overview of the Platform Designer system integration tool and its key features in the Intel Quartus Prime software. You will learn about the benefits of using standard interfaces in your FPGA design process and about the custom-generated, Network-on-a-Chip based, high-performance interconnect created to link these interfaces together.

Intel is a world leader in computing innovation. The company designs and builds the essential technologies that serve as the foundation for the world’s computing devices. Altera was originally a chip manufacturing company that was acquired by Intel in 2015 for $16.7 billion and merged into the company’s data center unit under the Programmable Solutions Group (PSG) brand.

Owner: Intel

Product Name: Altera Quartus Prime

Version: Pro Edition 25.1.0 (129)

Supported Architectures: x64

Website Home Page : www.altera.com

Languages Supported: english

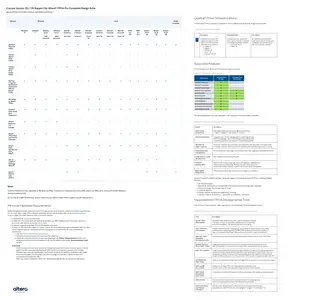

System Requirements: Windows *

Size: 82.8 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please