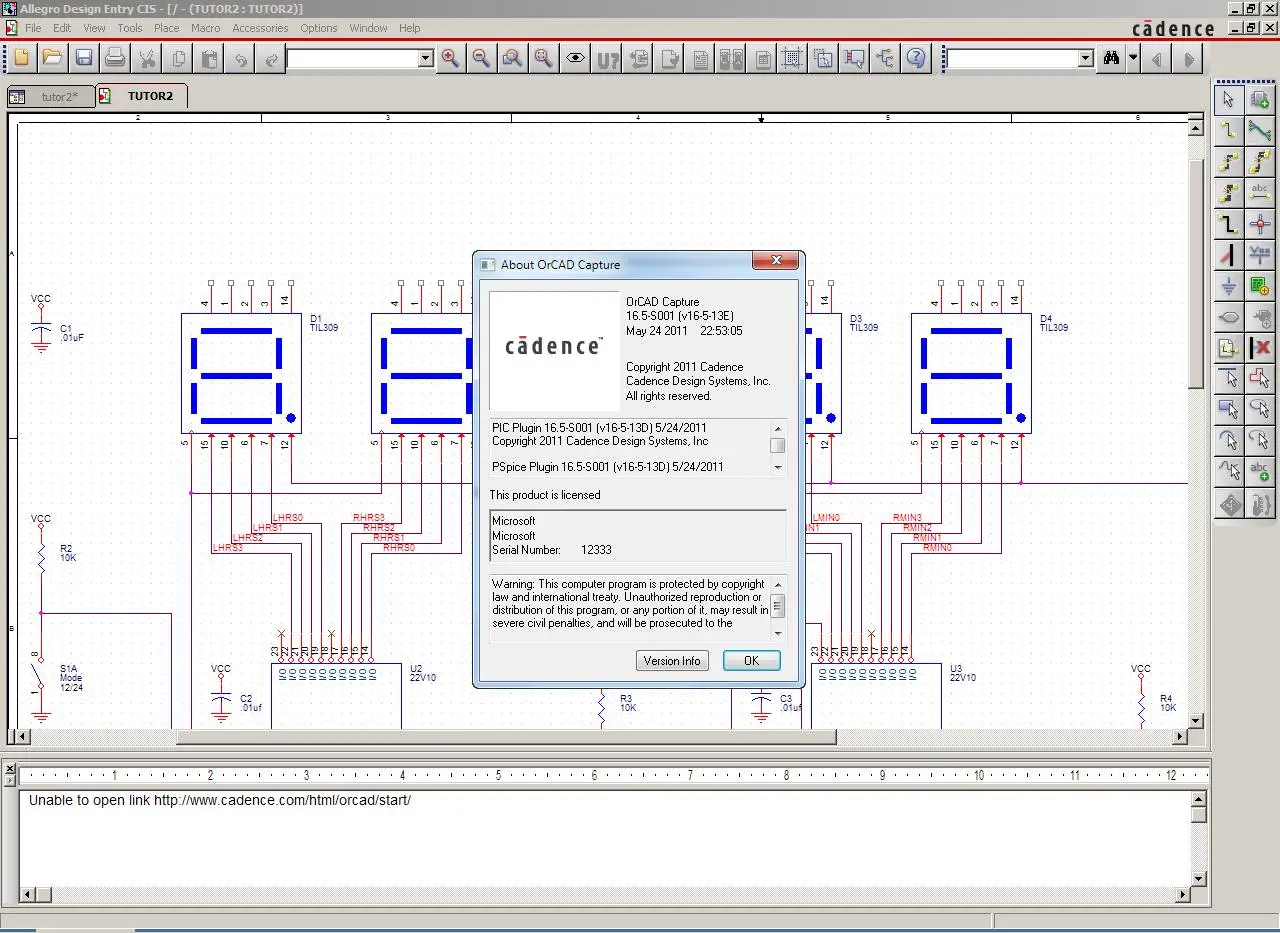

Cadence SPB/OrCAD 16.5.00(1)2 (Allegro SPB) Hotfix | 736.5 mb

Cadence OrCAD SPB design suites combine industry-leading, production-proven, and highly scalable SPB design applications to deliver complete schematic entry, simulation, and place-and-route solutions. With these powerful, intuitive tools that integrate seamlessly across the entire SPB design flow, engineers can quickly move products from conception to final output.

Company Profile

To keep pace with market demand for more performance and functionality in today’s mobile phones, digital cameras, computers, automotive systems and other electronics products, manufacturers pack billions of transistors onto a single chip. This massive integration parallels the shift to ever-smaller process geometries, where the chip’s transistors and other physical features can be smaller than the wavelength of light used to print them.

Designing and manufacturing semiconductor devices with such phenomenal scale, complexity and technological challenges would not be possible without electronic design automation (EDA). It is essential for everything from verifying that the myriad transistors do what the designer intended to dealing with physical effects on electrons traveling miles of wires with widths sometimes measuring less than 100 nanometers.

Cadence Design Systems is the world's leading EDA company. Cadence customers use our software, hardware, and services to overcome a range of technical and economic hurdles.

New Allegro 16.5 Technology

The latest Allegro technology will be available through flexible on-demand product configurations that offer cost-efficiency and scalability. Allegro 16.5 spans silicon, SoC, and system-level development and offers SPB designers benefits such as:

- Higher functional density with a constraint-driven flow for embedded components

- Faster timing closure with new SPB interconnect design planning technology

- Fewer physical prototype iterations with concurrent team design authoring

- More efficient low-power design with integrated power delivery network analysis

- A compliant and faster implementation path with package/board-aware SoC IP

- Smoother collaboration among global teams with new SiP distributed co-design

- Flexibility through “base plus options” configurations

DATE: 07-24-2011 HOTFIX VERSION: 002

===================================================================================================================================

CCRID PRODUCT PRODUCTLEVEL2 TITLE

===================================================================================================================================

527444 ALLEGRO_EDITOR EDIT_ETCH Slide command needs to be enhanced for same net spacings

583257 ALLEGRO_EDITOR EDIT_ETCH Add Connect and slide command needs to be enhanced for same net spacings.

592956 ALLEGRO_EDITOR EDIT_ETCH Same net traces will not push and/or shove each other.

745285 ALLEGRO_EDITOR EDIT_ETCH Requesting a true "shove" in Route > Slide for Same net routing.

773503 CAPTURE OTHER Doing "Mirror Horizontally" creates extra un-connects or extra junction dots in Capture V16.3.

774270 F2B PACKAGERXL Require to ignore space in Pattern setting to prevent duplicated Refdes.

799984 ALLEGRO_EDITOR INTERACTIV Enhance the Fix command to select just cline segs

809008 CAPTURE SCHEMATIC_EDITOR New nodes get appeared within the design when we select the design and do "Mirror Horizontally".

810058 CAPTURE SCHEMATIC_EDITOR New nodes get appeared within the design when we select the design and do "Mirror Horizontally".

821133 ALLEGRO_EDITOR MANUFACT Output artwork for pad data that are suppressed unconnected pads with Gerber 6x00 format

831710 CAPTURE SCHEMATIC_EDITOR Capture adds extra junctions to design by itself

842410 ALLEGRO_EDITOR EDIT_ETCH Ability to slide with "Shove" for "Same Net" segments/vias.

854971 ALLEGRO_EDITOR INTERACTIV Capability to add cline segment in a temp group

860772 ADW PCBCACHE Save Shopping Cart (pcbcache) is crashing component browser

867842 CAPTURE PROJECT_MANAGER Capture crash with 'Open File Location"

868306 CAPTURE CONNECTIVITY mirror vertically removes junction creates extra nets

882677 EMI RULE_CHECK bypass_plane_split fail if BYPASS_XXXX_EFFECT_DISTANCE

891439 ALLEGRO_EDITOR INTERACTIV moving cline segments

893544 ALLEGRO_EDITOR INTERFACES IPC-D-356A netlist issue with BB vias.

893765 ALLEGRO_EDITOR PARTITION Mail command not sending out email on Linux platforms.

894390 SIP_LAYOUT EXPORT_DATA Generate all balls in the xml file for export to EDI's readPackage command

895933 APD DATABASE Update Symbol shifts the center of the Dynamic Fillet and creating DRCs

896598 ALLEGRO_EDITOR PLACEMENT error message is misleading

897196 CIS LINK_DATABASE_PA Schematic Contents are not shown in CIS window while link Dbase part for parts placed from library

898598 ALLEGRO_EDITOR MENTOR Negative planes from Mentor Board Station not being translated.

899556 ALLEGRO_EDITOR ARTWORK Import artwork seems not to work correctly.

900501 ALLEGRO_EDITOR PLACEMENT "Place Replicate Apply" is showing lot of DRC's during placement of replicated circuit in 16.5

901141 CIS EXPLORER Japanese character appear garbled in CIS explorer window.

901666 CAPTURE OTHER Home page of Flowcad-Switzerland and Flowcal-Poland is not preserved on captre restart on start page

902066 ALLEGRO_EDITOR DRC_CONSTR Shape in Region not follow the constrains

902349 CAPTURE LIBRARY Capture crashes while closing library

902508 F2B PACKAGERXL SPB16.5 Packager-XL consumes much more memory than 16.3

902841 CAPTURE GENERAL Capture Start page does not show

902876 F2B PACKAGERXL Packager fails on the design upreved in 16.5

902959 CONCEPT_HDL HDLDIRECT HDLDirect Error while saving design

903171 PSPICE NETLISTER Why Capture is treating hierarchical power ports as floting nets in complex heirarchy designs?

903713 ALLEGRO_EDITOR PARTITION Placement Replication do not work fine in the Design Partition

903799 SIP_LAYOUT DIE_EDITOR Disappear die pins after exiting co-design die editor

904021 ALLEGRO_EDITOR OTHER Export PDF from SPB 16.5 produces a file not text searchable

904339 CONCEPT_HDL CORE new design crashes using the attached CDS_SITE

904522 F2B PACKAGERXL Part will not package in 16.5 but packages in 16.3

904764 APD OTHER Enhance Scale Factor of Stream Out to support 4 decimal places

904771 ALLEGRO_EDITOR MANUFACT Pin Number display issue.

904853 ALLEGRO_EDITOR GRAPHICS Enhancement for showing Static shape as it was seen in 16.3

905144 CONSTRAINT_MGR ECS_APPLY Min Line Spacing is larger than Primary or Neck Gap less(-) Tolerance but No Warning in CM

905314 F2B PACKAGERXL Import physical causes csb corruption

905337 CONCEPT_HDL CORE ConceptHDL crashes after Import Design process.

905533 ALLEGRO_EDITOR INTERACTIV Pin numbers for components on BOTTOM Side are moved in Preselect mode,when the BOTTOM layer is invisible

905796 CONCEPT_HDL CONSTRAINT_MGR Fujitsu CM issue inaccurate concept2cm diff pair issues

905811 CAPTURE EE_INTERSHEET_RE interesheet references in the form of grid grid page number instead of page number grid

906118 CONCEPT_HDL CONSTRAINT_MGR Cannot open CM if SIGNAL_MODEL value was not assigned in ptf.

906153 ALLEGRO_EDITOR SCRIPTS Unable to run allegro script in batch mode on the attached board.

906182 APD EXPORT_DATA Modify Board Level Component Output format

906200 ALLEGRO_EDITOR DFA Enh- DFA drc invoked in Batch mode returns false constraint value in Show Element

906517 PSPICE PROBE PSpice new cursor window shows incorrect result.

906627 ADW COMPONENT_BROWSE ppt options are not read if ucb is launched from FM. works fine if launched from dehdl.

906647 SIG_INTEGRITY LIBRARY lib_dist creates a signoise.log in current directory (with backup files like ,1 ,2 etc.) on each run

906673 F2B PACKAGERXL Ignore the signal model validity check during packaging

906688 ADW LRM A copy of source design gets created in worklib of target design after 'Import Design'

906750 ALLEGRO_EDITOR PARTITION Importing design partition removes the testpoint reference designation

906874 PSPICE NETLISTER Error less than 2 connections for unconnected hierarchical pin

907095 F2B OTHER Part Manager does not show Error as Undefined when directive ptf_mismatch_exclude_inj_prop is used

907424 ALLEGRO_EDITOR GRAPHICS Allegro add option for pre 16.5 shape display

907490 CAPTURE NETLIST_LAYOUT 16.5 Layout netlist is not correct. It differs form 16.3 layout netlist.

907884 SIP_LAYOUT MANUFACTURING Need to add an "NC" pin text option for "Manufacturing Documentation Display Pin Text"

907885 SIG_INTEGRITY OTHER Matchgroup targets lost when importing netlist to Allegro layout in HF31

907929 CAPTURE TCL_SAMPLE TCL command to delete a property from parts in a library is not working correctly

907933 SIG_INTEGRITY OTHER Single line impedence not working in OrCad PCB Professional

907963 CONCEPT_HDL CORE Design uprev issue when moving from 16.2 to 16.5

908000 SIG_INTEGRITY OTHER Inconsistence z-axis delay reported on Tpoint when define at via location.

908057 CONCEPT_HDL CORE DE HDL crash with the cut and paste of a signal name

908060 CONCEPT_HDL CORE CTRL+LMB Option not working correctly in 16.3

908210 CAPTURE CONNECTIVITY Connection is being lost while dragging a component

908241 CAPTURE DRC DRC error column is blank in DRC markers window in 16.5

908339 RF_PCB BE_IFF_IMPORT mechanical holes VIAFC are not at the right place

908534 SIP_LAYOUT SYMB_EDIT_APPMOD issues with symbol editor and copying pin arrays

908535 F2B DESIGNVARI When I try to view my variant file the variant editor crashes

908595 APD 3D_VIEWER Cadence Design 3D viewer" screen pops up and is all black because the colors have all converted to b

908849 CAPTURE ANNOTATE Getting crash while annotating the attached design

908874 CONCEPT_HDL CORE Part Manager - No Part Found error when using CCR# 775788 feature

909077 CONCEPT_HDL CORE After packaging pin numbers remains invisible even when $PN

909104 ALLEGRO_EDITOR SYMBOL Warning message needs to be modified. It does not save the symbol and also not tell the actual problem.

909417 ALLEGRO_EDITOR REPORTS "report -v upc" returns 'Segmentation fault' on Linux

909635 SIP_LAYOUT DIE_STACK_EDITOR Add Interposer crashes in SiP Layout

909749 ALLEGRO_EDITOR MANUFACT Allegro Crash during dimensioning

909760 SIP_LAYOUT MANUFACTURING Create bond finger solder mask doesn't follow the mask opening as defined in the padstack

909861 F2B PACKAGERXL NetAssembler broken within the latest 16.30.031

910006 CONCEPT_HDL INFRA Motorola design fails to uprev from 16.3 to 16.5, xcon file is getting corrupted.

910141 CAPTURE NETGROUPS Modify NetGroup definition does not update Offpage Connector

910340 ADW LRM Import design in schematic, only 1 page import, the entire block is getting imported.

910678 SIG_INTEGRITY OTHER The Analyze> Model Assignment> Auto setup is not creating/assigning models to discrete components in 16.5

910713 F2B DESIGNVARI Variant Editor crashes when you click web link under “Physical Part Filter” window.

910936 F2B PACKAGERXL ConceptHDL subdesign net name is inconsistent

911530 ALLEGRO_EDITOR SYMBOL Package Symbol Wizard does not create symbol with the name given

911631 CONCEPT_HDL CORE DEHDL crashes when opening a design

912001 ALLEGRO_EDITOR OTHER option_licenses entries are made in allegro.ini even when not set as default

912459 F2B BOM BOMHDL crashes before getting to a menu

913359 APD MANUFACTURING Package Report shows incorrect data

DATE: 06-24-2011 HOTFIX VERSION: 001

===================================================================================================================================

CCRID PRODUCT PRODUCTLEVEL2 TITLE

===================================================================================================================================

293005 ALLEGRO_EDITOR DATABASE Allegro crash when attempting to move mech. symbol

298289 CIS EXPLORER CIS querry gives wrong results

366939 ALLEGRO_EDITOR OTHER Cannot attach refdes on silk subclass with add text

432200 ALLEGRO_EDITOR MANUFACT Fillets with an arc are required for Flexi designs

443447 APD SHAPE Shapes not following the acute angle trim control setting.

473308 PSPICE AA_SENS Passing variables to lower level blocks using subparam

517556 PSPICE AA_SENS Advanced Analysis does not support variables being passed down the hierarchy

548143 ALLEGRO_EDITOR SHAPE Dynamic shpe on Etch TOP will not void properly.

606959 ADW COMPONENT_BROWSE Key properties with blank values are not getting read in shooping cart

616466 ALLEGRO_EDITOR SHAPE Solid shapes are not getting filled

641358 SIP_LAYOUT DIE_STACK_EDITOR Request for Via and Multi Layer Pin support for DIE stack Area (blue region)

644122 SIP_LAYOUT OTHER SiP Layout - xsection - ERROR Adjacent conductive layers are not allowed, but these are diestack layers not conductor

645816 ALLEGRO_EDITOR SHAPE Slide a cline all removes gnd shapes on board

725355 ALLEGRO_EDITOR SHAPE User can not voided Logo correctly.

763569 CONCEPT_HDL CORE Display status of Hide/Show unconnected pins icon in DE HDL UI

770021 CAPTURE BACKANNOTATE Changing pin group property after pin swap resets pin numbers

792126 CAPTURE PROPERTY_EDITOR Attempt to change display for occ prop resets

799014 CONCEPT_HDL CONSTRAINT_MGR concept2cm errors not shown in export physical after hier_write

803147 CIS LINK_DATABASE_PA Link DB part should not change RefDes of multi package part

804240 PSPICE DEHDL Problem in simulation result for a multi-section split part.

809118 CAPTURE NETLISTS ENH to compare two schematic Capture designs

816568 ALLEGRO_EDITOR SHAPE shape disappears when update to smooth.. State no etch

830053 CAPTURE STABILITY DXF export fails if schematic folder name as /

832108 ALLEGRO_EDITOR SHAPE Shape void incorrectly.

833542 CONCEPT_HDL CORE PDF publisher font is NOT WYSIWIG with respect to what seen in DE HDL

835777 CIS DERIVE_NEW_DB_PA For XLS, donot display table as worksheetName$worksheetName to avoid 8012 error

837640 CIS GEN_BOM date format of CIS BOM has broken macros of 16.2 in 16.3 version

844074 APD SPECCTRA_IF Export Router fails with memory errors.

851595 CONCEPT_HDL CORE Pin numbers overlap on the pin and increase in size

852832 CAPTURE BACKANNOTATE Why is Capture crashing with Mentor back annotation?

855015 ALLEGRO_EDITOR OTHER The rats are NOT connecting to the ends of the clines like they should be.

859883 CAPTURE NETLISTS ENH to compare two schematic Capture designs

866009 SIG_INTEGRITY OTHER Net with Pull-up/down should not be used for Diff-pair.

866830 SCM REPORTS Multiple lines added as separator between title block and report header instead of single line

866833 SCM REPORTS Extra indentation is left in the left side of the report when the Line Numbers are set to OFF

868618 SCM IMPORTS Block re-import does not update the docsch and sch view

873402 SIP_LAYOUT LOGIC pin swap for co-design die in SiP

874010 SIG_INTEGRITY OTHER PCB SI crashes when the Xnet is extracted with VARIANT_TO_IGNORE property.

874400 ALLEGRO_EDITOR INTERACTIV Flip mode issue with move command

874966 ALLEGRO_EDITOR INTERFACES Placed mechanical component do not get Ref Des or part number in IDF file

875709 ALLEGRO_EDITOR REPORTS Film area report generated incorrect data at l1

876275 CONCEPT_HDL CONSTRAINT_MGR Constraint Manager not retaining target net

879361 SCM UI SCM crashes when opening project

879496 CONCEPT_HDL OTHER Customer wants to have “the tabulation” key as separator in HDL BOM.

879514 PSPICE AA_MC Monte Carlo to handle equation as comp VALUE.

881845 ALLEGRO_EDITOR SHAPE Delete island deletes complete shape

882413 PDN_ANALYSIS PCB_PI PDN Analysis should support routed power nets

882427 PDN_ANALYSIS PCB_PI PDN Analysis target impedance should have a variable multiplier

882567 SIG_INTEGRITY OTHER PCB SI crash if boolean type prop was specified to VARIANT env.

882644 ALLEGRO_EDITOR PLACEMENT PCB Place Replicate Function automatically match Enhancement

883164 ALLEGRO_EDITOR INTERACTIV Vias marked fanout moves away from position when moving component

883224 SIG_INTEGRITY SIMULATION crash while reflection simulation from Constraint Manager

883760 PCB_LIBRARIAN METADATA Incorrectly formatted revision.dat file in the metadata folder

885391 SIG_INTEGRITY SIMULATION RLGC data sampling algorithm and w-element interpolation.

885849 ALLEGRO_EDITOR MANUFACT Silkscreen Audit cannot find Solder mask for the text string

885996 SIG_INTEGRITY OTHER The effect of sn_maxwidthlimit user preference is not seen in cross section impedance calculations

886090 ALLEGRO_EDITOR INTERACTIV Add Arc w/Radius does not snap to grid

887180 CAPTURE SCHEMATIC_EDITOR Signals Navigation window doesn’t get updated for Buses

887442 APD SHAPE Copper pour of Dynamic shapes on Top layer which contains many existing signal traces fails.

887578 SCM AUTO_UI Component Replace pops-up the DSPANE-204 Message

887926 SIG_INTEGRITY GEOMETRY_EXTRACT Field solution failed if diff trace on bottom doesn't have reference plane.

888414 SIG_EXPLORER OTHER View Trace Parameter display the thickness of dielectric incorrectly.

888600 CONCEPT_HDL CREFER Cross References not added to Schegen schematic

888679 SIP_LAYOUT SHAPE Can't create the Dynamic shape on layer M1_sig without unwanted horizontal openings appearing.

888804 ALLEGRO_EDITOR OTHER Fillet will become static shape after import from partition board.

888945 CONCEPT_HDL OTHER unplaced component after placing module

889222 ALLEGRO_EDITOR SHAPE Allegro freezes/hangs when adding shape as Polygon with OpenGL ON.

889365 SIG_INTEGRITY GEOMETRY_EXTRACT top/bottom trace impedances extracted to sigxp are wrong in 16.3

889404 ALLEGRO_EDITOR OTHER Incorrect pad size for Top conductor padstack written to column 59-62.

889426 CONCEPT_HDL CHECKPLUS CheckPlus does not find single node net

889636 ALLEGRO_EDITOR MANUFACT Incorrect spelling of "Visibility" in "Film Control" tab in the Artwork Control Form

891235 F2B PACKAGERXL Packager crashes without creating a pxl.log file

891292 ALLEGRO_EDITOR SHAPE arc routing causes weird undesireable shape fill performance

891856 ALLEGRO_EDITOR EDIT_ETCH crash when sliding diff pairs

892375 ALLEGRO_EDITOR PLACEMENT Place Replicate Update disband other groups, irrespective Fixed property added or not.

892455 ALLEGRO_EDITOR SYMBOL Why the overlapping pins are not reported with DRC?

892541 SIG_EXPLORER OTHER Export/Import layerstack through the technology file is changing the layer thickness

892766 APD WIREBOND Excuting Finger moving cannot push aside finger to move with together by shove all mode

892907 ALLEGRO_EDITOR DRC_CONSTR DRC not reported for etch_turn_under_pin violations

892963 ALLEGRO_EDITOR SKILL Bad shape boundary created after axlPolyOperation 'OR

892964 SIP_LAYOUT LOGIC Request that Edit Parts List use Dashes "-".

893295 APD WIREBOND Why move wirebond command does not shove wirebonds? This result in drcs.

893706 CONSTRAINT_MGR OTHER On line DRC hangs on partitioned board

893743 APD EDIT_ETCH Route behavior when spanning pads not as expected.

893783 SIP_LAYOUT OTHER Padstack Design Editing update File menu with a Update to Design and Close instead of 2 operation

894456 ALLEGRO_EDITOR REPORTS Request Net names be added to Propagation delay lines of the DRC report.

894499 SIG_INTEGRITY LIBRARY Tool crashes when moving a cline or selecting the Info icon with OpenGL on.

894582 APD SHAPE When making a dynamic xhatch Via shapes surrounding are abnormal.

895542 SIP_LAYOUT WIREBOND SIP design crashing when moving bond finger using blur mode BLUR_BONDFINGER_PRESRV_CON

895591 ALLEGRO_EDITOR PCAD_IN Importing PCAD file fails to get to the point where we can map layers

895757 APD ARTWORK Import Gerber command could not be imported Gerber data

895964 CONCEPT_HDL CHECKPLUS The CheckPlus command “getFileSubstrings” is not working correctly

896428 SCM UI Changed Ref Des value not maintained in DEHDL block when part is replaced

896655 CAPTURE EDIF Import/Export Design of Hierarcy design with OrCAD Capture

896846 CAPTURE IMPORT/EXPORT Import edif2cap and capture is crashing

897155 ALLEGRO_EDITOR REPORTS Copper coverage in L2 and L7 looks like the same but film area report had large gap.

897654 CAPTURE EE_INTERSHEET_RE Capture crashes on adding intersheet refernces in abbreviated format on attached design.

899344 RF_PCB BE_IFF_EXPORT dlibx2iff does not provide the component boundary drawing

899629 CONSTRAINT_MGR OTHER ECset for Total Etch Lenght is not present in OrCAD Prof

900175 CONCEPT_HDL CONSTRAINT_MGR Few Xnets are lost from Match Group after packaging and importing the netlist to board file.

900481 CONCEPT_HDL CORE Genview creates a larger symbol without taking the no. of pin in consideration

900813 ALLEGRO_EDITOR DRC_CONSTR With rotated pads, pad (pin - via) soldermask spacing DRC is unreasonable.

900905 PSPICE STABILITY Simsrvr crash and RPC Server unavailable error while running simulation.

901783 CONCEPT_HDL CORE CDS_PART_NAME is annotated on the schematic canvas after running back annotation in 16.5

901909 APD EXPORT_DATA The "package_pin_delay_length.rpt" with Z-axis delay turned on seems wrong

901987 CONCEPT_HDL OTHER SPB16.5 zoom fit does not center the page while ploting the schematic page

902133 CIS OTHER The visible part property value are being shown very distant from part graphics on schematic

902166 SPECCTRA ROUTE Specctra crashes when reading in "bestsave.w" file

902170 ALLEGRO_EDITOR DATABASE Diffpair Issues with OrCad PCB Designer Professional

902177 CONSTRAINT_MGR CONCEPT_HDL Option to view the layer thickness in CM worksheet through worksheet customization

902463 ALLEGRO_EDITOR INTERACTIV APD crashes when we click ( show element ) on certain components

902621 CONCEPT_HDL OTHER Design Differences (vdd) Crashes

902909 APD WIREBOND die to die wirebond crash

902933 ALLEGRO_EDITOR PADS_IN Pads_in fails while reading PADS ASCII file body

903284 PDN_ANALYSIS PCB_STATICIRDROP IRDrop voltage gradients are plotted outside of the PCB outline

903680 CONSTRAINT_MGR ECS_APPLY Constraint Manager not passing all hiearchical member objects to a custom measurement.

904403 ALLEGRO_EDITOR DATABASE Allegro crashes when refreshing module

===================================================================================================================================

CCRID PRODUCT PRODUCTLEVEL2 TITLE

===================================================================================================================================

527444 ALLEGRO_EDITOR EDIT_ETCH Slide command needs to be enhanced for same net spacings

583257 ALLEGRO_EDITOR EDIT_ETCH Add Connect and slide command needs to be enhanced for same net spacings.

592956 ALLEGRO_EDITOR EDIT_ETCH Same net traces will not push and/or shove each other.

745285 ALLEGRO_EDITOR EDIT_ETCH Requesting a true "shove" in Route > Slide for Same net routing.

773503 CAPTURE OTHER Doing "Mirror Horizontally" creates extra un-connects or extra junction dots in Capture V16.3.

774270 F2B PACKAGERXL Require to ignore space in Pattern setting to prevent duplicated Refdes.

799984 ALLEGRO_EDITOR INTERACTIV Enhance the Fix command to select just cline segs

809008 CAPTURE SCHEMATIC_EDITOR New nodes get appeared within the design when we select the design and do "Mirror Horizontally".

810058 CAPTURE SCHEMATIC_EDITOR New nodes get appeared within the design when we select the design and do "Mirror Horizontally".

821133 ALLEGRO_EDITOR MANUFACT Output artwork for pad data that are suppressed unconnected pads with Gerber 6x00 format

831710 CAPTURE SCHEMATIC_EDITOR Capture adds extra junctions to design by itself

842410 ALLEGRO_EDITOR EDIT_ETCH Ability to slide with "Shove" for "Same Net" segments/vias.

854971 ALLEGRO_EDITOR INTERACTIV Capability to add cline segment in a temp group

860772 ADW PCBCACHE Save Shopping Cart (pcbcache) is crashing component browser

867842 CAPTURE PROJECT_MANAGER Capture crash with 'Open File Location"

868306 CAPTURE CONNECTIVITY mirror vertically removes junction creates extra nets

882677 EMI RULE_CHECK bypass_plane_split fail if BYPASS_XXXX_EFFECT_DISTANCE

891439 ALLEGRO_EDITOR INTERACTIV moving cline segments

893544 ALLEGRO_EDITOR INTERFACES IPC-D-356A netlist issue with BB vias.

893765 ALLEGRO_EDITOR PARTITION Mail command not sending out email on Linux platforms.

894390 SIP_LAYOUT EXPORT_DATA Generate all balls in the xml file for export to EDI's readPackage command

895933 APD DATABASE Update Symbol shifts the center of the Dynamic Fillet and creating DRCs

896598 ALLEGRO_EDITOR PLACEMENT error message is misleading

897196 CIS LINK_DATABASE_PA Schematic Contents are not shown in CIS window while link Dbase part for parts placed from library

898598 ALLEGRO_EDITOR MENTOR Negative planes from Mentor Board Station not being translated.

899556 ALLEGRO_EDITOR ARTWORK Import artwork seems not to work correctly.

900501 ALLEGRO_EDITOR PLACEMENT "Place Replicate Apply" is showing lot of DRC's during placement of replicated circuit in 16.5

901141 CIS EXPLORER Japanese character appear garbled in CIS explorer window.

901666 CAPTURE OTHER Home page of Flowcad-Switzerland and Flowcal-Poland is not preserved on captre restart on start page

902066 ALLEGRO_EDITOR DRC_CONSTR Shape in Region not follow the constrains

902349 CAPTURE LIBRARY Capture crashes while closing library

902508 F2B PACKAGERXL SPB16.5 Packager-XL consumes much more memory than 16.3

902841 CAPTURE GENERAL Capture Start page does not show

902876 F2B PACKAGERXL Packager fails on the design upreved in 16.5

902959 CONCEPT_HDL HDLDIRECT HDLDirect Error while saving design

903171 PSPICE NETLISTER Why Capture is treating hierarchical power ports as floting nets in complex heirarchy designs?

903713 ALLEGRO_EDITOR PARTITION Placement Replication do not work fine in the Design Partition

903799 SIP_LAYOUT DIE_EDITOR Disappear die pins after exiting co-design die editor

904021 ALLEGRO_EDITOR OTHER Export PDF from SPB 16.5 produces a file not text searchable

904339 CONCEPT_HDL CORE new design crashes using the attached CDS_SITE

904522 F2B PACKAGERXL Part will not package in 16.5 but packages in 16.3

904764 APD OTHER Enhance Scale Factor of Stream Out to support 4 decimal places

904771 ALLEGRO_EDITOR MANUFACT Pin Number display issue.

904853 ALLEGRO_EDITOR GRAPHICS Enhancement for showing Static shape as it was seen in 16.3

905144 CONSTRAINT_MGR ECS_APPLY Min Line Spacing is larger than Primary or Neck Gap less(-) Tolerance but No Warning in CM

905314 F2B PACKAGERXL Import physical causes csb corruption

905337 CONCEPT_HDL CORE ConceptHDL crashes after Import Design process.

905533 ALLEGRO_EDITOR INTERACTIV Pin numbers for components on BOTTOM Side are moved in Preselect mode,when the BOTTOM layer is invisible

905796 CONCEPT_HDL CONSTRAINT_MGR Fujitsu CM issue inaccurate concept2cm diff pair issues

905811 CAPTURE EE_INTERSHEET_RE interesheet references in the form of grid grid page number instead of page number grid

906118 CONCEPT_HDL CONSTRAINT_MGR Cannot open CM if SIGNAL_MODEL value was not assigned in ptf.

906153 ALLEGRO_EDITOR SCRIPTS Unable to run allegro script in batch mode on the attached board.

906182 APD EXPORT_DATA Modify Board Level Component Output format

906200 ALLEGRO_EDITOR DFA Enh- DFA drc invoked in Batch mode returns false constraint value in Show Element

906517 PSPICE PROBE PSpice new cursor window shows incorrect result.

906627 ADW COMPONENT_BROWSE ppt options are not read if ucb is launched from FM. works fine if launched from dehdl.

906647 SIG_INTEGRITY LIBRARY lib_dist creates a signoise.log in current directory (with backup files like ,1 ,2 etc.) on each run

906673 F2B PACKAGERXL Ignore the signal model validity check during packaging

906688 ADW LRM A copy of source design gets created in worklib of target design after 'Import Design'

906750 ALLEGRO_EDITOR PARTITION Importing design partition removes the testpoint reference designation

906874 PSPICE NETLISTER Error less than 2 connections for unconnected hierarchical pin

907095 F2B OTHER Part Manager does not show Error as Undefined when directive ptf_mismatch_exclude_inj_prop is used

907424 ALLEGRO_EDITOR GRAPHICS Allegro add option for pre 16.5 shape display

907490 CAPTURE NETLIST_LAYOUT 16.5 Layout netlist is not correct. It differs form 16.3 layout netlist.

907884 SIP_LAYOUT MANUFACTURING Need to add an "NC" pin text option for "Manufacturing Documentation Display Pin Text"

907885 SIG_INTEGRITY OTHER Matchgroup targets lost when importing netlist to Allegro layout in HF31

907929 CAPTURE TCL_SAMPLE TCL command to delete a property from parts in a library is not working correctly

907933 SIG_INTEGRITY OTHER Single line impedence not working in OrCad PCB Professional

907963 CONCEPT_HDL CORE Design uprev issue when moving from 16.2 to 16.5

908000 SIG_INTEGRITY OTHER Inconsistence z-axis delay reported on Tpoint when define at via location.

908057 CONCEPT_HDL CORE DE HDL crash with the cut and paste of a signal name

908060 CONCEPT_HDL CORE CTRL+LMB Option not working correctly in 16.3

908210 CAPTURE CONNECTIVITY Connection is being lost while dragging a component

908241 CAPTURE DRC DRC error column is blank in DRC markers window in 16.5

908339 RF_PCB BE_IFF_IMPORT mechanical holes VIAFC are not at the right place

908534 SIP_LAYOUT SYMB_EDIT_APPMOD issues with symbol editor and copying pin arrays

908535 F2B DESIGNVARI When I try to view my variant file the variant editor crashes

908595 APD 3D_VIEWER Cadence Design 3D viewer" screen pops up and is all black because the colors have all converted to b

908849 CAPTURE ANNOTATE Getting crash while annotating the attached design

908874 CONCEPT_HDL CORE Part Manager - No Part Found error when using CCR# 775788 feature

909077 CONCEPT_HDL CORE After packaging pin numbers remains invisible even when $PN

909104 ALLEGRO_EDITOR SYMBOL Warning message needs to be modified. It does not save the symbol and also not tell the actual problem.

909417 ALLEGRO_EDITOR REPORTS "report -v upc" returns 'Segmentation fault' on Linux

909635 SIP_LAYOUT DIE_STACK_EDITOR Add Interposer crashes in SiP Layout

909749 ALLEGRO_EDITOR MANUFACT Allegro Crash during dimensioning

909760 SIP_LAYOUT MANUFACTURING Create bond finger solder mask doesn't follow the mask opening as defined in the padstack

909861 F2B PACKAGERXL NetAssembler broken within the latest 16.30.031

910006 CONCEPT_HDL INFRA Motorola design fails to uprev from 16.3 to 16.5, xcon file is getting corrupted.

910141 CAPTURE NETGROUPS Modify NetGroup definition does not update Offpage Connector

910340 ADW LRM Import design in schematic, only 1 page import, the entire block is getting imported.

910678 SIG_INTEGRITY OTHER The Analyze> Model Assignment> Auto setup is not creating/assigning models to discrete components in 16.5

910713 F2B DESIGNVARI Variant Editor crashes when you click web link under “Physical Part Filter” window.

910936 F2B PACKAGERXL ConceptHDL subdesign net name is inconsistent

911530 ALLEGRO_EDITOR SYMBOL Package Symbol Wizard does not create symbol with the name given

911631 CONCEPT_HDL CORE DEHDL crashes when opening a design

912001 ALLEGRO_EDITOR OTHER option_licenses entries are made in allegro.ini even when not set as default

912459 F2B BOM BOMHDL crashes before getting to a menu

913359 APD MANUFACTURING Package Report shows incorrect data

DATE: 06-24-2011 HOTFIX VERSION: 001

===================================================================================================================================

CCRID PRODUCT PRODUCTLEVEL2 TITLE

===================================================================================================================================

293005 ALLEGRO_EDITOR DATABASE Allegro crash when attempting to move mech. symbol

298289 CIS EXPLORER CIS querry gives wrong results

366939 ALLEGRO_EDITOR OTHER Cannot attach refdes on silk subclass with add text

432200 ALLEGRO_EDITOR MANUFACT Fillets with an arc are required for Flexi designs

443447 APD SHAPE Shapes not following the acute angle trim control setting.

473308 PSPICE AA_SENS Passing variables to lower level blocks using subparam

517556 PSPICE AA_SENS Advanced Analysis does not support variables being passed down the hierarchy

548143 ALLEGRO_EDITOR SHAPE Dynamic shpe on Etch TOP will not void properly.

606959 ADW COMPONENT_BROWSE Key properties with blank values are not getting read in shooping cart

616466 ALLEGRO_EDITOR SHAPE Solid shapes are not getting filled

641358 SIP_LAYOUT DIE_STACK_EDITOR Request for Via and Multi Layer Pin support for DIE stack Area (blue region)

644122 SIP_LAYOUT OTHER SiP Layout - xsection - ERROR Adjacent conductive layers are not allowed, but these are diestack layers not conductor

645816 ALLEGRO_EDITOR SHAPE Slide a cline all removes gnd shapes on board

725355 ALLEGRO_EDITOR SHAPE User can not voided Logo correctly.

763569 CONCEPT_HDL CORE Display status of Hide/Show unconnected pins icon in DE HDL UI

770021 CAPTURE BACKANNOTATE Changing pin group property after pin swap resets pin numbers

792126 CAPTURE PROPERTY_EDITOR Attempt to change display for occ prop resets

799014 CONCEPT_HDL CONSTRAINT_MGR concept2cm errors not shown in export physical after hier_write

803147 CIS LINK_DATABASE_PA Link DB part should not change RefDes of multi package part

804240 PSPICE DEHDL Problem in simulation result for a multi-section split part.

809118 CAPTURE NETLISTS ENH to compare two schematic Capture designs

816568 ALLEGRO_EDITOR SHAPE shape disappears when update to smooth.. State no etch

830053 CAPTURE STABILITY DXF export fails if schematic folder name as /

832108 ALLEGRO_EDITOR SHAPE Shape void incorrectly.

833542 CONCEPT_HDL CORE PDF publisher font is NOT WYSIWIG with respect to what seen in DE HDL

835777 CIS DERIVE_NEW_DB_PA For XLS, donot display table as worksheetName$worksheetName to avoid 8012 error

837640 CIS GEN_BOM date format of CIS BOM has broken macros of 16.2 in 16.3 version

844074 APD SPECCTRA_IF Export Router fails with memory errors.

851595 CONCEPT_HDL CORE Pin numbers overlap on the pin and increase in size

852832 CAPTURE BACKANNOTATE Why is Capture crashing with Mentor back annotation?

855015 ALLEGRO_EDITOR OTHER The rats are NOT connecting to the ends of the clines like they should be.

859883 CAPTURE NETLISTS ENH to compare two schematic Capture designs

866009 SIG_INTEGRITY OTHER Net with Pull-up/down should not be used for Diff-pair.

866830 SCM REPORTS Multiple lines added as separator between title block and report header instead of single line

866833 SCM REPORTS Extra indentation is left in the left side of the report when the Line Numbers are set to OFF

868618 SCM IMPORTS Block re-import does not update the docsch and sch view

873402 SIP_LAYOUT LOGIC pin swap for co-design die in SiP

874010 SIG_INTEGRITY OTHER PCB SI crashes when the Xnet is extracted with VARIANT_TO_IGNORE property.

874400 ALLEGRO_EDITOR INTERACTIV Flip mode issue with move command

874966 ALLEGRO_EDITOR INTERFACES Placed mechanical component do not get Ref Des or part number in IDF file

875709 ALLEGRO_EDITOR REPORTS Film area report generated incorrect data at l1

876275 CONCEPT_HDL CONSTRAINT_MGR Constraint Manager not retaining target net

879361 SCM UI SCM crashes when opening project

879496 CONCEPT_HDL OTHER Customer wants to have “the tabulation” key as separator in HDL BOM.

879514 PSPICE AA_MC Monte Carlo to handle equation as comp VALUE.

881845 ALLEGRO_EDITOR SHAPE Delete island deletes complete shape

882413 PDN_ANALYSIS PCB_PI PDN Analysis should support routed power nets

882427 PDN_ANALYSIS PCB_PI PDN Analysis target impedance should have a variable multiplier

882567 SIG_INTEGRITY OTHER PCB SI crash if boolean type prop was specified to VARIANT env.

882644 ALLEGRO_EDITOR PLACEMENT PCB Place Replicate Function automatically match Enhancement

883164 ALLEGRO_EDITOR INTERACTIV Vias marked fanout moves away from position when moving component

883224 SIG_INTEGRITY SIMULATION crash while reflection simulation from Constraint Manager

883760 PCB_LIBRARIAN METADATA Incorrectly formatted revision.dat file in the metadata folder

885391 SIG_INTEGRITY SIMULATION RLGC data sampling algorithm and w-element interpolation.

885849 ALLEGRO_EDITOR MANUFACT Silkscreen Audit cannot find Solder mask for the text string

885996 SIG_INTEGRITY OTHER The effect of sn_maxwidthlimit user preference is not seen in cross section impedance calculations

886090 ALLEGRO_EDITOR INTERACTIV Add Arc w/Radius does not snap to grid

887180 CAPTURE SCHEMATIC_EDITOR Signals Navigation window doesn’t get updated for Buses

887442 APD SHAPE Copper pour of Dynamic shapes on Top layer which contains many existing signal traces fails.

887578 SCM AUTO_UI Component Replace pops-up the DSPANE-204 Message

887926 SIG_INTEGRITY GEOMETRY_EXTRACT Field solution failed if diff trace on bottom doesn't have reference plane.

888414 SIG_EXPLORER OTHER View Trace Parameter display the thickness of dielectric incorrectly.

888600 CONCEPT_HDL CREFER Cross References not added to Schegen schematic

888679 SIP_LAYOUT SHAPE Can't create the Dynamic shape on layer M1_sig without unwanted horizontal openings appearing.

888804 ALLEGRO_EDITOR OTHER Fillet will become static shape after import from partition board.

888945 CONCEPT_HDL OTHER unplaced component after placing module

889222 ALLEGRO_EDITOR SHAPE Allegro freezes/hangs when adding shape as Polygon with OpenGL ON.

889365 SIG_INTEGRITY GEOMETRY_EXTRACT top/bottom trace impedances extracted to sigxp are wrong in 16.3

889404 ALLEGRO_EDITOR OTHER Incorrect pad size for Top conductor padstack written to column 59-62.

889426 CONCEPT_HDL CHECKPLUS CheckPlus does not find single node net

889636 ALLEGRO_EDITOR MANUFACT Incorrect spelling of "Visibility" in "Film Control" tab in the Artwork Control Form

891235 F2B PACKAGERXL Packager crashes without creating a pxl.log file

891292 ALLEGRO_EDITOR SHAPE arc routing causes weird undesireable shape fill performance

891856 ALLEGRO_EDITOR EDIT_ETCH crash when sliding diff pairs

892375 ALLEGRO_EDITOR PLACEMENT Place Replicate Update disband other groups, irrespective Fixed property added or not.

892455 ALLEGRO_EDITOR SYMBOL Why the overlapping pins are not reported with DRC?

892541 SIG_EXPLORER OTHER Export/Import layerstack through the technology file is changing the layer thickness

892766 APD WIREBOND Excuting Finger moving cannot push aside finger to move with together by shove all mode

892907 ALLEGRO_EDITOR DRC_CONSTR DRC not reported for etch_turn_under_pin violations

892963 ALLEGRO_EDITOR SKILL Bad shape boundary created after axlPolyOperation 'OR

892964 SIP_LAYOUT LOGIC Request that Edit Parts List use Dashes "-".

893295 APD WIREBOND Why move wirebond command does not shove wirebonds? This result in drcs.

893706 CONSTRAINT_MGR OTHER On line DRC hangs on partitioned board

893743 APD EDIT_ETCH Route behavior when spanning pads not as expected.

893783 SIP_LAYOUT OTHER Padstack Design Editing update File menu with a Update to Design and Close instead of 2 operation

894456 ALLEGRO_EDITOR REPORTS Request Net names be added to Propagation delay lines of the DRC report.

894499 SIG_INTEGRITY LIBRARY Tool crashes when moving a cline or selecting the Info icon with OpenGL on.

894582 APD SHAPE When making a dynamic xhatch Via shapes surrounding are abnormal.

895542 SIP_LAYOUT WIREBOND SIP design crashing when moving bond finger using blur mode BLUR_BONDFINGER_PRESRV_CON

895591 ALLEGRO_EDITOR PCAD_IN Importing PCAD file fails to get to the point where we can map layers

895757 APD ARTWORK Import Gerber command could not be imported Gerber data

895964 CONCEPT_HDL CHECKPLUS The CheckPlus command “getFileSubstrings” is not working correctly

896428 SCM UI Changed Ref Des value not maintained in DEHDL block when part is replaced

896655 CAPTURE EDIF Import/Export Design of Hierarcy design with OrCAD Capture

896846 CAPTURE IMPORT/EXPORT Import edif2cap and capture is crashing

897155 ALLEGRO_EDITOR REPORTS Copper coverage in L2 and L7 looks like the same but film area report had large gap.

897654 CAPTURE EE_INTERSHEET_RE Capture crashes on adding intersheet refernces in abbreviated format on attached design.

899344 RF_PCB BE_IFF_EXPORT dlibx2iff does not provide the component boundary drawing

899629 CONSTRAINT_MGR OTHER ECset for Total Etch Lenght is not present in OrCAD Prof

900175 CONCEPT_HDL CONSTRAINT_MGR Few Xnets are lost from Match Group after packaging and importing the netlist to board file.

900481 CONCEPT_HDL CORE Genview creates a larger symbol without taking the no. of pin in consideration

900813 ALLEGRO_EDITOR DRC_CONSTR With rotated pads, pad (pin - via) soldermask spacing DRC is unreasonable.

900905 PSPICE STABILITY Simsrvr crash and RPC Server unavailable error while running simulation.

901783 CONCEPT_HDL CORE CDS_PART_NAME is annotated on the schematic canvas after running back annotation in 16.5

901909 APD EXPORT_DATA The "package_pin_delay_length.rpt" with Z-axis delay turned on seems wrong

901987 CONCEPT_HDL OTHER SPB16.5 zoom fit does not center the page while ploting the schematic page

902133 CIS OTHER The visible part property value are being shown very distant from part graphics on schematic

902166 SPECCTRA ROUTE Specctra crashes when reading in "bestsave.w" file

902170 ALLEGRO_EDITOR DATABASE Diffpair Issues with OrCad PCB Designer Professional

902177 CONSTRAINT_MGR CONCEPT_HDL Option to view the layer thickness in CM worksheet through worksheet customization

902463 ALLEGRO_EDITOR INTERACTIV APD crashes when we click ( show element ) on certain components

902621 CONCEPT_HDL OTHER Design Differences (vdd) Crashes

902909 APD WIREBOND die to die wirebond crash

902933 ALLEGRO_EDITOR PADS_IN Pads_in fails while reading PADS ASCII file body

903284 PDN_ANALYSIS PCB_STATICIRDROP IRDrop voltage gradients are plotted outside of the PCB outline

903680 CONSTRAINT_MGR ECS_APPLY Constraint Manager not passing all hiearchical member objects to a custom measurement.

904403 ALLEGRO_EDITOR DATABASE Allegro crashes when refreshing module

visit my blog

Name: Cadence SPB/OrCAD

Version: 16.5.00(1)2 (Allegro SPB) 32bit Hotfix

Creator: www.cadence.com

Interface: english

OS: Windows XP / Vista / Seven

Platform: Cadence SPB/OrCAD 16.5.000

Size: 736.5 mb

Скачать | Download c filesonic.com

Скачать | Download c letitbit.net

Скачать | Download c depositfiles.com

Скачать | Download c vip-file.com

http://www.filesonic.com/file/1584904261/csoc165002uo.part1.rar

http://www.filesonic.com/file/1584995651/csoc165002uo.part2.rar

http://www.filesonic.com/file/1585057051/csoc165002uo.part3.rar

http://letitbit.net/download/6...7a/csoc165002uo.part1.rar.html

http://letitbit.net/download/2...f2/csoc165002uo.part2.rar.html

http://letitbit.net/download/4...5e/csoc165002uo.part3.rar.html

http://depositfiles.com/files/ttnfg1jx8

http://depositfiles.com/files/15w8l9kon

http://depositfiles.com/files/v791b2nbm

All parts on depositfiles.com, letitbit.net, filesonic.com interchanged. It is added by 5% of the overall size of the archive of information for the restoration

No mirrors please

No mirrors please