Cadence Virtuoso Studio IC23.10.130 | 12.1 Gb

Cadence Design Systems, Inc. announced the new Cadence Virtuoso Studio IC23.10.130, a next-generation custom design platform that delivers an optimal design experience and ushers in the future for custom analog design.

Cadence Unleashes the Future of Analog, Custom and RFIC Design with Pioneering AI-Powered Virtuoso Studio

Highlights:

- Industry’s leading platform for creating differentiated custom silicon delivers unmatched productivity benefits with new generative AI technology

- Virtuoso Studio empowers designers to push semiconductor and 3D-IC design boundaries by seamless integration with Cadence’s cutting-edge technologies and modern infrastructure

- Leverages 30 years of industry leadership for all process technologies enabling 3X productivity improvement for today’s largest designs that will shape the world of tomorrow

Virtuoso Studio features a reimagined infrastructure with a unique approach to managing design processes and allows more than a 3X improvement in design throughput for today’s largest designs, enabling customers to meet aggressive time-to-market goals.

Virtuoso Studio addresses the challenges customers face with larger, more complex designs, empowering them to analyze and verify designs to ensure that design intent is maintained throughout the design cycle. This new platform features seamless integration with other Cadence solutions, including the Cadence Spectre Simulation Platform, Cadence Allegro PCB Design and Cadence Pegasus Verification System, removing traditional barriers between different design domains and speeding design closure. Virtuoso Studio is newly integrated with the AWR® Microwave Office solution, and the Pegasus Design Rule Check (DRC) Solution and Layout Versus Schematic (LVS) Solution are now available from within the Virtuoso Layout Suite. These provide advanced mmWave design and interactive signoff quality analysis during layout creation. Additionally, customers can access the Spectre Simulation Platform, including the Spectre X Simulator and Spectre FX Simulator, through Virtuoso Studio, which allows for the analysis of the industry’s largest analog and mixed-signal designs.

The new Virtuoso Studio platform offers customers the same great experience they are accustomed to, with the following benefits to address growing complexity:

- Proven Solution: Virtuoso Studio continues to offer the secure, proven solutions that industry-leading companies and foundries have trusted for 30 years for their analog, RFIC and mixed-signal designs.

- Improved Productivity: Design teams can leverage comprehensive planar and FinFET-based layout placement automation and new routing solutions to improve engineering productivity.

- Cloud-Ready: Virtuoso Studio offers massively scalable, cloud-ready solutions for occurrences when hundreds of simulations turn into thousands. It is optimized for customers’ preferred cloud providers or ready for private cloud deployment.

- Generative AI for Design Migration: The foundry-supported solutions ease the burden of process migration for schematics and layouts. Tools within the Virtuoso ADE Suite quickly re-center and validate designs post-migration, so customers can achieve aggressive time-to-market goals. Customers can utilize the AI-enabled tools to take existing IP and transform it for their next-generation designs.

- 3D-IC Integration: Virtuoso Studio allows the heterogeneous integration of 2.5D and 3D designs for advanced nodes, analog/RF packaging/modules and photonics systems.

Virtuoso Studio stays at the forefront of delivering designs accurately and on time through innovative improvements in traditional custom design tools. The new Design Space Optimization feature lets customers utilize AI algorithms to navigate competing specifications and aid in design centering, particularly after the process migration of a design. Customers can experience faster interactive editing in both the layout and schematic tools, thanks to optimized code and algorithms, while multi-threading accelerates rendering, connectivity extraction and design rule checks in parallel. Additionally, the Cadence Spectre FMC Analysis is integrated into Virtuoso Studio and provides a complete machine learning (ML)-based Monte Carlo variation solution to deliver a 3-to-6-sigma yield with orders of magnitude speedup over brute force Monte Carlo analysis.

CCR

Number TITLE

3118209 Probing a net in the schematic causes Virtuoso Studio to exit unexpectedly

3109658 Columns in the net summary table display incorrect sorting order

3107524 Lint error occurs when the LDO driver name is not specified when setting refvoltage=vref

3106402 Checker fails when minStepEdgeLength is specified with widthRanges and adjEolSpacingRange parameters

3106141 Print Tree command in Virtuoso Schematic Editor skips a cell hierarchy

3105169 When using a third-party simulator, additional expression evaluator startup time is observed for each simulation point

3103994 Virtuoso Studio exits unexpectedly upon multiple clicks in the second section under Notes in the Design Intent form for layout

3103992 The Design Intent form in layout has two sections under Notes

3103117 Virtuoso ADE Assembler exits unexpectedly when opening a maestro view saved from an older release

3101320 AppData write triggers read of route data, bypassing route preWrite/postWrite actions and corrupting the data

3100813 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3100775 Cannot stop the Extract step in Abstract Generator GUI

3100290 Zero coverage in generate coverage file flow

3099796 View size increases after saving EAD layout without any parasitic extracted

3097921 When the library contains the minOppExtension constraint, selecting Rule on the Install Guard Ring form returns a SKILL error

3097532 Virtuoso Studio exits unexpectedly when running re-evaluation

3097365 When auCdlTermOrderStr is set to D, the terminals with underscore are not expanding correctly

3097247 Unchecked reference libraries can damage the hierarchy when using the Check Hierarchy command

3097177 Top-level terminal not recognized when creating High Current Design Intent for a net

3096673 Issue in expression evaluation results in empty fields in the Results table

3096671 Netlisting does not complete for the age stage in reliability simulation

3096638 sp analysis netlists incorrectly if diffsprobe is not in the top-level schematic

3095820 Incorrect row snapping when running Edit In Group

3095474 Spice In reports an error when the net names have square brackets in the middle

3095047 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3094879 Standard cell router modifies the existing via and causes drc error on minimum area

3094233 The Create Guard Ring results are the same in custom area mode and row region mode

3093393 Dummies are placed outside the PR boundary when using Automated Placement and Routing Dummy Fill

3093328 The fill box shape is affected by the presence of a resistor and capacitor device in the same row in Align Fill mode

3092811 Assisted Export seems to miss vias originating from flattening of a Pcell instance

3092655 Create Symbol Using TSG' returns an error and the ihdl process does not start

3092602 Instance binding in HED config to .amsbind.scs translation is incorrect in the AMS flow

3092285 The Run Preview tab is not displaying the details of tests

3092147 Virtuoso ADE Assembler stops responding when adding instance parameters

3091847 minSideSpacing does not flag 'ignoreJoint violations correctly due to an incorrect dependency on joint width

3091472 Virtuoso Studio IC23.1 exits unexpectedly while using the ISR10 version due to QT issues

3091441 Speed up Verilog netlist creation with the vector expression

3091136 The Create Wire command with the Cover Pin option generates incorrect via extension

3091108 Pin Accessibility Checker should place topologies snapped to the placement grid

3090864 The Text-to-Symbol Generator files cannot be imported when 'Create Symbol Using TSG' is selected

3090435 EAD not generating all nets specified in the DSPF file

3090324 Unchecked reference libraries can damage the hierarchy when using the Check Hierarchy command

3089988 Support the Remove from Group command for group arrays that are members of figGroup

3089969 Unable to create a group array for MPPs using the Copy command

3089886 Single cell matrix should have all the X pins connected only to X pins of the other cell instances

3089501 Improve the message that is printed when the 'ade_e.scs' file is not created

3088239 Allow a locked technology constraint group to be used as constraint group for netclass in the Routing Constraint Manager

3087482 sp analysis netlists incorrectly if diffsprobe is not in the top-level schematic

3086880 Performance issues observed while opening or closing a maestro cellview with a huge number of histories

3086800 iPegasus does not use the correct area limit in free mode

3085320 Specified master cannot be selected when using the 'Select By Property' option

3085305 Specified net name cannot be selected when using the 'Select By Property' option

3084880 Air gap in design creates an uneditable entry in Stack Editor

3084601 Do not display swept parameters in the Dc Mismatch Summary form

3084518 When synchronizing layout or schematic with the design intent at the top-level, the old design intent is not removed

3084461 Autogenerated WSPs on M2 have no color mask information when creating several types of analog cells

3084145 Performance improvement of the Check and Save operation in Text Editor

3083932 Adding a group array interactively to a figGroup is not working as expected

3083724 Changing the active pattern using the Track Pattern assistant does not refresh the snap pattern drawn in the design

3083181 APR Router is not closing M0 connections in analog routing rings

3083105 Virtuoso SystemVerilog Netlister fails when the netlist.oa file is not created

3082761 The lxDummy property is not added when dummy devices are generated

3082111 The advanced Tie Shield command remains incomplete due to unconnected nets

3082015 When creating M0 WSPs, no tracks are generated on the overlaps in the M0 local regions

3081623 Label name cannot be added to the library name in the IP export flow for the runsv command

3080918 When using the Current pattern preset, the spacing set in the Property Editor is reset to 0

3080754 Guard ring is generated without nets and unable to connect to power ground mesh wire

3079913 Multi-cell migration maps instance to wrong library

3079439 Name of history zip file is created with a space

3079424 Voltus-XFi cannot find the syntax error in the config options for the Custom EM Plug-in flow

3078964 actime is grayed out in the Transient Options form when there are multiple test and AMS simulator is used

3078677 XStream In is showing errors for a zero-length line object

3076399 A PBSR restart simulation creates a global variable that is reused for every subsequent restart simulation

3075277 Device Router creates invalid hierarchical connection violations

3075179 The drGetDataFormatEntryForPattern SKILL function is not working as expected

3074321 Group array generation fails when an unsavable ruler is selected

3073967 Pattern names of resistor devices are not saved to csv files

3072280 In MATLAB Interface, accessing AdeInfoManager gives P-code related warning

3071604 LVS binder option should flatten the hierarchy instead of creating transparent instances

3070796 The SystemVerilog editor has an increased extraction time due to multiple UPF text views

3070399 In multi-cell migration, the Results browser cannot be used when temporary libraries are removed

3070364 False error flagged for minLargeViaArrayCutSpacing

3070199 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3068069 Unexpected minSpacing error in the Pin Accessibility Checker result

3066756 Remove new line characters from the Model Library and Simulation Files Setup forms

3066196 With 'onHistoryNameCollision' set to IncrementAsNew, automatic history item numbering is not done for custom-named Explorer runs

3059244 SINAD is not correctly calculated for a two-tone signal

3058153 When tandem shielding with layers minWidth, tandemWidth on the Constraint Manager should display 'no value' instead of 0

3057884 ocnxlOutputExpr not working when the output expression contains a variable

3052017 License error occurs when emirutil report=[text] is specified with emirutil autorun=[true]

3050966 Virtuoso Studio becomes unresponsive when running simulations in LSCS mode

3044019 Confusing 'oppoint' options in the DC Analysis form

3043915 Custom column is copied to the Name column in Outputs tab when importing outputs from a CSV to multiple tests

3043675 The Common Centroid preset is reset to Current when there are resistor devices in a design

3041957 Auto Via assistant engine fails to report the 'Vias with no added metal' violation

3037723 Opening a maestro view takes longer than expected

3032841 One of the outputs in calcVal Wizard is grayed out in the selection set, but can be used for typing

3030541 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3030508 Reloading waveforms changes the legends of y axis from dB to volt

3028021 Schematic bindkeys for Calculator are not working

3024605 Plotting waveforms from a new run replaces previous plots even when the plotting mode is set to 'append'

3015046 For multiple simultaneous simulations, successfully run results are incorrectly shown as canceled

3013794 Min Number Cuts setting is not reflected to each via layer in Via Configuration Editor of Routing Constraint Manager

3009695 Instantiated text views can cause the pc.db file to explicitly refer a particular library

3009375 Max values of MAS are not evaluated

3006400 Alignment to ruler does not work when running edit-in-place

3006206 calcVal Lint check is not aware of the corner affinity algorithm

3003327 Job Details assistant does not show pointID in the last line of the log fil

2993704 Antenna numbers for the Metal2 layer are not present in the lef file when ExtractAntennaPinPathsOnly is set to true

2992463 Remove the 'filename' field for oppoint in DC options form

2980859 The job policy setup information is not stored in the setup state

2977175 In Virtuoso Schematic Migration, the Results browser cannot be opened after running multi-cell cleanup

2963457 Unselected items are copied by the Copy wizard into the category specified in the Add To Category field

2956218 Minimum spacing is not applied when transitioning from a vertical M3 bus to a horizontal M4 bus

2953410 Virtuoso Studio becomes unresponsive when using the Netlist and Run options in LSCS

2951733 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

2950654 Virtuoso Studio exits unexpectedly while using IC23.1 ISR4

2949460 Run Plan simulation returns false errors about conflicting variable names in sweeps and corners

2942889 Fault dropping fails in case of a simulation time out error

2941377 Net tracer does not trace all shapes and incorrectly places halos during edit-in-place

2930586 sim err points stop other points from running reliability simulation in LSCS mode

2927997 Cannot plot the results of sp sprobe analysis after plotting the results of ac,sp, and hb analyses

2920662 Apply Previous does not update Pcell parameters

2634838 Provide an option to specify the views to be checked by the cross-view checks in Text Editor

2624680 calcVal fails when corners are rearranged in Virtuoso ADE Assembler

2572468 Allow overwriting of job policies for Voltus-XFi Analysis setup

2570046 The job policy configuration feature for Spectre simulation is missing in Voltus-XFi

2495946 Disable saving of the operating point information to a log file

2232078 Virtuoso RF: WHen voiding, dynamic shapes with no connectivity must not merge with dynamic shapes with connectivity

2117025 Support calcVal with MAS in run plan

1900688 Incorrect view is checked by cross-view checks in Text Editor

March 2025

Number TITLE

3118209 Probing a net in the schematic causes Virtuoso Studio to exit unexpectedly

3109658 Columns in the net summary table display incorrect sorting order

3107524 Lint error occurs when the LDO driver name is not specified when setting refvoltage=vref

3106402 Checker fails when minStepEdgeLength is specified with widthRanges and adjEolSpacingRange parameters

3106141 Print Tree command in Virtuoso Schematic Editor skips a cell hierarchy

3105169 When using a third-party simulator, additional expression evaluator startup time is observed for each simulation point

3103994 Virtuoso Studio exits unexpectedly upon multiple clicks in the second section under Notes in the Design Intent form for layout

3103992 The Design Intent form in layout has two sections under Notes

3103117 Virtuoso ADE Assembler exits unexpectedly when opening a maestro view saved from an older release

3101320 AppData write triggers read of route data, bypassing route preWrite/postWrite actions and corrupting the data

3100813 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3100775 Cannot stop the Extract step in Abstract Generator GUI

3100290 Zero coverage in generate coverage file flow

3099796 View size increases after saving EAD layout without any parasitic extracted

3097921 When the library contains the minOppExtension constraint, selecting Rule on the Install Guard Ring form returns a SKILL error

3097532 Virtuoso Studio exits unexpectedly when running re-evaluation

3097365 When auCdlTermOrderStr is set to D, the terminals with underscore are not expanding correctly

3097247 Unchecked reference libraries can damage the hierarchy when using the Check Hierarchy command

3097177 Top-level terminal not recognized when creating High Current Design Intent for a net

3096673 Issue in expression evaluation results in empty fields in the Results table

3096671 Netlisting does not complete for the age stage in reliability simulation

3096638 sp analysis netlists incorrectly if diffsprobe is not in the top-level schematic

3095820 Incorrect row snapping when running Edit In Group

3095474 Spice In reports an error when the net names have square brackets in the middle

3095047 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3094879 Standard cell router modifies the existing via and causes drc error on minimum area

3094233 The Create Guard Ring results are the same in custom area mode and row region mode

3093393 Dummies are placed outside the PR boundary when using Automated Placement and Routing Dummy Fill

3093328 The fill box shape is affected by the presence of a resistor and capacitor device in the same row in Align Fill mode

3092811 Assisted Export seems to miss vias originating from flattening of a Pcell instance

3092655 Create Symbol Using TSG' returns an error and the ihdl process does not start

3092602 Instance binding in HED config to .amsbind.scs translation is incorrect in the AMS flow

3092285 The Run Preview tab is not displaying the details of tests

3092147 Virtuoso ADE Assembler stops responding when adding instance parameters

3091847 minSideSpacing does not flag 'ignoreJoint violations correctly due to an incorrect dependency on joint width

3091472 Virtuoso Studio IC23.1 exits unexpectedly while using the ISR10 version due to QT issues

3091441 Speed up Verilog netlist creation with the vector expression

3091136 The Create Wire command with the Cover Pin option generates incorrect via extension

3091108 Pin Accessibility Checker should place topologies snapped to the placement grid

3090864 The Text-to-Symbol Generator files cannot be imported when 'Create Symbol Using TSG' is selected

3090435 EAD not generating all nets specified in the DSPF file

3090324 Unchecked reference libraries can damage the hierarchy when using the Check Hierarchy command

3089988 Support the Remove from Group command for group arrays that are members of figGroup

3089969 Unable to create a group array for MPPs using the Copy command

3089886 Single cell matrix should have all the X pins connected only to X pins of the other cell instances

3089501 Improve the message that is printed when the 'ade_e.scs' file is not created

3088239 Allow a locked technology constraint group to be used as constraint group for netclass in the Routing Constraint Manager

3087482 sp analysis netlists incorrectly if diffsprobe is not in the top-level schematic

3086880 Performance issues observed while opening or closing a maestro cellview with a huge number of histories

3086800 iPegasus does not use the correct area limit in free mode

3085320 Specified master cannot be selected when using the 'Select By Property' option

3085305 Specified net name cannot be selected when using the 'Select By Property' option

3084880 Air gap in design creates an uneditable entry in Stack Editor

3084601 Do not display swept parameters in the Dc Mismatch Summary form

3084518 When synchronizing layout or schematic with the design intent at the top-level, the old design intent is not removed

3084461 Autogenerated WSPs on M2 have no color mask information when creating several types of analog cells

3084145 Performance improvement of the Check and Save operation in Text Editor

3083932 Adding a group array interactively to a figGroup is not working as expected

3083724 Changing the active pattern using the Track Pattern assistant does not refresh the snap pattern drawn in the design

3083181 APR Router is not closing M0 connections in analog routing rings

3083105 Virtuoso SystemVerilog Netlister fails when the netlist.oa file is not created

3082761 The lxDummy property is not added when dummy devices are generated

3082111 The advanced Tie Shield command remains incomplete due to unconnected nets

3082015 When creating M0 WSPs, no tracks are generated on the overlaps in the M0 local regions

3081623 Label name cannot be added to the library name in the IP export flow for the runsv command

3080918 When using the Current pattern preset, the spacing set in the Property Editor is reset to 0

3080754 Guard ring is generated without nets and unable to connect to power ground mesh wire

3079913 Multi-cell migration maps instance to wrong library

3079439 Name of history zip file is created with a space

3079424 Voltus-XFi cannot find the syntax error in the config options for the Custom EM Plug-in flow

3078964 actime is grayed out in the Transient Options form when there are multiple test and AMS simulator is used

3078677 XStream In is showing errors for a zero-length line object

3076399 A PBSR restart simulation creates a global variable that is reused for every subsequent restart simulation

3075277 Device Router creates invalid hierarchical connection violations

3075179 The drGetDataFormatEntryForPattern SKILL function is not working as expected

3074321 Group array generation fails when an unsavable ruler is selected

3073967 Pattern names of resistor devices are not saved to csv files

3072280 In MATLAB Interface, accessing AdeInfoManager gives P-code related warning

3071604 LVS binder option should flatten the hierarchy instead of creating transparent instances

3070796 The SystemVerilog editor has an increased extraction time due to multiple UPF text views

3070399 In multi-cell migration, the Results browser cannot be used when temporary libraries are removed

3070364 False error flagged for minLargeViaArrayCutSpacing

3070199 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3068069 Unexpected minSpacing error in the Pin Accessibility Checker result

3066756 Remove new line characters from the Model Library and Simulation Files Setup forms

3066196 With 'onHistoryNameCollision' set to IncrementAsNew, automatic history item numbering is not done for custom-named Explorer runs

3059244 SINAD is not correctly calculated for a two-tone signal

3058153 When tandem shielding with layers minWidth, tandemWidth on the Constraint Manager should display 'no value' instead of 0

3057884 ocnxlOutputExpr not working when the output expression contains a variable

3052017 License error occurs when emirutil report=[text] is specified with emirutil autorun=[true]

3050966 Virtuoso Studio becomes unresponsive when running simulations in LSCS mode

3044019 Confusing 'oppoint' options in the DC Analysis form

3043915 Custom column is copied to the Name column in Outputs tab when importing outputs from a CSV to multiple tests

3043675 The Common Centroid preset is reset to Current when there are resistor devices in a design

3041957 Auto Via assistant engine fails to report the 'Vias with no added metal' violation

3037723 Opening a maestro view takes longer than expected

3032841 One of the outputs in calcVal Wizard is grayed out in the selection set, but can be used for typing

3030541 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

3030508 Reloading waveforms changes the legends of y axis from dB to volt

3028021 Schematic bindkeys for Calculator are not working

3024605 Plotting waveforms from a new run replaces previous plots even when the plotting mode is set to 'append'

3015046 For multiple simultaneous simulations, successfully run results are incorrectly shown as canceled

3013794 Min Number Cuts setting is not reflected to each via layer in Via Configuration Editor of Routing Constraint Manager

3009695 Instantiated text views can cause the pc.db file to explicitly refer a particular library

3009375 Max values of MAS are not evaluated

3006400 Alignment to ruler does not work when running edit-in-place

3006206 calcVal Lint check is not aware of the corner affinity algorithm

3003327 Job Details assistant does not show pointID in the last line of the log fil

2993704 Antenna numbers for the Metal2 layer are not present in the lef file when ExtractAntennaPinPathsOnly is set to true

2992463 Remove the 'filename' field for oppoint in DC options form

2980859 The job policy setup information is not stored in the setup state

2977175 In Virtuoso Schematic Migration, the Results browser cannot be opened after running multi-cell cleanup

2963457 Unselected items are copied by the Copy wizard into the category specified in the Add To Category field

2956218 Minimum spacing is not applied when transitioning from a vertical M3 bus to a horizontal M4 bus

2953410 Virtuoso Studio becomes unresponsive when using the Netlist and Run options in LSCS

2951733 Plotting mode settings in the Results tab and the Plotting/Printing Options form are out of sync

2950654 Virtuoso Studio exits unexpectedly while using IC23.1 ISR4

2949460 Run Plan simulation returns false errors about conflicting variable names in sweeps and corners

2942889 Fault dropping fails in case of a simulation time out error

2941377 Net tracer does not trace all shapes and incorrectly places halos during edit-in-place

2930586 sim err points stop other points from running reliability simulation in LSCS mode

2927997 Cannot plot the results of sp sprobe analysis after plotting the results of ac,sp, and hb analyses

2920662 Apply Previous does not update Pcell parameters

2634838 Provide an option to specify the views to be checked by the cross-view checks in Text Editor

2624680 calcVal fails when corners are rearranged in Virtuoso ADE Assembler

2572468 Allow overwriting of job policies for Voltus-XFi Analysis setup

2570046 The job policy configuration feature for Spectre simulation is missing in Voltus-XFi

2495946 Disable saving of the operating point information to a log file

2232078 Virtuoso RF: WHen voiding, dynamic shapes with no connectivity must not merge with dynamic shapes with connectivity

2117025 Support calcVal with MAS in run plan

1900688 Incorrect view is checked by cross-view checks in Text Editor

March 2025

Cadence Virtuoso Studio leverages 30 years of industry knowledge and leadership in custom/analog design to give you broader support for systems, including RF, mixed-signal, photonics, and advanced heterogeneous designs. Innovative artificial intelligence (AI) techniques, cloud enablement, infrastructure improvements, and integration across Cadence products complement these design flows, creating a hub for efficiently delivering real designs for the real world.

Virtuoso Studio: Custom Design for the Real World

The analog design world we know is evolving. And so is Virtuoso technology. Learn how the best analog tools just got better to help you keep pace with your challenging design issues. The AI-powered Virtuoso Studio custom design solution provides innovative features, reimagined infrastructure for unrivaled productivity, and new levels of integration that stretch beyond classic design boundaries.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare.

Owner: Cadence Design Systems, Inc.

Product Name: Virtuoso Studio

Version: IC23.10.130 hotfix

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

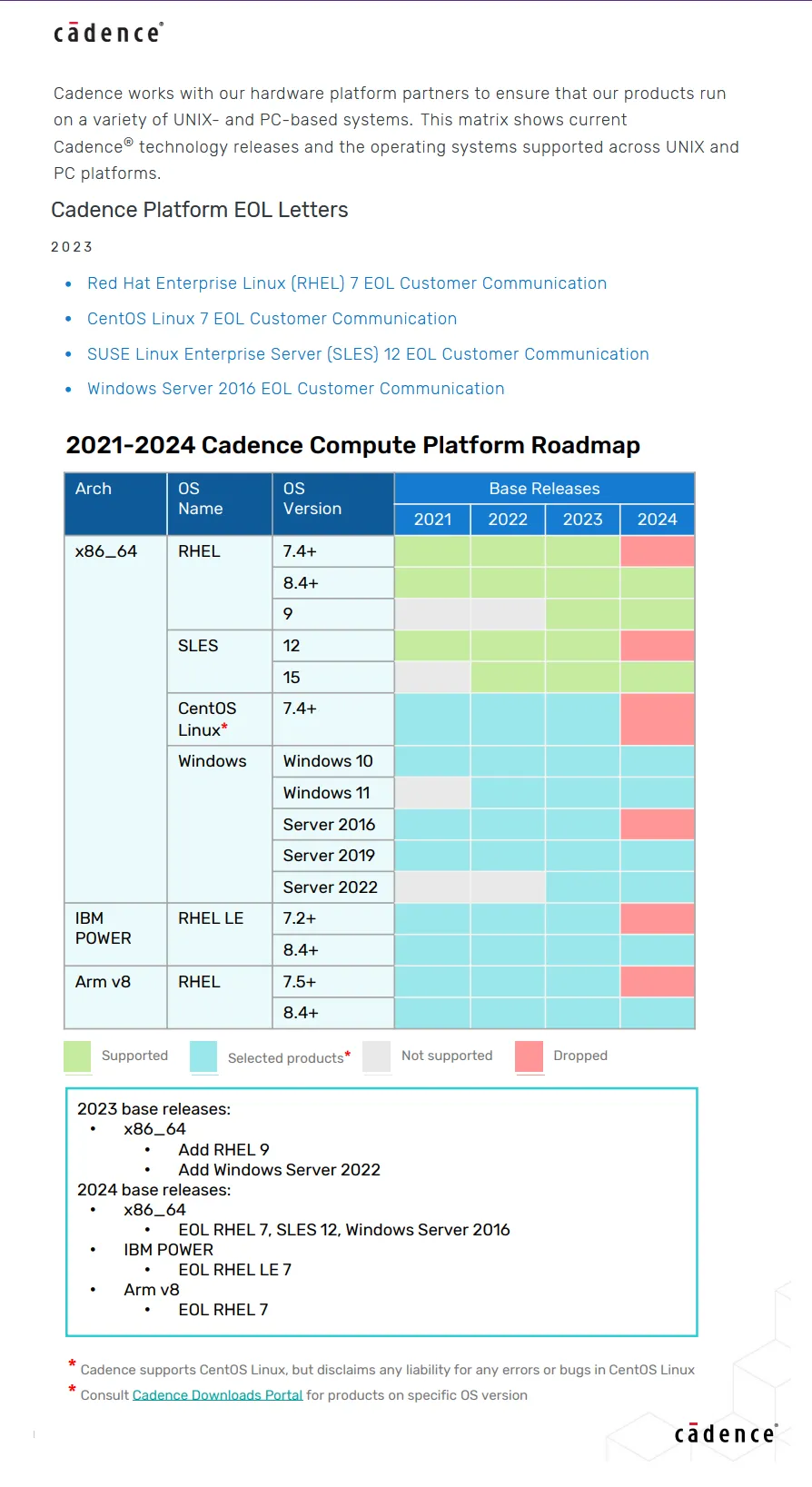

System Requirements: Linux *

Software Prerequisites: pre-installed Virtuoso Studio IC23.10.000 and above

Size: 12.1 Gb

Cadence Virtuoso Studio IC23.10.110

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please