Cadence Virtuoso Studio IC23.10.110 | 25.5 Gb

Cadence Design Systems, Inc. announced the new Cadence Virtuoso Studio IC23.10.110, a next-generation custom design platform that delivers an optimal design experience and ushers in the future for custom analog design.

Cadence Unleashes the Future of Analog, Custom and RFIC Design with Pioneering AI-Powered Virtuoso Studio

Highlights:

- Industry’s leading platform for creating differentiated custom silicon delivers unmatched productivity benefits with new generative AI technology

- Virtuoso Studio empowers designers to push semiconductor and 3D-IC design boundaries by seamless integration with Cadence’s cutting-edge technologies and modern infrastructure

- Leverages 30 years of industry leadership for all process technologies enabling 3X productivity improvement for today’s largest designs that will shape the world of tomorrow

Virtuoso Studio features a reimagined infrastructure with a unique approach to managing design processes and allows more than a 3X improvement in design throughput for today’s largest designs, enabling customers to meet aggressive time-to-market goals.

Virtuoso Studio addresses the challenges customers face with larger, more complex designs, empowering them to analyze and verify designs to ensure that design intent is maintained throughout the design cycle. This new platform features seamless integration with other Cadence solutions, including the Cadence Spectre Simulation Platform, Cadence Allegro PCB Design and Cadence Pegasus Verification System, removing traditional barriers between different design domains and speeding design closure. Virtuoso Studio is newly integrated with the AWR® Microwave Office solution, and the Pegasus Design Rule Check (DRC) Solution and Layout Versus Schematic (LVS) Solution are now available from within the Virtuoso Layout Suite. These provide advanced mmWave design and interactive signoff quality analysis during layout creation. Additionally, customers can access the Spectre Simulation Platform, including the Spectre X Simulator and Spectre FX Simulator, through Virtuoso Studio, which allows for the analysis of the industry’s largest analog and mixed-signal designs.

The new Virtuoso Studio platform offers customers the same great experience they are accustomed to, with the following benefits to address growing complexity:

- Proven Solution: Virtuoso Studio continues to offer the secure, proven solutions that industry-leading companies and foundries have trusted for 30 years for their analog, RFIC and mixed-signal designs.

- Improved Productivity: Design teams can leverage comprehensive planar and FinFET-based layout placement automation and new routing solutions to improve engineering productivity.

- Cloud-Ready: Virtuoso Studio offers massively scalable, cloud-ready solutions for occurrences when hundreds of simulations turn into thousands. It is optimized for customers’ preferred cloud providers or ready for private cloud deployment.

- Generative AI for Design Migration: The foundry-supported solutions ease the burden of process migration for schematics and layouts. Tools within the Virtuoso ADE Suite quickly re-center and validate designs post-migration, so customers can achieve aggressive time-to-market goals. Customers can utilize the AI-enabled tools to take existing IP and transform it for their next-generation designs.

- 3D-IC Integration: Virtuoso Studio allows the heterogeneous integration of 2.5D and 3D designs for advanced nodes, analog/RF packaging/modules and photonics systems.

Virtuoso Studio stays at the forefront of delivering designs accurately and on time through innovative improvements in traditional custom design tools. The new Design Space Optimization feature lets customers utilize AI algorithms to navigate competing specifications and aid in design centering, particularly after the process migration of a design. Customers can experience faster interactive editing in both the layout and schematic tools, thanks to optimized code and algorithms, while multi-threading accelerates rendering, connectivity extraction and design rule checks in parallel. Additionally, the Cadence Spectre FMC Analysis is integrated into Virtuoso Studio and provides a complete machine learning (ML)-based Monte Carlo variation solution to deliver a 3-to-6-sigma yield with orders of magnitude speedup over brute force Monte Carlo analysis.

CCR

Number TITLE

3074890 The Detail-Transpose view shows 'eval err', but the Detail view does not

3072477 The Detail-Transpose view shows 'eval err', but the Detail view does not

3070717 Virtuoso Studio exits unexpectedly when resolving a non-matching instance name in an R constraint

3069319 Yield view shows 0 yield after simulation

3066932 The colored metal placed as a background cellview is not showing the color in IC23.1 ISR9

3057993 Virtuoso Studio exits unexpectedly due to an AMS netlisting issue

3055640 Enable the Heat Sink option in GUI

3055516 Voltus-XFi template does not support Real Time SHE

3055193 Auto Twig not connecting with gate and drain terminals in a customer cell view

3054627 High memory consumption for gzip files

3054130 Virtuoso Studio exits unexpectedly when modifying a model file

3053481 lceAddSimpleStopLayers does not work as expected

3052698 Virtuoso Studio exits unexpectedly when changing the direction of symbol pin after copying pin to another symbol view

3052364 mergedViaCornerToCornerSpacing and includeOverlapNeighbors failures for some testcases

3052288 signal SIGTERM received when using custom eval trigger function in LSCS mode

3052046 AGILE abstract generator fails with Error (IAG-910229) and blank log file when run in container environment

3051788 EM-IR simulation fails when maestro view uses a corner name that begins with a number

3051530 Slotting vias takes into account excluded layers in the sltShapeConsecutiveSlotting SKILL API

3050981 Assisted Export: small coordinates error due to the number of decimals/digits limitations in SKILL

3050968 Net merging issue in HSpice netlist

3050031 Resizing of columns for the Detail-Transpose view is not working as expected

3049508 Automated Placement and Device Routing is unable to complete M0 route when M0 I/O pin is on instTerms

3049014 Virtuoso Studio exits unexpectedly during hierarchical flattening

3048897 Existing Pegasus svdb data used for Quantus when Pegasus run is impacted due to a job policy issue

3047959 _wspRefreshPatternFamilyFormOnWindowNumChange displays an error when errsetTrace is enabled

3047849 Horizontal cut direction for gate is not created during the creation of auto twigs using SDR

3047301 Auto Via fails to create stack for metal with multiple minLength definitions in the technology file

3046664 Partial Select does not allow groups to be selected when mouse is over an instance or Pcell

3045948 The chdir command errors out due to lack of user permissions

3045762 lceAddSimpleStopLayers does not work as expected

3045724 The vdrCheckVoltageLabels SKILL function reports invalid errors when minV and maxV labels have same XY coordinates

3044483 Cannot find a setup database entry for a handle

3043926 Datasets created from cells with view name other than 'schematic' are not visible in the VDR Dataset form

3043650 Resistors are removed from clustered pattern presets when their aspect ratio is reduced to very low values in the Array Assistant

3043645 parameter description error for xfgrRules

3043423 Router fails due to the Generate Spines option 'Skip pins on non-spine-adjacent layers'

3043172 Voltus-XFi errors out if the LVS run name does not match the DUT name

3042880 The enhanced shield router does not generate shields

3042645 Creating a degenerate block-override terminal results in an oaModBusTerm that has an invisible bit in the block domain

3042544 Auto Via enclosure computation issue with chamfered shapes

3042498 Virtuoso iQuantus Insight license checked out unnecessarily when running a simulation in Virtuoso ADE Assembler

3041592 Fields in the LRP text report are not properly indented

3040428 Empty subcircuit and instance statement should not be printed in the CDL netlist

3040288 Changes in schematic cause the Netlister to change the port order for Smart View instantiation, giving wrong simulation results

3040032 Generation of input.sqldb from input.tmideg0.xml errors out

3039680 The current limit for RMS J/JMAX is displayed incorrectly in the Results Browser and does not match the text report

3039652 The current (I) column for ACPeak J/JMAX in the Results Browser displays RMS current instead of peak AC current

3039515 Running the Auto Place and Route incremental placer does not yield an optimized area

3039401 Changing checkHierCloseErrorViews environment variable in same session causes incorrect behavior

3039234 Virtuoso Studio exits unexpectedly when using CCS_AttachPortAs*() with sec_port_attach_as.ils

3038914 The input.rpt_em file unexpectedly contains an empty section labeled _CDNS_MMSIM_INSTANCE_PHY

3038889 Netlisting error occurs when using ideal switches in analog library with AMS simulator

3038748 The bw_sel variable returns unexpected value in the netlist

3038691 Netlisting stops due to a SKILL error while formatting the devices

3038373 Hspice: not giving priority to labelled in-out in internal net merging

3038308 Ensure that a scalar net follows User-Defined Design Default (UDDD) validLayers constraint

3038190 Last Smart View instance is netlisted by order even when 'Port connection by' is set to 'name' in the AMS Options form

3038188 The via resistors show zero JouleHeatT value for Average J/JMAX SHE in GUI but sh_avg.txt report shows non-zero values

3037521 Due to a performance issue, device router is stuck at OpenAccess post fixer

3037465 Incorrect index is returned when cv~>memInsts is used for a mosaic

3036933 An error appears when merging the input and ground nets during CDL netlisting

3036109 Setting the variable hnlProcessDifferentPmAndInstTerminalRepresentation=t changes the default way of the expansion of the bus terminals

3035707 Wrong value of the Overhang parameter is listed in Tandem Shield Options form of Routing Constraint Manager

3035657 Custom Python script errors out due to change in the get_net_summary API

3035655 Incorrect behavior observed during the synchronous copy of a subcell into a hierarchical synchronous family

3035256 Auto Via should prevent placing shifted smaller cuts for fail case when the "Alternate Vias" option is off

3035062 IC23.1 ISR6-ISR9: Cannot find oaPath shape on some wirebonds

3034880 Virtuoso Studio exits unexpectedly if the hyperparameter property starts with a number

3034866 Virtuoso Studio exits unexpectedly if the hyperparameter property contains a '.'

3034535 The 'Supply Value/Net' column in Interface Element (IE) Setup form is editable even for UCM

3033625 EM Calculator calculates wrong current limits for via layers for a specific testcase

3032405 Netlisting jobs are pending

3030071 Virtuoso-Celsius gives incorrect layer stackup versus qrcTechFile

3029509 drdGetMinSpanLengthSpacing returns inconsistent value with respect to DRD

3028741 The automatic backtracing stops responding during the switch_function extraction

3027163 The SFE-23 error message appears during AMS netlisting

3026649 Virtuoso Studio exits unexpectedly while running the dbSave SKILL function without enabling the GUI

3025223 maeSetSetup incorrectly returns t when the function is not successful

3022201 Switch function is missing a switch pin in automatic backtracing mode

3021985 Tungsten view does not show SHE mode as Real Time

3019978 Playback expressions are not evaluated when the 'Save Simulation Data' command is inactivated

3018399 Device Router Pin to Trunk routing is unable to create direct route to multiple aligned instPins

3016591 Allow values with 3 decimal digits while editing the port connection X and Y coordinates in Electromagnetic Solver assistant

3010645 The Shield constraint checker in Routing Constraint Manager flagged unshielded area violation on hierarchical shielding

3008261 Evaluation of a variable value is not working as expected

3008151 Device router is unable to extend the tying to shield lines of adjacent net

3005303 Allow values with 3 decimal digits while editing the port connection X and Y coordinates in Electromagnetic Solver assistant

2999083 Design variables are missing from the Reliability Analysis Editor form when opened from a run plan

2998173 The Routability check in Chip Assembly reports blocked pin for metal shape covered by a pin shape and on the same layer as the pin figure

2994076 The schematic view of the lower hierarchy where the snapshot was taken remains open

2991021 Enablement flow: Import fails to create additional pins when importing into an existing library

2991009 Improve handling of constraints on unreferenced objects

2963375 Pcell subcircuit definition cannot be created due to the same name of the subcircuit

2951323 Improve error handling for hbsp form if used port cannot be found

2932947 Dummy stack devices added using the Array Assistant do not match their neighboring devices

2929950 Spaces at the beginning or end in the name of an implementation set should be disallowed

2910151 Create Pin From Label does not work as expected with VPLGens in Whole Shape mode

2909558 Create Pin From Label does not generate pins as expected at certain locations

2897813 calcVal lint check does not work when the ?historyName argument is used

2894419 Support external HDL settings when using Virtuoso SystemVerilog Netlister

2883883 Design variable distributions are not honored when Monte Carlo distributions are explicitly defined

2869675 Cellviews cannot be updated using ccpDmRename because the function is attempting the update before checking out the cellviews

2798428 The Plot button acts as a toggle button for Smith charts

2749456 Auto Via does not work when there is a shape with purpose "all" in the layout

2729229 Delay in the display of context menu when an output is right-clicked in the Results tab

2718391 While creating autovia, an internal error is reported for certain blocks

2687832 Cellviews cannot be updated using ccpDmRename because the function is attempting the update before checking out the cellviews

2658964 Add is_isolated attribute only when all the connected nodes are connected to isolation cells

1946019 Virtuoso Studio exits unexpectedly during check and save

1754482 Virtuoso Power Manger reports an error when the wildcard match is not supported

November 2024

Cadence Virtuoso Studio leverages 30 years of industry knowledge and leadership in custom/analog design to give you broader support for systems, including RF, mixed-signal, photonics, and advanced heterogeneous designs. Innovative artificial intelligence (AI) techniques, cloud enablement, infrastructure improvements, and integration across Cadence products complement these design flows, creating a hub for efficiently delivering real designs for the real world.

Virtuoso Studio: Custom Design for the Real World

The analog design world we know is evolving. And so is Virtuoso technology. Learn how the best analog tools just got better to help you keep pace with your challenging design issues. The AI-powered Virtuoso Studio custom design solution provides innovative features, reimagined infrastructure for unrivaled productivity, and new levels of integration that stretch beyond classic design boundaries.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare.

Owner: Cadence Design Systems, Inc.

Product Name: Virtuoso Studio

Version: IC23.10.110 *

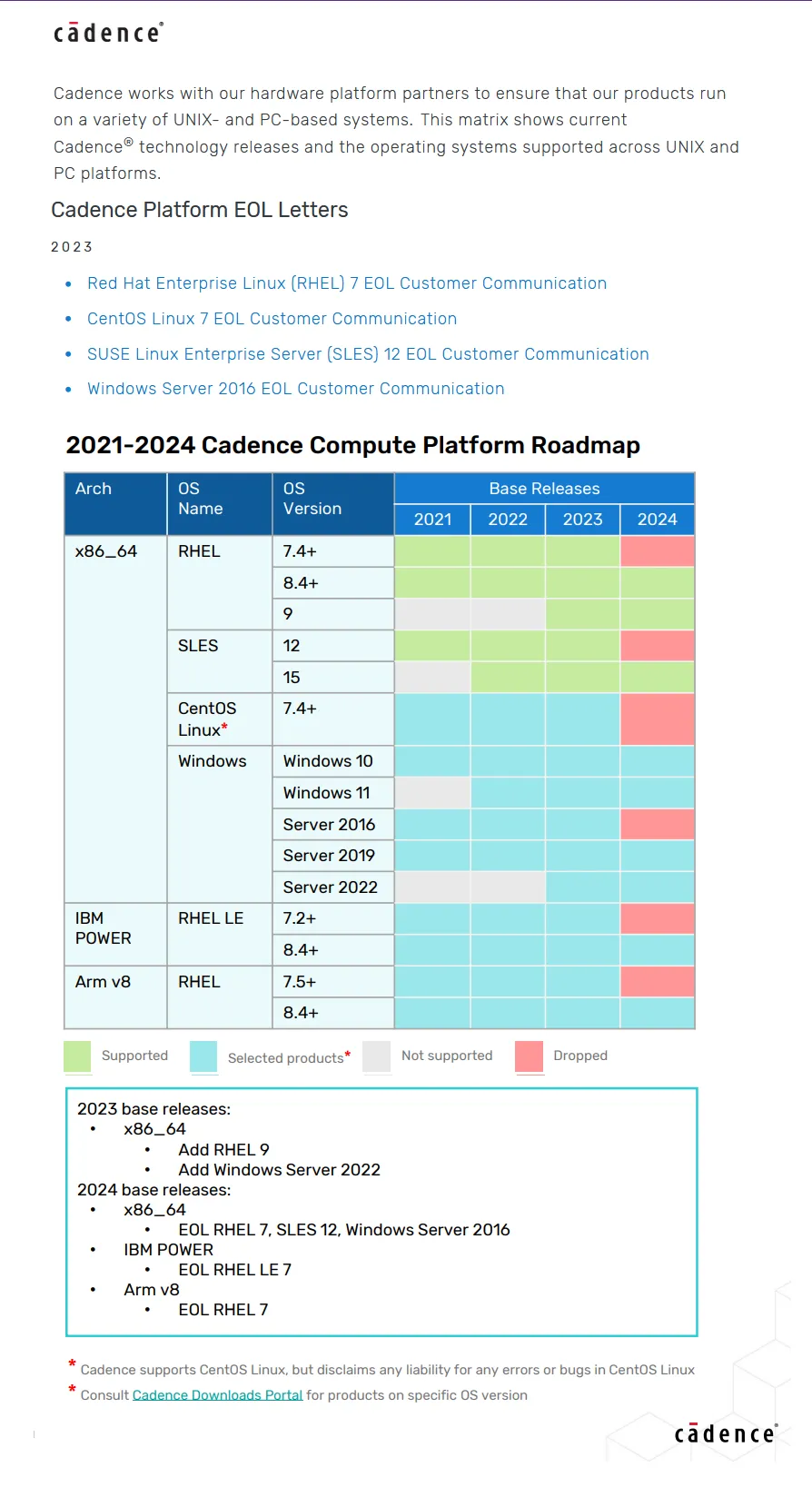

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux **

Size: 25.5 Gb

Base_IC23.10.000_lnx86.tar

Hotfix_IC23.10.110_lnx86.tar

Hotfix_IC23.10.110_lnx86.tar

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please