Cadence Virtuoso Studio IC23.10.000 | 13.2 Gb

Cadence Design Systems, Inc. announced the new Cadence Virtuoso Studio IC23.10.000, a next-generation custom design platform that delivers an optimal design experience and ushers in the future for custom analog design.

Cadence Unleashes the Future of Analog, Custom and RFIC Design with Pioneering AI-Powered Virtuoso Studio

Highlights:

- Industry’s leading platform for creating differentiated custom silicon delivers unmatched productivity benefits with new generative AI technology

- Virtuoso Studio empowers designers to push semiconductor and 3D-IC design boundaries by seamless integration with Cadence’s cutting-edge technologies and modern infrastructure

- Leverages 30 years of industry leadership for all process technologies enabling 3X productivity improvement for today’s largest designs that will shape the world of tomorrow

Virtuoso Studio features a reimagined infrastructure with a unique approach to managing design processes and allows more than a 3X improvement in design throughput for today’s largest designs, enabling customers to meet aggressive time-to-market goals.

Virtuoso Studio addresses the challenges customers face with larger, more complex designs, empowering them to analyze and verify designs to ensure that design intent is maintained throughout the design cycle. This new platform features seamless integration with other Cadence solutions, including the Cadence Spectre Simulation Platform, Cadence Allegro PCB Design and Cadence Pegasus Verification System, removing traditional barriers between different design domains and speeding design closure. Virtuoso Studio is newly integrated with the AWR® Microwave Office solution, and the Pegasus Design Rule Check (DRC) Solution and Layout Versus Schematic (LVS) Solution are now available from within the Virtuoso Layout Suite. These provide advanced mmWave design and interactive signoff quality analysis during layout creation. Additionally, customers can access the Spectre Simulation Platform, including the Spectre X Simulator and Spectre FX Simulator, through Virtuoso Studio, which allows for the analysis of the industry’s largest analog and mixed-signal designs.

The new Virtuoso Studio platform offers customers the same great experience they are accustomed to, with the following benefits to address growing complexity:

- Proven Solution: Virtuoso Studio continues to offer the secure, proven solutions that industry-leading companies and foundries have trusted for 30 years for their analog, RFIC and mixed-signal designs.

- Improved Productivity: Design teams can leverage comprehensive planar and FinFET-based layout placement automation and new routing solutions to improve engineering productivity.

- Cloud-Ready: Virtuoso Studio offers massively scalable, cloud-ready solutions for occurrences when hundreds of simulations turn into thousands. It is optimized for customers’ preferred cloud providers or ready for private cloud deployment.

- Generative AI for Design Migration: The foundry-supported solutions ease the burden of process migration for schematics and layouts. Tools within the Virtuoso ADE Suite quickly re-center and validate designs post-migration, so customers can achieve aggressive time-to-market goals. Customers can utilize the AI-enabled tools to take existing IP and transform it for their next-generation designs.

- 3D-IC Integration: Virtuoso Studio allows the heterogeneous integration of 2.5D and 3D designs for advanced nodes, analog/RF packaging/modules and photonics systems.

Virtuoso Studio stays at the forefront of delivering designs accurately and on time through innovative improvements in traditional custom design tools. The new Design Space Optimization feature lets customers utilize AI algorithms to navigate competing specifications and aid in design centering, particularly after the process migration of a design. Customers can experience faster interactive editing in both the layout and schematic tools, thanks to optimized code and algorithms, while multi-threading accelerates rendering, connectivity extraction and design rule checks in parallel. Additionally, the Cadence Spectre FMC Analysis is integrated into Virtuoso Studio and provides a complete machine learning (ML)-based Monte Carlo variation solution to deliver a 3-to-6-sigma yield with orders of magnitude speedup over brute force Monte Carlo analysis.

Note: This CCR list represents those CCRs that were first addressed in the IC23.1 BASE release.

If you would like to see a full list of the CCRs addressed between the previous BASE releases (IC6.1.8 and/or ICADVM20.1) then refer to the IC6.1.8 ISR32 or ICADVM20.1 ISR32 README file. IC618/20.1 ISR32 being the last ISR before the IC23.1 BASE release.

==============================================================================

CCR

Number TITLE

2825198 In a maestro setup with aging simulation, job submission takes ~7-10 minutes

2820494 ADE Assembler incorrectly stops all simulation jobs even if No is clicked on error message Assembler-1970

2817821 Virtuoso Studio exits unexpectedly when running different methods of Monte Carlo simulation

2815433 Remove duplicate reports of sim errors from simulation job to ensure an accurate remaining sim count in the parent Virtuoso Studio process

2812604 Virtuoso Studio exits unexpectedly while using the context menu for the 'Add Pin on Different Purposes' option in the Pin browser

2807596 RAVEL errors not showing correctly in the Annotation Browser

2807265 Misaligned stacked vias effects QoR in customer data

2806323 Wire creation behavior not as expected when Virtuoso Studio runs in nograph mode

2806300 Virtuoso Studio exits unexpectedly using different technology libraries during create instance

2805872 Virtuoso Studio exits unexpectedly after attaching a technology library

2805384 check_length fails to include via metal in reporting

2805037 Issue with stacked via when shield enclosure is set to center or half

2802231 Quick Align in Partial selection mode makes unintended stretch

2801784 The Health Monitor form is not getting displayed as expected when using options from a pinned toolbox

2801531 Cannot open the Choosing Analyses form after a successful transient noise simulation

2801239 Importing global variables with large number of sweep points returns errors

2800564 Virtuoso Studio exits unexpectedly while using the Copy Route feature

2800493 phoWayPointConnector errors out due to missing LPP definition in the technology file

2800429 Fix an issue in calcVal debugging

2800233 EAE labeling fails for net separator device

2799656 If the computers running the simulation jobs are not reachable, the jobs appear halted in the UI

2799104 Capture and Replay unable to save due to directory with no write permissions

2798988 In remote operations, retry to get a good results database handle if the one returned is invalid

2798463 libImport exits unexpectedly with assertion failures

2798132 Array Assistant Aspect Ratio column is not working as expected in Virtuoso Layout Suite XL

2797523 Expression evaluator should not be blocked by pop-up windows

2795776 Check if RAVEL files exist at the start of a DRC run

2794010 Incorrect net names for faults in AMS simulation result in Spectre warnings

2793500 Some nets are missing when using the 'Only show failing nets' button in Voltus-Fi GUI

2793306 Virtuoso Studio incorrectly requests for Voltus_Xfi_Cockpit instead of Voltus_XFi_Cockpit

2792338 In LSCS mode, results evaluation was canceled after a Monte Carlo simulation with a custom simulator

2792329 calcVal issue with corner name mismatch

2791799 When non-schematic views are used, instances or nets not found in source design show an error in the EM Solver assistant

2791665 Canceling points results in idle jobs until the entire run completes

2791454 Cannot switch focus from a form to a window when using Virtuoso Layout Suite and Virtuoso Schematics XL

2790433 Use of VAR in transient dynamic parameter works only for parameters, not for parametric sets

2789337 Opening a layout resizes the Command Interpreter Window

2789269 inniopCheckDesignDb errors out, reporting too few arguments

2788537 Expressions using string values of the design variables set by the pre-run ocnxlUpdatePointVariable function are evaluated incorrectly

2788083 Auto twigs to honor trim shapes existing in the design to avoid creating a violation during interactive routingВ

2787707 Qt warning messages are getting displayed when launching Virtuoso Studio

2787553 Assisted Export does not update net routing resulting in an open net

2787461 Segmentation fault occurs by new shield routing with multiple net selection for a customer design

2786896 In the automated device placement and routing flow, a highlight dummy box does not disappear when the layout is re-initialized

2786416 maestro cellview does not always reconnect to a running simulation when repeatedly closed and reopened

2786244 LSCS jobs are stuck in the 'simulation finished' state; job log shows repeated LifeMonitor::run messages

2785399 Shorts created by tie shield

2783647 Incorrect netlist is generated after replacing vsource with vpulse

2783431 The Cover Pin option in simulation-driven interactive routing does not cover the pin completely

2783316 The previously selected instances are removed when the Specify Instances for Monte Carlo form is reopened

2782508 Virtuoso Studio exits unexpectedly during Create probe when expand.cfg instance rule does not specify library name

2779726 Create wire does not consider overridden width value from Wire Assistant with layer-purpose drawing1

2779598 Simulation SPEF attachment failure and false attachment warning

2777681 Shorts reported for trim insertion in Auto Place and Route flow

2776879 Automatically stop all pending jobs if there are idle jobs and no pending tasks

2776553 Errors reported when testing dummy fill enhancements in the automated device placement and routing flow

2776458 XL Status column is not enabled by default in Nets section of the Navigator assistant

2775580 Incomplete shielding performed while preferring constraints over finishing and setting shielding as the highest net order priorityВ

2768334 Unable to edit layer name in the Property Editor form

2767426 ADE Explorer: Parametric sweep runs despite disabling individual parameters in parametric set

2766892 Virtuoso Studio exits unexpectedly after changing eval type to 'all' and re-evaluating the results of a previous session

2766891 Auto-inference jobs not ended after the pre-existing parasitic file attached to simulation are detected

2766783 phoDrawBendConnectorSymbol fails for 'odd' magnification values

2766288 Error occurs when Layout XL Probe is used to track a net connection

2766258 Automated routing creates endOfLineKeepout, minStepEdgeLength, and minClusterSpacing violations

2765134 EOP Issue - When toggling visibility of a CDF parameter in layout CDF the prompt moves to the bottom and appears to be missing

2763835 Nets remain highlighted when clicked for the second time during output setup, although they are unselected

2762598 Local sweep values not displayed in the Results tab

2761855 Variables in specifications are not working when the variable is swept

2761569 UserDV shape generation reports shorts on resistor and capacitor nets

2761496 Simulation jobs stay in the job queue even when the simulations are complete

2761206 The Save button in ADE Explorer becomes inactive after the managed symbol is checked in

2760466 Add error handling for empty data files in DSPF parsing, training, and inference

2759868 ADE Assembler suddenly becomes slow after the simulation of 10000 points is done

2759439 Voltus-Fi Violation Browser does not limit element count

2759352 When one of the gates in a dummy instance is connected to a net, Extract Layout generates false opens

2758557 Connectivity generation fails with SKILL stack trace

2757801 Virtuoso Visualization and Analysis XL Calculator stops responding after selecting multiple nets from the schematic

2757287 CDF value set by callback is not saved for non-visible parameters when multiple instances are selected on layout

2754065 Automated device-level routing is creating minSideSpacing and minViaSpacing DRC errors due to multi-cuts

2753935 OSSHNL-393 is reported incorrectly if the instance is named 'dummy'

2753637 Batch Checker does not check inside via

2753145 Support Auto-Twig mesh routing targeting M0 pre-routing inside Modgens

2753000 The IO Planner is enhanced to change the width of the site definitions to abut rows during IO row creation

2751970 Unable to generate shielding when the minWidth is not the same as the WSP width

2751767 Virtuoso Studio exits unexpectedly when using variable bus width SystemVerilog/VerilogA Pcell

2751515 Automated placement and routing fill cell fails with an error in one of the user cells and the cell does not contain row region

2751139 The shield router in Virtuoso Studio generates over-extension tandemShield

2750587 Need performance improvement for shield creation

2749621 There is no via tied to shielding nets (in_p/in_m)

2749618 No tie shield inserted when enabled blockage insertion

2748574 ML_PAREST menu should be implemented as a regular drop-down

2748571 Option to suppress training and inference error messages

2748569 Batch inference needs progress indicator and a finishing message

2748566 All reports should include design or model name to avoid overwriting

2748552 CLI commands should check for valid paths in arguments and create them if they do not exist

2748551 Automatically created maestro views should be deleted after inference completes

2748000 Incorrect calculation of row height for certain devices in the automated device placement and routing flow

2747438 Running incremental placement generates overlaps between Modgens in the automated device placement and routing flow

2747307 Shorts reported for trim insertion in Auto Place and Route flow

2747071 Pin tool displays bus pins difference when switched between the 'Collapse Selected Bus' and 'Expand Selected Bus' modes

2745809 SPEF file attachment failure with simulation and false attachment warning

2745542 Virtuoso Studio exits unexpectedly when routing tandemsplit shielding with the new shield router

2744708 Track Pattern Assistant is not refreshing/updating Row Region template name when the user switches to others in current cell view

2744677 Unable to start Virtuoso Studio on SLES12 in IC23.1

2744222 Add an option to stop child batch runs if the parent run is closed

2743861 Reference Schematic/Symbol View For Inherited Connections' field is disabled if Virtuoso Schematic Editor XL license is missing

2743704 calcVal fails with 'unbound variable' when used for waveform in context of S-parameter data

2741313 Cannot tap metal inside unselectable via but can tap an unselectable pathSeg

2737226 Unable to plot results if the history name is changed to keep it same as the test name

2734757 Virtuoso Studio stops responding after a few hundred jobs are run in ADE Assembler

2734471 SiP-DRC runs in SiP_DRC/RAVEL flow even if it was not selected for running

2734144 Callback fails to assign value corresponding to a cyclic field when more than one instance is selected

2732622 Pin dimensions cannot be modified when a pin placed under the Pin Placer is moved to Top-level route mode

2732611 PIN_ON_ROUTE property prevents pin placement in Top Level Route mode

2732392 SQL errors and performance issues observed after a right-click in the Results tab for EMIR with assert checks

2730180 Virtuoso ADE Assembler stops responding when in MPS loop with MATLAB

2726678 SIGEPE error when using placer in Auto Device Place and Route flow

2725889 Shield intersection not being completed

2719750 Warning message while running Oasis

2718699 Add Length criteria to Find/Replace form when searching for path and pathSeg

2718697 Add criteria to Find/Replace form when searching for Rectangle

2718004 Virtuoso RF Solution LVS-Driven flow: Disable loading of default via clustering settings

2714693 Query marker message field is very small

2713487 APR.stdcell.route separateStdCellLibs is not adding libraries to the reference library list for placement and routing

2711609 Output patterns do not exist in input patterns

2711434 LVS issue after running the router in automated place and route flow

2708753 During automated place and route flow evaluation, DRC violations reported

2706406 tandemSplitNearby does not seem to work as expected and the side shield nets are created for all wire segments

2705204 Shield Checker flags a violation if minWidth is not the same as the one with the drawn layout

2705033 Virtuoso Studio stops responding after netlist creation for a top-level MTS block

2703599 OA 22.61 not running on CentOS7

2703170 The pass/fail filter in ADE Assembler is not working properly with big databases

2701718 Reference Schematic/Symbol View For Inherited Connections' field is disabled and checks for Virtuoso Schematic Editor XL license

2700337 Using HDL Package Setup with cdsTextTo5x adds the '-xmvlog_args -use5x' option to the exported xrunArgs file

2697326 Width Spacing Pattern generated in wrong direction

2697067 Virtuoso Studio exits unexpectedly when post-processing PSF file for noise summary results

2695005 Adjust Blocks - Pins command not working as expected

2691120 NC-Verilog netlist is different for single-bit and multi-bit when a Verilog keyword is used in port name

2689903 Incorrect yield result when Monte Carlo spec setting is from design variable

2689544 When CDS_ENABLE_EXP_PCELL=true, a non-graphical Virtuoso Studio session displays a blocking dialog box regarding PDK mismatch

2688040 SiP-DRC check should not list the differences about the Virtuoso RF Solution being supported or not

2687822 Verify Synchronization not displaying warning messages related to synchronous clone families

2684476 Ruler error message on cancel

2683232 Pcell callback to control choices of cyclic type CDF

2671359 Modgen is not showing up under the FigGroup section of the Navigator assistant

2667520 Performance issues reported during in-place editing of stack series

2666852 Fluid shapes cannot be selected when pteLppsDisplayOrderControl is ON

2664444 Request performance improvement when adding clones in Virtuoso Layout Suite XL from Virtuoso Schematic Editor

2654655 Display a message when license is checked out or released while using the вЂCreate Via – Auto’ command in layout

2649365 M1 Width Spacing Pattern is not generated according to device pins

2642312 Display is very slow when displayRulerInHierarchy option is TRUE

2636202 During Edit In Place, instance transform is not applied for zoom to selected

2636093 Lag while editing a layout due to updates to Stretch toolbar

2625420 Duplicate category in Pcell Xor list window

2607038 Virtuoso Studio exits unexpectedly when opening Calibre PEX created schematic in edit mode

2586758 ADE Verifier license usage during batch run not working as expected

2571258 Using variables in specification not working in case of Monte Carlo with variable sweep

2568603 Virtuoso Schematic Editor XL is very slow with large bus bit pins

2565009 M1 Width Spacing Pattern pitch is not matched to the Row template height

2559160 Virtuoso Studio slow performance on large layout, with zoom, pan, fit view

2556335 Voltus-Fi-XL generates incorrect report if 'Show EM %' is enabled

2550874 Bus legend is not displayed correctly when saving the graph image with a background color other than white

2543036 Results are not updated after loading the .grf file even when the 'Reload using current context' option is enabled

2526009 Show Editable and Display Parameters filter shows non-editable parameter

2519413 Incorrect difference between schematic and layout placed parameters

2517092 Monte Carlo shows incorrect yield percentage when the setup uses variables in specification

2505491 Space in sweep parameter stops Pcell validation run

2474441 Batch Verifier and Distributed Plot should follow UHD license scheme

2474128 Virtuoso Placer in Virtuoso Layout Suite EXL cockpit requires 24 GXL tokens with mature nodes

2336834 Reference Schematic/Symbol View for Inherited Connections' field checks for Virtuoso Schematic Editor XL license

2286331 Slow to open memory array schematics in edit mode

2284060 Soft block coloring option does not work consistently when switched from Virtuoso Layout Suite XL to Virtuoso Layout Suite EXL and vice versa

2250577 In ADE Assembler, sorting of Pass/Fail is not done correctly

2126991 CDF Cyclic parameter choices are updated based on a callback but not displayed correctly

2027016 STB analysis generates an error when the output is a string variable in psfbinf format

1885564 The 'Fit Y to Visible X' command does not work as expected for the waveform filtered through the Graph - Filter By Sweep Var option

1882969 The 'Fit Y to Visible X' command does not work as expected for the waveform filtered through the Graph - Filter By Sweep Var option

1839924 The specified values are getting overwritten by the Edit Object Properties form when an instance master view is deleted

807671 Exporting a digital signal in SPECTRE format only saves x-axis values

June 2023

If you would like to see a full list of the CCRs addressed between the previous BASE releases (IC6.1.8 and/or ICADVM20.1) then refer to the IC6.1.8 ISR32 or ICADVM20.1 ISR32 README file. IC618/20.1 ISR32 being the last ISR before the IC23.1 BASE release.

==============================================================================

CCR

Number TITLE

2825198 In a maestro setup with aging simulation, job submission takes ~7-10 minutes

2820494 ADE Assembler incorrectly stops all simulation jobs even if No is clicked on error message Assembler-1970

2817821 Virtuoso Studio exits unexpectedly when running different methods of Monte Carlo simulation

2815433 Remove duplicate reports of sim errors from simulation job to ensure an accurate remaining sim count in the parent Virtuoso Studio process

2812604 Virtuoso Studio exits unexpectedly while using the context menu for the 'Add Pin on Different Purposes' option in the Pin browser

2807596 RAVEL errors not showing correctly in the Annotation Browser

2807265 Misaligned stacked vias effects QoR in customer data

2806323 Wire creation behavior not as expected when Virtuoso Studio runs in nograph mode

2806300 Virtuoso Studio exits unexpectedly using different technology libraries during create instance

2805872 Virtuoso Studio exits unexpectedly after attaching a technology library

2805384 check_length fails to include via metal in reporting

2805037 Issue with stacked via when shield enclosure is set to center or half

2802231 Quick Align in Partial selection mode makes unintended stretch

2801784 The Health Monitor form is not getting displayed as expected when using options from a pinned toolbox

2801531 Cannot open the Choosing Analyses form after a successful transient noise simulation

2801239 Importing global variables with large number of sweep points returns errors

2800564 Virtuoso Studio exits unexpectedly while using the Copy Route feature

2800493 phoWayPointConnector errors out due to missing LPP definition in the technology file

2800429 Fix an issue in calcVal debugging

2800233 EAE labeling fails for net separator device

2799656 If the computers running the simulation jobs are not reachable, the jobs appear halted in the UI

2799104 Capture and Replay unable to save due to directory with no write permissions

2798988 In remote operations, retry to get a good results database handle if the one returned is invalid

2798463 libImport exits unexpectedly with assertion failures

2798132 Array Assistant Aspect Ratio column is not working as expected in Virtuoso Layout Suite XL

2797523 Expression evaluator should not be blocked by pop-up windows

2795776 Check if RAVEL files exist at the start of a DRC run

2794010 Incorrect net names for faults in AMS simulation result in Spectre warnings

2793500 Some nets are missing when using the 'Only show failing nets' button in Voltus-Fi GUI

2793306 Virtuoso Studio incorrectly requests for Voltus_Xfi_Cockpit instead of Voltus_XFi_Cockpit

2792338 In LSCS mode, results evaluation was canceled after a Monte Carlo simulation with a custom simulator

2792329 calcVal issue with corner name mismatch

2791799 When non-schematic views are used, instances or nets not found in source design show an error in the EM Solver assistant

2791665 Canceling points results in idle jobs until the entire run completes

2791454 Cannot switch focus from a form to a window when using Virtuoso Layout Suite and Virtuoso Schematics XL

2790433 Use of VAR in transient dynamic parameter works only for parameters, not for parametric sets

2789337 Opening a layout resizes the Command Interpreter Window

2789269 inniopCheckDesignDb errors out, reporting too few arguments

2788537 Expressions using string values of the design variables set by the pre-run ocnxlUpdatePointVariable function are evaluated incorrectly

2788083 Auto twigs to honor trim shapes existing in the design to avoid creating a violation during interactive routingВ

2787707 Qt warning messages are getting displayed when launching Virtuoso Studio

2787553 Assisted Export does not update net routing resulting in an open net

2787461 Segmentation fault occurs by new shield routing with multiple net selection for a customer design

2786896 In the automated device placement and routing flow, a highlight dummy box does not disappear when the layout is re-initialized

2786416 maestro cellview does not always reconnect to a running simulation when repeatedly closed and reopened

2786244 LSCS jobs are stuck in the 'simulation finished' state; job log shows repeated LifeMonitor::run messages

2785399 Shorts created by tie shield

2783647 Incorrect netlist is generated after replacing vsource with vpulse

2783431 The Cover Pin option in simulation-driven interactive routing does not cover the pin completely

2783316 The previously selected instances are removed when the Specify Instances for Monte Carlo form is reopened

2782508 Virtuoso Studio exits unexpectedly during Create probe when expand.cfg instance rule does not specify library name

2779726 Create wire does not consider overridden width value from Wire Assistant with layer-purpose drawing1

2779598 Simulation SPEF attachment failure and false attachment warning

2777681 Shorts reported for trim insertion in Auto Place and Route flow

2776879 Automatically stop all pending jobs if there are idle jobs and no pending tasks

2776553 Errors reported when testing dummy fill enhancements in the automated device placement and routing flow

2776458 XL Status column is not enabled by default in Nets section of the Navigator assistant

2775580 Incomplete shielding performed while preferring constraints over finishing and setting shielding as the highest net order priorityВ

2768334 Unable to edit layer name in the Property Editor form

2767426 ADE Explorer: Parametric sweep runs despite disabling individual parameters in parametric set

2766892 Virtuoso Studio exits unexpectedly after changing eval type to 'all' and re-evaluating the results of a previous session

2766891 Auto-inference jobs not ended after the pre-existing parasitic file attached to simulation are detected

2766783 phoDrawBendConnectorSymbol fails for 'odd' magnification values

2766288 Error occurs when Layout XL Probe is used to track a net connection

2766258 Automated routing creates endOfLineKeepout, minStepEdgeLength, and minClusterSpacing violations

2765134 EOP Issue - When toggling visibility of a CDF parameter in layout CDF the prompt moves to the bottom and appears to be missing

2763835 Nets remain highlighted when clicked for the second time during output setup, although they are unselected

2762598 Local sweep values not displayed in the Results tab

2761855 Variables in specifications are not working when the variable is swept

2761569 UserDV shape generation reports shorts on resistor and capacitor nets

2761496 Simulation jobs stay in the job queue even when the simulations are complete

2761206 The Save button in ADE Explorer becomes inactive after the managed symbol is checked in

2760466 Add error handling for empty data files in DSPF parsing, training, and inference

2759868 ADE Assembler suddenly becomes slow after the simulation of 10000 points is done

2759439 Voltus-Fi Violation Browser does not limit element count

2759352 When one of the gates in a dummy instance is connected to a net, Extract Layout generates false opens

2758557 Connectivity generation fails with SKILL stack trace

2757801 Virtuoso Visualization and Analysis XL Calculator stops responding after selecting multiple nets from the schematic

2757287 CDF value set by callback is not saved for non-visible parameters when multiple instances are selected on layout

2754065 Automated device-level routing is creating minSideSpacing and minViaSpacing DRC errors due to multi-cuts

2753935 OSSHNL-393 is reported incorrectly if the instance is named 'dummy'

2753637 Batch Checker does not check inside via

2753145 Support Auto-Twig mesh routing targeting M0 pre-routing inside Modgens

2753000 The IO Planner is enhanced to change the width of the site definitions to abut rows during IO row creation

2751970 Unable to generate shielding when the minWidth is not the same as the WSP width

2751767 Virtuoso Studio exits unexpectedly when using variable bus width SystemVerilog/VerilogA Pcell

2751515 Automated placement and routing fill cell fails with an error in one of the user cells and the cell does not contain row region

2751139 The shield router in Virtuoso Studio generates over-extension tandemShield

2750587 Need performance improvement for shield creation

2749621 There is no via tied to shielding nets (in_p/in_m)

2749618 No tie shield inserted when enabled blockage insertion

2748574 ML_PAREST menu should be implemented as a regular drop-down

2748571 Option to suppress training and inference error messages

2748569 Batch inference needs progress indicator and a finishing message

2748566 All reports should include design or model name to avoid overwriting

2748552 CLI commands should check for valid paths in arguments and create them if they do not exist

2748551 Automatically created maestro views should be deleted after inference completes

2748000 Incorrect calculation of row height for certain devices in the automated device placement and routing flow

2747438 Running incremental placement generates overlaps between Modgens in the automated device placement and routing flow

2747307 Shorts reported for trim insertion in Auto Place and Route flow

2747071 Pin tool displays bus pins difference when switched between the 'Collapse Selected Bus' and 'Expand Selected Bus' modes

2745809 SPEF file attachment failure with simulation and false attachment warning

2745542 Virtuoso Studio exits unexpectedly when routing tandemsplit shielding with the new shield router

2744708 Track Pattern Assistant is not refreshing/updating Row Region template name when the user switches to others in current cell view

2744677 Unable to start Virtuoso Studio on SLES12 in IC23.1

2744222 Add an option to stop child batch runs if the parent run is closed

2743861 Reference Schematic/Symbol View For Inherited Connections' field is disabled if Virtuoso Schematic Editor XL license is missing

2743704 calcVal fails with 'unbound variable' when used for waveform in context of S-parameter data

2741313 Cannot tap metal inside unselectable via but can tap an unselectable pathSeg

2737226 Unable to plot results if the history name is changed to keep it same as the test name

2734757 Virtuoso Studio stops responding after a few hundred jobs are run in ADE Assembler

2734471 SiP-DRC runs in SiP_DRC/RAVEL flow even if it was not selected for running

2734144 Callback fails to assign value corresponding to a cyclic field when more than one instance is selected

2732622 Pin dimensions cannot be modified when a pin placed under the Pin Placer is moved to Top-level route mode

2732611 PIN_ON_ROUTE property prevents pin placement in Top Level Route mode

2732392 SQL errors and performance issues observed after a right-click in the Results tab for EMIR with assert checks

2730180 Virtuoso ADE Assembler stops responding when in MPS loop with MATLAB

2726678 SIGEPE error when using placer in Auto Device Place and Route flow

2725889 Shield intersection not being completed

2719750 Warning message while running Oasis

2718699 Add Length criteria to Find/Replace form when searching for path and pathSeg

2718697 Add criteria to Find/Replace form when searching for Rectangle

2718004 Virtuoso RF Solution LVS-Driven flow: Disable loading of default via clustering settings

2714693 Query marker message field is very small

2713487 APR.stdcell.route separateStdCellLibs is not adding libraries to the reference library list for placement and routing

2711609 Output patterns do not exist in input patterns

2711434 LVS issue after running the router in automated place and route flow

2708753 During automated place and route flow evaluation, DRC violations reported

2706406 tandemSplitNearby does not seem to work as expected and the side shield nets are created for all wire segments

2705204 Shield Checker flags a violation if minWidth is not the same as the one with the drawn layout

2705033 Virtuoso Studio stops responding after netlist creation for a top-level MTS block

2703599 OA 22.61 not running on CentOS7

2703170 The pass/fail filter in ADE Assembler is not working properly with big databases

2701718 Reference Schematic/Symbol View For Inherited Connections' field is disabled and checks for Virtuoso Schematic Editor XL license

2700337 Using HDL Package Setup with cdsTextTo5x adds the '-xmvlog_args -use5x' option to the exported xrunArgs file

2697326 Width Spacing Pattern generated in wrong direction

2697067 Virtuoso Studio exits unexpectedly when post-processing PSF file for noise summary results

2695005 Adjust Blocks - Pins command not working as expected

2691120 NC-Verilog netlist is different for single-bit and multi-bit when a Verilog keyword is used in port name

2689903 Incorrect yield result when Monte Carlo spec setting is from design variable

2689544 When CDS_ENABLE_EXP_PCELL=true, a non-graphical Virtuoso Studio session displays a blocking dialog box regarding PDK mismatch

2688040 SiP-DRC check should not list the differences about the Virtuoso RF Solution being supported or not

2687822 Verify Synchronization not displaying warning messages related to synchronous clone families

2684476 Ruler error message on cancel

2683232 Pcell callback to control choices of cyclic type CDF

2671359 Modgen is not showing up under the FigGroup section of the Navigator assistant

2667520 Performance issues reported during in-place editing of stack series

2666852 Fluid shapes cannot be selected when pteLppsDisplayOrderControl is ON

2664444 Request performance improvement when adding clones in Virtuoso Layout Suite XL from Virtuoso Schematic Editor

2654655 Display a message when license is checked out or released while using the вЂCreate Via – Auto’ command in layout

2649365 M1 Width Spacing Pattern is not generated according to device pins

2642312 Display is very slow when displayRulerInHierarchy option is TRUE

2636202 During Edit In Place, instance transform is not applied for zoom to selected

2636093 Lag while editing a layout due to updates to Stretch toolbar

2625420 Duplicate category in Pcell Xor list window

2607038 Virtuoso Studio exits unexpectedly when opening Calibre PEX created schematic in edit mode

2586758 ADE Verifier license usage during batch run not working as expected

2571258 Using variables in specification not working in case of Monte Carlo with variable sweep

2568603 Virtuoso Schematic Editor XL is very slow with large bus bit pins

2565009 M1 Width Spacing Pattern pitch is not matched to the Row template height

2559160 Virtuoso Studio slow performance on large layout, with zoom, pan, fit view

2556335 Voltus-Fi-XL generates incorrect report if 'Show EM %' is enabled

2550874 Bus legend is not displayed correctly when saving the graph image with a background color other than white

2543036 Results are not updated after loading the .grf file even when the 'Reload using current context' option is enabled

2526009 Show Editable and Display Parameters filter shows non-editable parameter

2519413 Incorrect difference between schematic and layout placed parameters

2517092 Monte Carlo shows incorrect yield percentage when the setup uses variables in specification

2505491 Space in sweep parameter stops Pcell validation run

2474441 Batch Verifier and Distributed Plot should follow UHD license scheme

2474128 Virtuoso Placer in Virtuoso Layout Suite EXL cockpit requires 24 GXL tokens with mature nodes

2336834 Reference Schematic/Symbol View for Inherited Connections' field checks for Virtuoso Schematic Editor XL license

2286331 Slow to open memory array schematics in edit mode

2284060 Soft block coloring option does not work consistently when switched from Virtuoso Layout Suite XL to Virtuoso Layout Suite EXL and vice versa

2250577 In ADE Assembler, sorting of Pass/Fail is not done correctly

2126991 CDF Cyclic parameter choices are updated based on a callback but not displayed correctly

2027016 STB analysis generates an error when the output is a string variable in psfbinf format

1885564 The 'Fit Y to Visible X' command does not work as expected for the waveform filtered through the Graph - Filter By Sweep Var option

1882969 The 'Fit Y to Visible X' command does not work as expected for the waveform filtered through the Graph - Filter By Sweep Var option

1839924 The specified values are getting overwritten by the Edit Object Properties form when an instance master view is deleted

807671 Exporting a digital signal in SPECTRE format only saves x-axis values

June 2023

Cadence Virtuoso Studio leverages 30 years of industry knowledge and leadership in custom/analog design to give you broader support for systems, including RF, mixed-signal, photonics, and advanced heterogeneous designs. Innovative artificial intelligence (AI) techniques, cloud enablement, infrastructure improvements, and integration across Cadence products complement these design flows, creating a hub for efficiently delivering real designs for the real world.

Virtuoso Studio: Custom Design for the Real World

The analog design world we know is evolving. And so is Virtuoso technology. Learn how the best analog tools just got better to help you keep pace with your challenging design issues. The AI-powered Virtuoso Studio custom design solution provides innovative features, reimagined infrastructure for unrivaled productivity, and new levels of integration that stretch beyond classic design boundaries.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare.

Owner: Cadence Design Systems, Inc.

Product Name: Virtuoso Studio

Version: IC23.10.000 Base

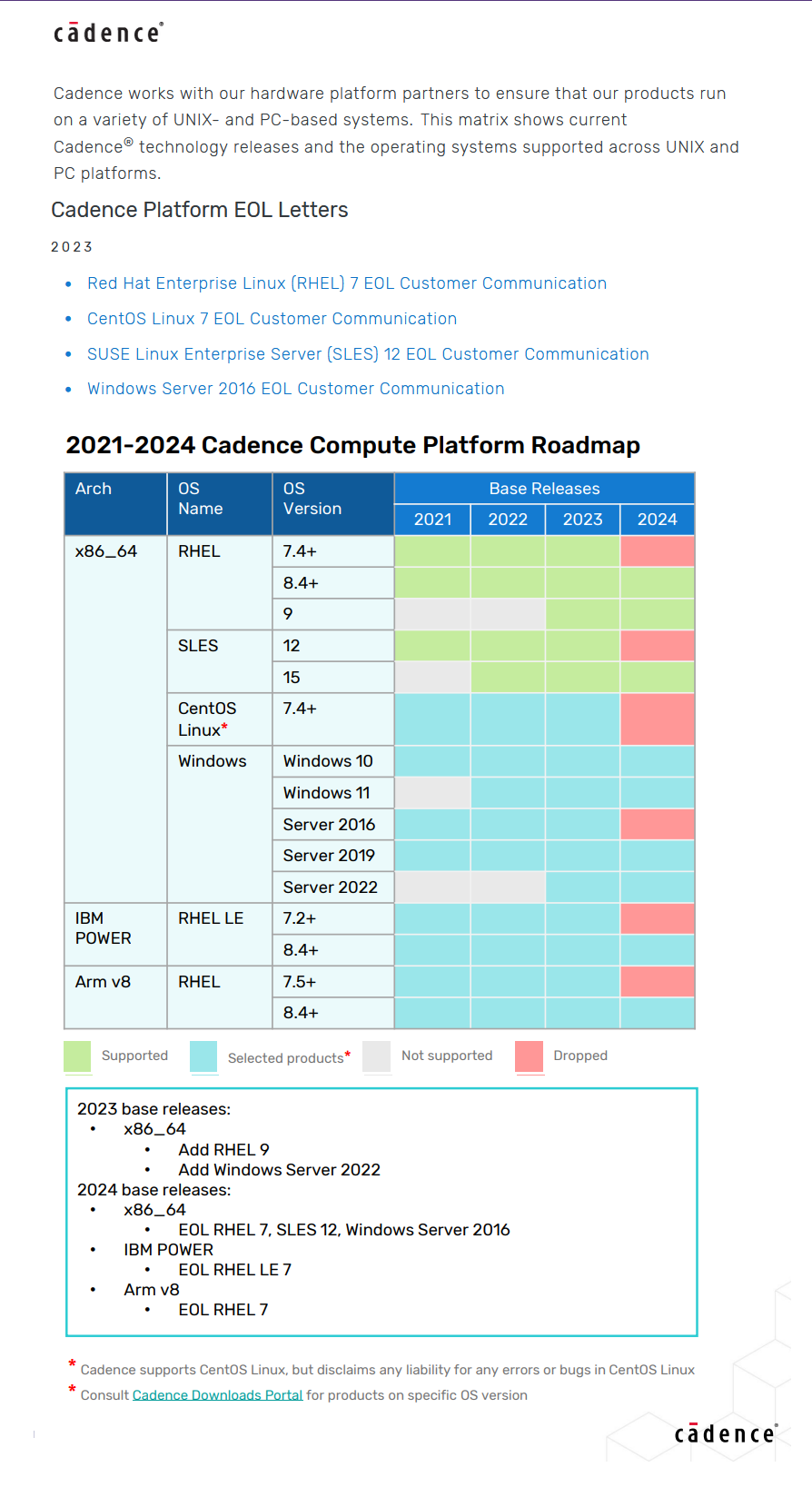

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 13.2 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please