Cadence Virtuoso, Release Version IC6.1.8 ISR32 | 11.6 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled Virtuoso, Release Version IC6.1.8 ISR32 (06.18.320) is a holistic, system-based solution that provides the functionality to drive simulation and LVS-clean layout of ICs and packages from a single schematic.

CCRs Fixed in IC6.1.8 and/or ICADVM20.1 ISR32 - Date: May 2023

2804715 Simulation for some corners remains incomplete after netlisting is finished

2798702 probe.tcl has unwanted commands after AMS simulation

2796355 Error WIA-1175 on CIW via ADE Explorer when the environment variable adexl.plotting plotScalarExpressions is set to nil

2794633 LSCS domain-state drops active test during ocean run

2794399 Incorrect netlist is generated when Device Masking is enabled for Reliability analysis

2790295 HspiceD netlister taking significantly more time for the same design in latest version than compared to IC6.1.8 ISR10

2790134 SOA violations for maximum peak value are reported in the cumulative results for minimum peak violations

2788667 Edits in descended block keep adding net highlights upon edits when another copy of top-level layout is open

2787761 Netlisting a schematic cell leads to the error E,DUPIMP or E,DUPIDN

2787043 Unable to sort data in the Detail-Transpose view in ADE Assembler

2783290 Modgen failed to abut pseudoparallel connection

2782858 Improve create bus command use model to compute the bit spacing when the command is invoked

2781538 AMS UNL: Netlisting error with the function amsOSSAmsSpecificPrintInst

2779550 Virtuoso Electromigration- Clarity 3D Solver: Incorrect translation of oblong vias

2779318 Virtuoso exits unexpectedly while running Multi Technology Simulation

2778666 Probing from Checks/Asserts output view is not following configured and simulated hierarchy

2777657 Evaluation problems with ICRP when ternary conditional operator is used to set the temperature

2777435 An error occurs while importing the CSV file in VDR

2776875 axlPutNote does not work for group history

2776610 Bus spacing in create bus could not be changed after changing the bus net width

2775676 Change the label 'instance Name for Testbench' in the Advanced Testbench Reuse form to something more descriptive

2775042 Ensure that the 'View Log Messages' submenu entry is independent of msg.db

2774690 Issues with while updating pin direction in Layout XL

2773209 Instance coloring applied incorrectly for iterated instances

2772911 The is_unconnected attribute incorrectly extracted as true for connected input pins in schematic

2772900 Incorrect netlist is generated when the input is repeated bus bits

2772670 Virtuoso exits unexpectedly when the strand number is greater than the bits mentioned in the net name field in the Create Strand Wire form

2770093 relharmnum is not in the netlist when sampled (jitter) is used in multiple pnoise

2769293 Poor performance when some nets are specified as a matched length constraint by Virtuoso Space-based Router auto routing

2768865 Incorrect sorting of results data in the Detail-Transpose view

2768839 Variables are randomly missed from the netlist

2768456 Increase precision for dbWriteSkill dumping large oaDist and oaCoord values

2768051 Issue a warning message indicating that local sweeps are not supported in reliability analysis

2767301 calcVal lint check does not consider multiple matching parameters

2763766 Re-evaluation does not work for fault results

2763402 ac analysis is required to perform stb analysis using actimes in AMS simulations

2763282 Extraction in EAD becomes unresponsive for Effective R Calculator when pressing the calculate button twice

2762576 Maximize via violation does not check via not centered on wire intersection

2762506 Virtuoso Electromigration- LVS-based flow: unexpected ports created because the SVDB is used from an LVS run with blackbox

2761867 If the signal via is a cross via, identify and ensure shield stack Vias are aligned properly

2761538 Design variables with expressions defined using strcat cannot be imported from a CSV

2758964 Syntax error reported for the 'Tj' variable defined in ICT-EM file for EAD

2758245 An incorrect model section is selected for a model if the model sections are specified in different case in the model file and the Corners Setup form

2757416 The Plot Outputs button not working in ADE Explorer

2755625 ocnxlUpdatePointVariable should update dependent variables

2754635 The CSV file shows different heading names than those specified in the argument '?exprList' of the function 'awvSaveToCSV'

2754093 Unexpected licenses checked out during EAD distributed processing

2752967 Virtuoso ADE Verifier shows different results for Local and Batch Run modes

2750137 Implementation run reports an error if the implementation run summary data file is not writable

2748073 Quantus exits during qrcToDfII if hierarchical_cell_list_file contains cells which are not present inside the layout

2747919 Cannot view waveform outputs during simulation due to ERROR (WIA-1175)

2746313 In ADE Assembler, nodes within a DSPF file cannot be driven through externally defined voltage sources

2743855 Spaces in the library file paths specified in the Include Options Setup form for AMS cause the xrunArgs file to fail

2743781 45-degree geometries produced during DEF Out translation are not in sync with the ones created in Virtuoso

2743302 Inconsistent behavior of compute enclosures in the Via Properties form between ICADVM20.1 ISR27 and ISR28

2741962 Antenna diode attribute extraction

2741259 Unable to consistently plot waveforms in Virtuoso Visualization and Analysis XL when running simulation remotely

2733742 libImport reports warnings and does not translate some DRAs

2724931 A SKILL error is reported when editing device Design Intent for a specific case

2723572 libImport should read .ssm files and referenced content from the -dirs argument of libImport

2723435 axlWriteOceanScriptLCV does not write the script in ADE Assembler unless a maestro cellview is opened

2719180 ADE Assembler creates line breaks in the dspf_include option

2718189 A warning message is reported when closing a layout window in EAD

2717830 Results from Virtuoso Visualization and Analysis XL Calculator and the Direct Measurements assistant do not match

2716377 File export to Allegro fails on imported components of libImport

2684395 Waveform expressions are visible although filtered out from Detail-Transpose results view

2682351 Virtuoso exits unexpectedly after resizing log viewer window

2679602 Add an API to retrieve results of all data points from coverage data, which is sliced by verification space

2676959 maeSetReliabilityOptionVal not reflecting in reliability analysis created from SKILL

2667965 ADE Assembler creates a bad netlist if the function 'round' is used in the design variables

2664491 Unable to consistently plot waveforms in Virtuoso Visualization and Analysis XL when running simulation remotely

2659404 Intercept labels for x and y axes are not working by the vertical and horizontal markers

2652087 Net highlighting during EIP is distracting when the top cell is opened in multiple windows

2636406 Intercept labels for x and y axes are not shown by the vertical and horizontal markers even when the Intercepts field is set to 'on'

2633378 EIP: Complete net highlighted when selecting an object while top level cell is shown in another canvas

2592669 The '-state' option of the 'runsv' command reports an unexpected INFO message (RUNSV-32)

2272838 ocnGenNoiseSummary does not report noise results when the given hierLevel is greater than the level in the design

May 2023

2798702 probe.tcl has unwanted commands after AMS simulation

2796355 Error WIA-1175 on CIW via ADE Explorer when the environment variable adexl.plotting plotScalarExpressions is set to nil

2794633 LSCS domain-state drops active test during ocean run

2794399 Incorrect netlist is generated when Device Masking is enabled for Reliability analysis

2790295 HspiceD netlister taking significantly more time for the same design in latest version than compared to IC6.1.8 ISR10

2790134 SOA violations for maximum peak value are reported in the cumulative results for minimum peak violations

2788667 Edits in descended block keep adding net highlights upon edits when another copy of top-level layout is open

2787761 Netlisting a schematic cell leads to the error E,DUPIMP or E,DUPIDN

2787043 Unable to sort data in the Detail-Transpose view in ADE Assembler

2783290 Modgen failed to abut pseudoparallel connection

2782858 Improve create bus command use model to compute the bit spacing when the command is invoked

2781538 AMS UNL: Netlisting error with the function amsOSSAmsSpecificPrintInst

2779550 Virtuoso Electromigration- Clarity 3D Solver: Incorrect translation of oblong vias

2779318 Virtuoso exits unexpectedly while running Multi Technology Simulation

2778666 Probing from Checks/Asserts output view is not following configured and simulated hierarchy

2777657 Evaluation problems with ICRP when ternary conditional operator is used to set the temperature

2777435 An error occurs while importing the CSV file in VDR

2776875 axlPutNote does not work for group history

2776610 Bus spacing in create bus could not be changed after changing the bus net width

2775676 Change the label 'instance Name for Testbench' in the Advanced Testbench Reuse form to something more descriptive

2775042 Ensure that the 'View Log Messages' submenu entry is independent of msg.db

2774690 Issues with while updating pin direction in Layout XL

2773209 Instance coloring applied incorrectly for iterated instances

2772911 The is_unconnected attribute incorrectly extracted as true for connected input pins in schematic

2772900 Incorrect netlist is generated when the input is repeated bus bits

2772670 Virtuoso exits unexpectedly when the strand number is greater than the bits mentioned in the net name field in the Create Strand Wire form

2770093 relharmnum is not in the netlist when sampled (jitter) is used in multiple pnoise

2769293 Poor performance when some nets are specified as a matched length constraint by Virtuoso Space-based Router auto routing

2768865 Incorrect sorting of results data in the Detail-Transpose view

2768839 Variables are randomly missed from the netlist

2768456 Increase precision for dbWriteSkill dumping large oaDist and oaCoord values

2768051 Issue a warning message indicating that local sweeps are not supported in reliability analysis

2767301 calcVal lint check does not consider multiple matching parameters

2763766 Re-evaluation does not work for fault results

2763402 ac analysis is required to perform stb analysis using actimes in AMS simulations

2763282 Extraction in EAD becomes unresponsive for Effective R Calculator when pressing the calculate button twice

2762576 Maximize via violation does not check via not centered on wire intersection

2762506 Virtuoso Electromigration- LVS-based flow: unexpected ports created because the SVDB is used from an LVS run with blackbox

2761867 If the signal via is a cross via, identify and ensure shield stack Vias are aligned properly

2761538 Design variables with expressions defined using strcat cannot be imported from a CSV

2758964 Syntax error reported for the 'Tj' variable defined in ICT-EM file for EAD

2758245 An incorrect model section is selected for a model if the model sections are specified in different case in the model file and the Corners Setup form

2757416 The Plot Outputs button not working in ADE Explorer

2755625 ocnxlUpdatePointVariable should update dependent variables

2754635 The CSV file shows different heading names than those specified in the argument '?exprList' of the function 'awvSaveToCSV'

2754093 Unexpected licenses checked out during EAD distributed processing

2752967 Virtuoso ADE Verifier shows different results for Local and Batch Run modes

2750137 Implementation run reports an error if the implementation run summary data file is not writable

2748073 Quantus exits during qrcToDfII if hierarchical_cell_list_file contains cells which are not present inside the layout

2747919 Cannot view waveform outputs during simulation due to ERROR (WIA-1175)

2746313 In ADE Assembler, nodes within a DSPF file cannot be driven through externally defined voltage sources

2743855 Spaces in the library file paths specified in the Include Options Setup form for AMS cause the xrunArgs file to fail

2743781 45-degree geometries produced during DEF Out translation are not in sync with the ones created in Virtuoso

2743302 Inconsistent behavior of compute enclosures in the Via Properties form between ICADVM20.1 ISR27 and ISR28

2741962 Antenna diode attribute extraction

2741259 Unable to consistently plot waveforms in Virtuoso Visualization and Analysis XL when running simulation remotely

2733742 libImport reports warnings and does not translate some DRAs

2724931 A SKILL error is reported when editing device Design Intent for a specific case

2723572 libImport should read .ssm files and referenced content from the -dirs argument of libImport

2723435 axlWriteOceanScriptLCV does not write the script in ADE Assembler unless a maestro cellview is opened

2719180 ADE Assembler creates line breaks in the dspf_include option

2718189 A warning message is reported when closing a layout window in EAD

2717830 Results from Virtuoso Visualization and Analysis XL Calculator and the Direct Measurements assistant do not match

2716377 File export to Allegro fails on imported components of libImport

2684395 Waveform expressions are visible although filtered out from Detail-Transpose results view

2682351 Virtuoso exits unexpectedly after resizing log viewer window

2679602 Add an API to retrieve results of all data points from coverage data, which is sliced by verification space

2676959 maeSetReliabilityOptionVal not reflecting in reliability analysis created from SKILL

2667965 ADE Assembler creates a bad netlist if the function 'round' is used in the design variables

2664491 Unable to consistently plot waveforms in Virtuoso Visualization and Analysis XL when running simulation remotely

2659404 Intercept labels for x and y axes are not working by the vertical and horizontal markers

2652087 Net highlighting during EIP is distracting when the top cell is opened in multiple windows

2636406 Intercept labels for x and y axes are not shown by the vertical and horizontal markers even when the Intercepts field is set to 'on'

2633378 EIP: Complete net highlighted when selecting an object while top level cell is shown in another canvas

2592669 The '-state' option of the 'runsv' command reports an unexpected INFO message (RUNSV-32)

2272838 ocnGenNoiseSummary does not report noise results when the given hierLevel is greater than the level in the design

May 2023

The Cadence Virtuoso System Design Platform links two world-class Cadence technologies—custom IC design and package/PCB design/analysis—creating a holistic methodology that automates and streamlines the design and verification flow for multi-die heterogeneous systems. Leveraging the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment, it provides a single platform for IC-and package/system-level design capture, analysis, and verification. In addition, the Virtuoso System Design Platform provides an automated bidirectional interface with the Cadence SiP-level implementation environment and Clarity 3d Solver. The Virtuoso System Design Platform allows IC designers to easily include system-level layout parasitics in the IC verification flow, enabling time savings by combining package/board layout connectivity data with the IC layout parasitic electrical model. The automatically generated “system-aware” schematic that results can then be easily used to create a testbench for final circuit-level simulation. The Virtuoso System Design Platform automates this entire flow, eliminating the highly manual and error-prone process of integrating system-level layout parasitic models back into the IC designer’s flow.

Cadence Virtuoso: Introduction

This video shows the basic introduction to one of the most used IC design tools in the industry and academia - Cadence virtuoso. It also shows how to edit schematic design in cadence virtuoso.

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world’s most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications.

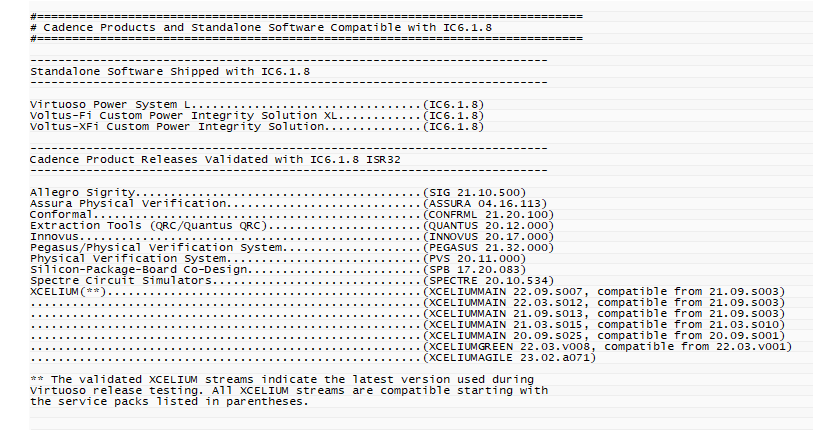

Product: Cadence Virtuoso

Version: IC6.1.8 ISR32 (06.18.320) hotfix

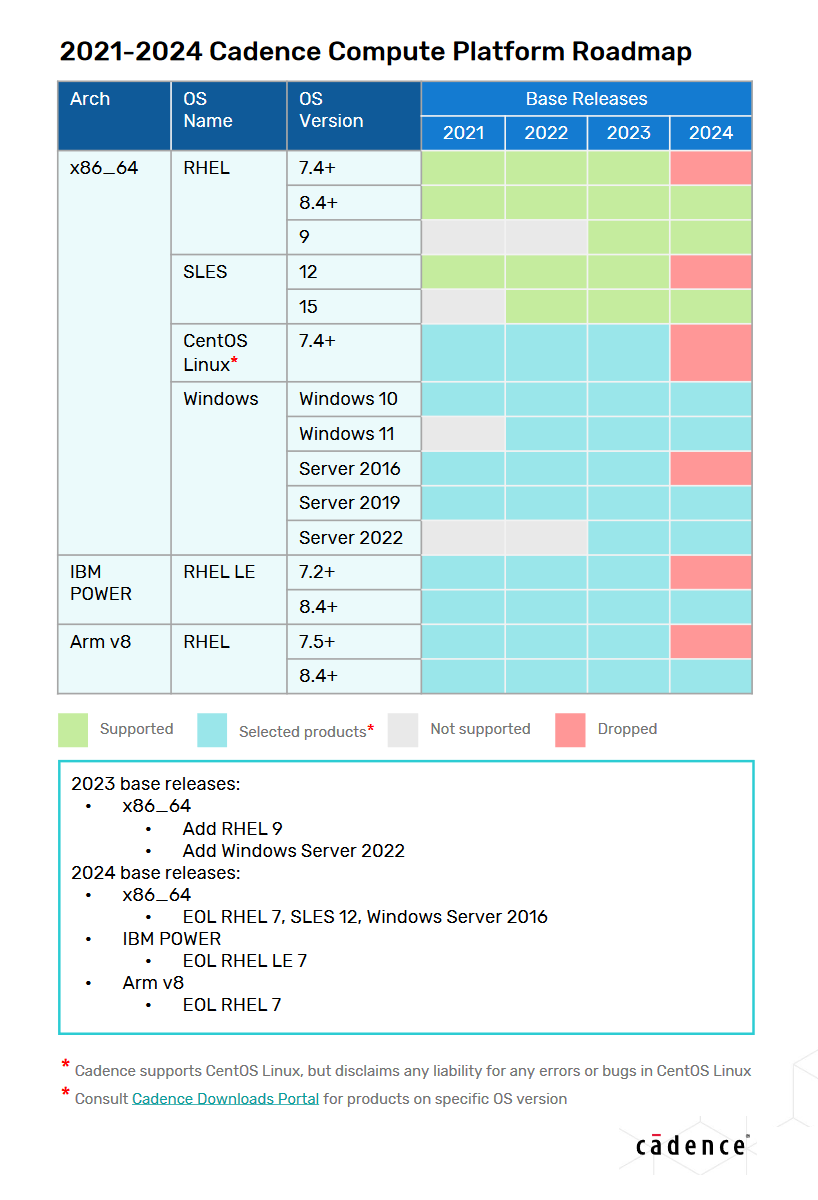

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 11.6 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please