Cadence Virtuoso, Release Version ICADVM 20.10.000 | 10.1 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled Virtuoso, Release Version ICADVM 20.10.000 Base. This software consists of features and functionality required for creating 5nm designs, which include an accelerated, row-based custom placement and routing methodology.

Featured Enhancements

Here is a listing of some of the important updates made to the ICADVM20.1 and IC6.1.8 ISR14 releases:

ICADVM20.1 Only

Bond Wires in Cross-Fabric EM Models (Virtuoso RF Solution)

Electromagnetic simulations for cross-fabric designs now support ICs connected through bond wires.

Material File in EM Simulation (Virtuoso RF Solution)

Specify a material file in the process stackup that Electromagnetic Solver assistant sends to Clarity 3D for simulations. This file provides support for advanced material properties and frequency-dependent dielectrics.

Create Split Symbols (Virtuoso Schematic Editor XL)

Split a large symbol into multiple partial symbols by using the Split Symbols feature in Virtuoso Schematic Editor. Splitting large symbol masters improves the legibility of pin symbols, especially in large PCB and package schematics.

Virtuoso Power Manager for Static Power Verification (Virtuoso Schematic Editor XL)

Virtuoso Power Manager enables static power verification for analog and mixed signal IPs by checking, extracting, exporting, and verifying the power intent of IP designs.

Layer-Based flow in Concurrent Layout (Virtuoso Layout Suite EXL and Virtuoso Layout Suite XL)

Define layer-based partitions using the layer-based flow in Concurrent Layout. When these design partitions are defined, two dedicated constraint groups are also created. These constraint groups assist you in routing and interactive wire editing. This way, you can limit the editing only to those layers that are part of the current layer-based design partition.

Design Planning and Analysis (Virtuoso Layout Suite EXL)

The Virtuoso Design Planner tool has been replaced by the Virtuoso Design Planning and Analysis (DPA) tool, which supports an expanded range of floorplanning, design planning, and congestion analysis capabilities, including support for hard blocks, soft blocks, and virtual hierarchies. This enhanced support is accessible through a unified Plan menu, Design Planning workspace, and Design Planning toolbar, all of which are available from the Layout EXL window.

ICADVM20.1 and IC6.1.8 ISR14

Distribute Simulation Jobs (Virtuoso ADE Explorer and Virtuoso ADE Assembler)

Control thousands of netlisting and simulation jobs in parallel using the default job control mode, LSCS (Large-Scale Cloud Simulations) in Virtuoso ADE Explorer and Virtuoso ADE Assembler. LSCS implements a new architecture to run simulations with better resource utilization. It also enables future scalability requirements for cloud simulations.

Merge Histories (Virtuoso ADE Assembler)

Merge the results from multiple histories into a single history without running a simulation. Merging histories not only merges the results from different histories, but also merges setups used in those histories.

Performance Diagnostic Tool (Virtuoso Design Environment)

Use the Performance Diagnostic tool to isolate issues that might have caused an application to slow down or freeze. It has an auto-hiding control toolbar to let you record callstacks when the application slows down.

2332454 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2332071 Cannot change the test name in maestro view in ADE Explorer

2327724 The CSV file in which the setup is exported from the Results tab in ADE Assembler is not saved at the desired location

2327005 Wrong column header exporting CSV file from detail transpose

2326741 Virtuoso exits unexpectedly due to an internal application error

2326292 Running 'runsv' reports 'runams' instead of 'runsv'

2326286 Virtuoso exits unexpectedly when editing a figGroup

2325395 Create Via command violates shape boundary for polygonal shapes

2325056 Virtuoso exits unexpectedly when saving constraints cache

2324097 Virtuoso exits unexpectedly when launching Schematics XL

2324083 Virtuoso exits unexpectedly due to an internal application error

2323750 Padstacks are erroneously exported to CLF as bumps

2323703 Virtuoso exits unexpectedly due to a segmentation fault in ddtUpdateGraph in IC6.1.8 ISR12

2323562 Create Via command not following the correct purpose defined in layer1ExtraParams

2323534 Via not created by Auto Via command due to obstruction.

2323038 emir.conf file not written to the netlist directory for AMS EMIR run with the new EMIR UI

2322780 3X performance degradation observed during power grid generation as cover cell at initialization

2322703 5X performance degradation observed during power grid generation as FigGroup at initialization

2321972 The Chaining command takes up to 2 minutes to open the Options form

2321733 Virtuoso exits unexpectedly in ctuOaUpdate::registerOAShapeToBeDeleted

2321703 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321436 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321137 Virtuoso exits unexpectedly during Check and Save

2321080 Probe translation fails when device prefix is different for different devices of the same type

2319537 The Push Pre-Routes command ignores via blockages when there are floating wires in the design

2319127 Remove all instances of catch/throw from the code

2318879 Virtuoso exits unexpectedly when deleting labels in Text Editor

2317803 Virtuoso exits unexpectedly when using Design Intent

2317179 Checker does not consider full wire length to determine width direction when using the minOppExtension table

2316623 Auto Via command must reduce one edge by 1db to handle another offset correctly

2316506 Virtuoso exits unexpectedly when browsing Rapid Analog Prototype constraints

2316443 Unable to generate eadTechFile using the eadModelGen utility

2315205 minViaSpacing support for centerToCenter parameter does not work as expected

2314971 Expressions with extracted view net mapping in LSCS control mode evaluate into errors but evaluate successfully in ICRP mode

2314905 The simulation does not run on setting up a single individual fault in the ADE Assembler fault simulation setup

2314592 Virtuoso exits unexpectedly while processing a pop-up menu event

2313575 Improve handling of netlisting failures

2312572 Extractor claims there is no via definition with implant layer if extractVerifyWellSubstrateConnections is nil

2312347 Virtuoso exits unexpectedly after AMS Monte Carlo simulation completes

2312108 Updating library property bag using the FirstAccessLib trigger fails in ICADVM18.1

2311881 The Set Valid Layers form is distorted in IC6.1.8 but appears fine in IC6.1.7

2310932 Decap Fill places overlapping decaps

2309540 Add save statements for post layout signals used in expressions

2309431 Checker does not flag violations when using direction parameters with minOppExtension

2309277 Virtuoso exits unexpectedly during dbClose

2308056 Virtuoso exits unexpectedly during descend read

2307756 Virtuoso exits unexpectedly when saving constraints cache

2307603 A beta license is required to use the technology file in Voltus-Fi

2307296 Random netlist and simulation errors when run Size Over Corners

2306918 Incorrect pg_function exported for some pins

2306226 DesignSync options are ignored when creating a setup library view using the slaOpenOrCreateView function

2305135 Placement Planning throws an error when the Tap tab is hidden

2305117 SystemVerilog Netlister stops responding and causes Virtuoso to exit unexpectedly

2305014 Need an option to display all the active WSPs for a given layer

2304848 Virtuoso exits unexpectedly while cleaning up raw shape to fractured shapes mapping.

2304824 Virtuoso exits unexpectedly when saving constraints cache

2304346 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2303971 pg_function is not being detected correctly

2303856 Fault simulation with sampling fails because fault statement has incomplete sample option

2303636 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode.

2303616 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode

2303562 Trunk trim generate wrong begin and end point of a pathSeg

2303178 Virtuoso stops responding when using leHiAssignNet command and Repeat Command is off in the Layout Editor Options form

2303148 SystemVerilog Netlister stops responding when using time literals to override CDF parameters

2302634 Unable to generate an AMS netlist when using pPar function in the parameter values for the specified instances

2302553 The Voltus-Fi GUI does not load any nets in the EM results window when vsaSetEMPlot and vsaLoadNets functions are used together

2302343 Expression evaluates for failed iteration of Monte Carlo run in LSCS run mode

2301963 Many config views are created with config sweep by LSCS in ADE

2301789 Virtuoso exits unexpectedly when evaluating the spectrumMeasurement expression from ADE Assembler

2301775 Allegro Import translator generates errors in ECO mode when 'ocm' symbols exist in the SiP file

2301724 When separate history management is enabled, Virtuoso exits unexpectedly after copying a maestro view and deleting a history point

2301209 Enable the traceTxChainWithDirComp flag in vpmSetEnvVals()

2301206 Enable the extendedHierCellTermDirCheck flag in vpmSetEnvVals()

2301072 Parametric sweep fails with ERROR (ASSEMBLER-2343) using dependent variables

2300228 Parameter not set in the netlist when using calcVal and variable sweep in the corners

2299793 Handle automatically created RPP for single rail level shifter cells in Virtuoso Power Manager

2299786 Handle three-terminal devices in supply and data path in Virtuoso Power Manager extractor

2299778 Virtuoso Power Manager extractor to support three-terminal capacitor devices

2299767 Virtuoso Power Manager setup to support registration of three-terminal devices in the capacitor category

2299373 Virtuoso Power Manager missing pg_pin definition in the exported Liberty file

2299234 Virtuoso stops responding when using recursive variable in ADE Explorer

2299076 Virtuoso exits unexpectedly when non-static data members of a class are not initialized

2299013 Operating Region Violations option missing in the context menu of the Detail results view

2298616 Noise summary feature does not work as expected on specifying instances through the 'Include Instances' field

2298606 The Spectrum assistant rounds off stop time, giving wrong THD results and spectrum plot

2298548 FastC Coupled C becomes smaller when side metal is in a specific range

2298313 XOasis Out does not set strict flag for layerNames in OASIS files

2298035 Can we run Modelwriter in IC6.1.8 ISR12?

2297815 The clip function does not work with a family of voltage waveforms in the Monte Carlo simulation

2297684 Unable to launch Verify Design UI

2297489 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2296131 Virtuoso Power Manager extracting incorrect pg_function for a few pins

2296127 Virtuoso Power Manager missing pg_function for a few pins

2296004 Virtuoso Power Manager extracting incomplete pg_function

2295351 Virtuoso exits unexpectedly when specifying the setup data in Data View assistant

2294844 Slow performance when leHiFlatten command is run

2294441 The Auto Via command is choosing larger enclosure than expected for GM0 metal

2294333 pz analysis results are plotted in wrong axes

2294162 Filter issues for multiple corner model setup in Detail-Transpose results view

2293292 Virtuoso Power Manager is inheriting VDD/supply attribute from cells in the ignore category

2293289 Virtuoso Power Manager extractor does not contain pg_function values for few pins in scratch mode

2293284 Update the Noise Summary form in IC6.1.8 ISR7 to support wildcards when selecting instances with hierarchy in the schematic

2293277 Size Over Corners fails unless OK is clicked on the new Size Over Corners options form

2293273 Size Over Corners does not proceed with corner analysis

2292266 When editing virtual hierarchy, switch back to the workspace that customer used to work in Layout XL

2292256 Display all local nets up to the virtual pins within a virtual hierarchy when doing Select - Local Nets on a selected virtual hierarchy

2291881 Options on the Harmonic Balance Noise Analysis form do not display correctly when Noise Figure is selected

2291692 SKILL function ddsSetLibManLCV does not work on combined libraries

2291057 While accessing Self-Heating Effect analysis reports, on reverting back to text files from html files, the text files go missing

2290993 Checker exits unexpectedly if a layerIndex value for a layer specified with minVoltageExtension is 0

2290870 Virtuoso exits unexpectedly when attaching a technology database to a library

2290004 AMS UNL netlisting assembly does not work as expected in IC6.1.8 ISR10

2289577 Add model name to the exported Unified Power Format file

2289480 Performance is degraded during interactive edit operation for DI associated object

2288933 ADE Explorer allows adding temp in design variable

2288846 Virtuoso stops responding when using multiple tabs

2288273 ESD Optimizer removes vias that should be retained in the optimized DSPF file

2288267 The ESD HBM waveform shows an incorrect current value at t=0 that does not match the schematic value

2287209 ADE Verifier ignores the values in the Verification Space column when importing data from a CSV file

2286809 Unable to change order of the pin in Pin Tool after "Create Pin Template" utility is invoked.

2286617 Add the argument rcr=selected to the Solver Method table on selecting Iterated as the solver method

2286597 Pin Optimizer fails when there is a mosaic in the design

2286453 Links with literal equal sign (=) do not work with the hiCreateHypertextField

2286247 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2285890 Layout XL stops responding when using Gnome window manager

2284658 Provide the support to register any instance as header or footer type special cell

2284010 Additional argument 'Exclude' for net analysis in the ADE EMIR Setup form gets appended as a new line in the Summary Information table

2283915 Pre-simulation of an operating region spec is stopped when ADE Assembler uses a local host

2283485 DRD does not report minExtensionEdge constraint violations

2283273 A strange stdVia remains when we escape the command during wiring

2283202 Virtuoso Power Manager not extracting the expected isolation strategy signal

2283171 Additional internal power pins found for related power pins

2280242 Performance degradation observed when transitioning from ADE L to ADE Explorer

2279815 When working with the Make Cell operation, selected objects are losing connectivity

2279021 Virtuoso Space-based Router introduces maxWidth and allowedWidthRanges violations when hitting offGrid pins

2277658 Unable to create a via using the Auto Via command due to shape on cut layer though purpose of cut shape is specified in viaIgnorePurposes

2277395 The autoSave environment variable does not work in IC6.1.8 and ICADVM18.1 ISR9 or later releases

2277352 Found libImport errors in Allegro board file

2276459 DEFOUT of path objects adds unwanted horizontal extension at 45-degree transitions

2276436 Library copy must also update target and footprint library name parameters

2276425 Provide support for package footprint export of an imported SiP layout

2275830 The awvSetLegendWidth function does not work with circular graphs

2274889 Remove the Set Valid Layers form

2273262 Memory consumption increases when using noiseSummary() statement in the OCEAN script

2273154 AMS UNL netlister with arrayed instances in the SystemVerilog code causes an EXNEUS elaboration error.

2272602 Additional internal supplies in exported Liberty file

2272601 Virtuoso Power Manager missing pg_function for a few pins

2272060 Virtuoso exits unexpectedly due to segmentation fault in axlPlotSingleOutput

2271313 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2270877 Runams adds -flow argument to the probe.tcl file on restarting, which causes Spectre to fail

2270654 Update Components and Nets should replace existing pin in case Design Intent for that pin is updated to different layer or width

2269647 Support for module type in the Co-Design flow

2268969 Co-Design does not work if the fabric type is module

2264905 Extracting VerilogAMS cellviews stopped working since IC6.1.8 ISR6

2264534 Yield view shows incorrect results when using the VAR expression to define specifications

2263432 Line chop in minSpacing mode chops pathSeg placed outside prBoundary with larger value than required

2263427 Line chop in minSpacing mode does not chop rectangle placed outside prBoundary

2262620 Implicit signals are not generated because of a specific sequence of changing 'Save all' options

2262063 Spectre assert statements return 'inf' for Duration (%) in ADE Assembler output Checks/Asserts table

2259594 Virtuoso exits unexpectedly when running an EM simulation using a smart view

2259565 Smart view is not netlisted correctly; shows a warning that the view is not a valid extracted view

2259521 Layout XL: Incorrect extraction for a MIM capacitor in two-metal stack configuration

2258187 Double-clicking a signal waveform incorrectly works as the Plot All command

2255264 The 'filter_ir_percent' option does not work in Voltus-Fi

2254523 Update the *WARNING* (LCE-2045) message to reflect the actual type of the layer instead of using the term 'logical layer'

2253741 Setting the environment variable groupRunA to nil causes identical corner point runs to be linked and not rerun

2252419 The footprint Library Name property does not automatically update in Schematic Edit Object Properties

2246655 Performance issues when waiving more than 10k violations

2246026 Measurement across corners is not working correctly for expressions without name

2245814 ADE Explorer slower than ADE L when ignoreDesignChangesDuringRun is set

2244573 Virtuoso RF Solution: Instantiated pins are no longer visible after changing the name of the Export Die library

2243791 Allegro Import translation fails with SiPtoOA error

2237464 Virtuoso exits unexpectedly when pasting objects which include one or more traces

2237124 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

2236937 Virtuoso exits unexpectedly when using the Fit Visible Traces command

2235874 Modgen template reuse gives warning and fails

2235872 Virtuoso exits unexpectedly when running simulations in ADE Assembler

2232020 Virtuoso RF Solution viaSelectionMode use non-Cutlayers blocks via selection

2229395 Limiting voltage parameter in variableGainAmplifier in Functional Library does not work

2228879 Output expressions with plot and save disabled should not be evaluated

2222659 Discrepancy between spectre_ddmrpt and ADE assembler fault report

2222582 Appearance of statement aging_analysis_name value=dc in the netlist

2215721 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2213922 Router routes over blockages for some differential pair nets

2210847 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2208481 Model group name containing a dot (.) causes an error in worst case corners

2204742 Virtuoso exits unexpectedly when the hiRegZoomPanProc SKILL function is used

2203332 Spectre reliability relx_tran argument truncates decimal points

2200925 Reference History does not work as expected when using variables dependent on each other

2190802 Checks/Asserts tab reports 'inf' for Duration (%)

2188074 The rodFillBBoxWithRects SKILL function is creating fill shapes outside the given bounding box

2182019 In Pin to Trunk routing, Trunk Extend extends the trunk outside of selected area

2170762 ADE Assembler consumes large amounts of memory and does not release it until Virtuoso is closed

2150446 Pin Placement is creating shorts for existing power pins

2147838 SKILL function ddsSetLibManLCV does not work on combined libraries

2141130 Release memory after ADE Assembler is closed

2128122 The leGetCoordinateForm (bindkey Shift+N) Pan-to-coordinate is not compatible with infix mode

2112949 Discrepancies in the results displayed in Detail view and Yield view

2110671 Bug in waveform comparison across corner

2098875 Memory no longer needed by ADE Assembler should be released to OS

2067163 Memory consumed by ADE Assembler is not released when the tool is closed; need to close Virtuoso

2064375 Incremental netlisting does not work with AMS Designer in ADE Explorer

2035506 Typical implementation does not work with the model files that do not have section details

2025368 Incremental netlisting does not work with AMS Designer in ADE Explorer

2020300 Pin To Trunk routing chooses offset via for simple pattern

2007678 In ADE Assembler, the Create Test Copy command in the context menu of Corners does not copy enabled corners in the Corner Setup form

1994369 Creating a Test Copy does not copy the corners setup

1961784 Specifying a variable in the Relative Harmonic field in the Periodic Noise Analysis setup gives an error

1954211 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1928931 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1832041 SKILL function ddsSetLibManLCV does not work on combined libraries

1767782 Allow to waive corner-specific violations

918684 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

October 2020

2332071 Cannot change the test name in maestro view in ADE Explorer

2327724 The CSV file in which the setup is exported from the Results tab in ADE Assembler is not saved at the desired location

2327005 Wrong column header exporting CSV file from detail transpose

2326741 Virtuoso exits unexpectedly due to an internal application error

2326292 Running 'runsv' reports 'runams' instead of 'runsv'

2326286 Virtuoso exits unexpectedly when editing a figGroup

2325395 Create Via command violates shape boundary for polygonal shapes

2325056 Virtuoso exits unexpectedly when saving constraints cache

2324097 Virtuoso exits unexpectedly when launching Schematics XL

2324083 Virtuoso exits unexpectedly due to an internal application error

2323750 Padstacks are erroneously exported to CLF as bumps

2323703 Virtuoso exits unexpectedly due to a segmentation fault in ddtUpdateGraph in IC6.1.8 ISR12

2323562 Create Via command not following the correct purpose defined in layer1ExtraParams

2323534 Via not created by Auto Via command due to obstruction.

2323038 emir.conf file not written to the netlist directory for AMS EMIR run with the new EMIR UI

2322780 3X performance degradation observed during power grid generation as cover cell at initialization

2322703 5X performance degradation observed during power grid generation as FigGroup at initialization

2321972 The Chaining command takes up to 2 minutes to open the Options form

2321733 Virtuoso exits unexpectedly in ctuOaUpdate::registerOAShapeToBeDeleted

2321703 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321436 Virtuoso exits unexpectedly when deleting labels in Text Editor

2321137 Virtuoso exits unexpectedly during Check and Save

2321080 Probe translation fails when device prefix is different for different devices of the same type

2319537 The Push Pre-Routes command ignores via blockages when there are floating wires in the design

2319127 Remove all instances of catch/throw from the code

2318879 Virtuoso exits unexpectedly when deleting labels in Text Editor

2317803 Virtuoso exits unexpectedly when using Design Intent

2317179 Checker does not consider full wire length to determine width direction when using the minOppExtension table

2316623 Auto Via command must reduce one edge by 1db to handle another offset correctly

2316506 Virtuoso exits unexpectedly when browsing Rapid Analog Prototype constraints

2316443 Unable to generate eadTechFile using the eadModelGen utility

2315205 minViaSpacing support for centerToCenter parameter does not work as expected

2314971 Expressions with extracted view net mapping in LSCS control mode evaluate into errors but evaluate successfully in ICRP mode

2314905 The simulation does not run on setting up a single individual fault in the ADE Assembler fault simulation setup

2314592 Virtuoso exits unexpectedly while processing a pop-up menu event

2313575 Improve handling of netlisting failures

2312572 Extractor claims there is no via definition with implant layer if extractVerifyWellSubstrateConnections is nil

2312347 Virtuoso exits unexpectedly after AMS Monte Carlo simulation completes

2312108 Updating library property bag using the FirstAccessLib trigger fails in ICADVM18.1

2311881 The Set Valid Layers form is distorted in IC6.1.8 but appears fine in IC6.1.7

2310932 Decap Fill places overlapping decaps

2309540 Add save statements for post layout signals used in expressions

2309431 Checker does not flag violations when using direction parameters with minOppExtension

2309277 Virtuoso exits unexpectedly during dbClose

2308056 Virtuoso exits unexpectedly during descend read

2307756 Virtuoso exits unexpectedly when saving constraints cache

2307603 A beta license is required to use the technology file in Voltus-Fi

2307296 Random netlist and simulation errors when run Size Over Corners

2306918 Incorrect pg_function exported for some pins

2306226 DesignSync options are ignored when creating a setup library view using the slaOpenOrCreateView function

2305135 Placement Planning throws an error when the Tap tab is hidden

2305117 SystemVerilog Netlister stops responding and causes Virtuoso to exit unexpectedly

2305014 Need an option to display all the active WSPs for a given layer

2304848 Virtuoso exits unexpectedly while cleaning up raw shape to fractured shapes mapping.

2304824 Virtuoso exits unexpectedly when saving constraints cache

2304346 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2303971 pg_function is not being detected correctly

2303856 Fault simulation with sampling fails because fault statement has incomplete sample option

2303636 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode.

2303616 Setting CDS_USE_XVFB to 1 generates an xmsim: *E,STRPIN error that stops invoking the SimVision GUI in interactive mode

2303562 Trunk trim generate wrong begin and end point of a pathSeg

2303178 Virtuoso stops responding when using leHiAssignNet command and Repeat Command is off in the Layout Editor Options form

2303148 SystemVerilog Netlister stops responding when using time literals to override CDF parameters

2302634 Unable to generate an AMS netlist when using pPar function in the parameter values for the specified instances

2302553 The Voltus-Fi GUI does not load any nets in the EM results window when vsaSetEMPlot and vsaLoadNets functions are used together

2302343 Expression evaluates for failed iteration of Monte Carlo run in LSCS run mode

2301963 Many config views are created with config sweep by LSCS in ADE

2301789 Virtuoso exits unexpectedly when evaluating the spectrumMeasurement expression from ADE Assembler

2301775 Allegro Import translator generates errors in ECO mode when 'ocm' symbols exist in the SiP file

2301724 When separate history management is enabled, Virtuoso exits unexpectedly after copying a maestro view and deleting a history point

2301209 Enable the traceTxChainWithDirComp flag in vpmSetEnvVals()

2301206 Enable the extendedHierCellTermDirCheck flag in vpmSetEnvVals()

2301072 Parametric sweep fails with ERROR (ASSEMBLER-2343) using dependent variables

2300228 Parameter not set in the netlist when using calcVal and variable sweep in the corners

2299793 Handle automatically created RPP for single rail level shifter cells in Virtuoso Power Manager

2299786 Handle three-terminal devices in supply and data path in Virtuoso Power Manager extractor

2299778 Virtuoso Power Manager extractor to support three-terminal capacitor devices

2299767 Virtuoso Power Manager setup to support registration of three-terminal devices in the capacitor category

2299373 Virtuoso Power Manager missing pg_pin definition in the exported Liberty file

2299234 Virtuoso stops responding when using recursive variable in ADE Explorer

2299076 Virtuoso exits unexpectedly when non-static data members of a class are not initialized

2299013 Operating Region Violations option missing in the context menu of the Detail results view

2298616 Noise summary feature does not work as expected on specifying instances through the 'Include Instances' field

2298606 The Spectrum assistant rounds off stop time, giving wrong THD results and spectrum plot

2298548 FastC Coupled C becomes smaller when side metal is in a specific range

2298313 XOasis Out does not set strict flag for layerNames in OASIS files

2298035 Can we run Modelwriter in IC6.1.8 ISR12?

2297815 The clip function does not work with a family of voltage waveforms in the Monte Carlo simulation

2297684 Unable to launch Verify Design UI

2297489 Unable to resize a graph strip in Virtuoso Visualization and Analysis XL

2296131 Virtuoso Power Manager extracting incorrect pg_function for a few pins

2296127 Virtuoso Power Manager missing pg_function for a few pins

2296004 Virtuoso Power Manager extracting incomplete pg_function

2295351 Virtuoso exits unexpectedly when specifying the setup data in Data View assistant

2294844 Slow performance when leHiFlatten command is run

2294441 The Auto Via command is choosing larger enclosure than expected for GM0 metal

2294333 pz analysis results are plotted in wrong axes

2294162 Filter issues for multiple corner model setup in Detail-Transpose results view

2293292 Virtuoso Power Manager is inheriting VDD/supply attribute from cells in the ignore category

2293289 Virtuoso Power Manager extractor does not contain pg_function values for few pins in scratch mode

2293284 Update the Noise Summary form in IC6.1.8 ISR7 to support wildcards when selecting instances with hierarchy in the schematic

2293277 Size Over Corners fails unless OK is clicked on the new Size Over Corners options form

2293273 Size Over Corners does not proceed with corner analysis

2292266 When editing virtual hierarchy, switch back to the workspace that customer used to work in Layout XL

2292256 Display all local nets up to the virtual pins within a virtual hierarchy when doing Select - Local Nets on a selected virtual hierarchy

2291881 Options on the Harmonic Balance Noise Analysis form do not display correctly when Noise Figure is selected

2291692 SKILL function ddsSetLibManLCV does not work on combined libraries

2291057 While accessing Self-Heating Effect analysis reports, on reverting back to text files from html files, the text files go missing

2290993 Checker exits unexpectedly if a layerIndex value for a layer specified with minVoltageExtension is 0

2290870 Virtuoso exits unexpectedly when attaching a technology database to a library

2290004 AMS UNL netlisting assembly does not work as expected in IC6.1.8 ISR10

2289577 Add model name to the exported Unified Power Format file

2289480 Performance is degraded during interactive edit operation for DI associated object

2288933 ADE Explorer allows adding temp in design variable

2288846 Virtuoso stops responding when using multiple tabs

2288273 ESD Optimizer removes vias that should be retained in the optimized DSPF file

2288267 The ESD HBM waveform shows an incorrect current value at t=0 that does not match the schematic value

2287209 ADE Verifier ignores the values in the Verification Space column when importing data from a CSV file

2286809 Unable to change order of the pin in Pin Tool after "Create Pin Template" utility is invoked.

2286617 Add the argument rcr=selected to the Solver Method table on selecting Iterated as the solver method

2286597 Pin Optimizer fails when there is a mosaic in the design

2286453 Links with literal equal sign (=) do not work with the hiCreateHypertextField

2286247 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2285890 Layout XL stops responding when using Gnome window manager

2284658 Provide the support to register any instance as header or footer type special cell

2284010 Additional argument 'Exclude' for net analysis in the ADE EMIR Setup form gets appended as a new line in the Summary Information table

2283915 Pre-simulation of an operating region spec is stopped when ADE Assembler uses a local host

2283485 DRD does not report minExtensionEdge constraint violations

2283273 A strange stdVia remains when we escape the command during wiring

2283202 Virtuoso Power Manager not extracting the expected isolation strategy signal

2283171 Additional internal power pins found for related power pins

2280242 Performance degradation observed when transitioning from ADE L to ADE Explorer

2279815 When working with the Make Cell operation, selected objects are losing connectivity

2279021 Virtuoso Space-based Router introduces maxWidth and allowedWidthRanges violations when hitting offGrid pins

2277658 Unable to create a via using the Auto Via command due to shape on cut layer though purpose of cut shape is specified in viaIgnorePurposes

2277395 The autoSave environment variable does not work in IC6.1.8 and ICADVM18.1 ISR9 or later releases

2277352 Found libImport errors in Allegro board file

2276459 DEFOUT of path objects adds unwanted horizontal extension at 45-degree transitions

2276436 Library copy must also update target and footprint library name parameters

2276425 Provide support for package footprint export of an imported SiP layout

2275830 The awvSetLegendWidth function does not work with circular graphs

2274889 Remove the Set Valid Layers form

2273262 Memory consumption increases when using noiseSummary() statement in the OCEAN script

2273154 AMS UNL netlister with arrayed instances in the SystemVerilog code causes an EXNEUS elaboration error.

2272602 Additional internal supplies in exported Liberty file

2272601 Virtuoso Power Manager missing pg_function for a few pins

2272060 Virtuoso exits unexpectedly due to segmentation fault in axlPlotSingleOutput

2271313 Virtuoso exits unexpectedly when pasting objects that include one or more traces

2270877 Runams adds -flow argument to the probe.tcl file on restarting, which causes Spectre to fail

2270654 Update Components and Nets should replace existing pin in case Design Intent for that pin is updated to different layer or width

2269647 Support for module type in the Co-Design flow

2268969 Co-Design does not work if the fabric type is module

2264905 Extracting VerilogAMS cellviews stopped working since IC6.1.8 ISR6

2264534 Yield view shows incorrect results when using the VAR expression to define specifications

2263432 Line chop in minSpacing mode chops pathSeg placed outside prBoundary with larger value than required

2263427 Line chop in minSpacing mode does not chop rectangle placed outside prBoundary

2262620 Implicit signals are not generated because of a specific sequence of changing 'Save all' options

2262063 Spectre assert statements return 'inf' for Duration (%) in ADE Assembler output Checks/Asserts table

2259594 Virtuoso exits unexpectedly when running an EM simulation using a smart view

2259565 Smart view is not netlisted correctly; shows a warning that the view is not a valid extracted view

2259521 Layout XL: Incorrect extraction for a MIM capacitor in two-metal stack configuration

2258187 Double-clicking a signal waveform incorrectly works as the Plot All command

2255264 The 'filter_ir_percent' option does not work in Voltus-Fi

2254523 Update the *WARNING* (LCE-2045) message to reflect the actual type of the layer instead of using the term 'logical layer'

2253741 Setting the environment variable groupRunA to nil causes identical corner point runs to be linked and not rerun

2252419 The footprint Library Name property does not automatically update in Schematic Edit Object Properties

2246655 Performance issues when waiving more than 10k violations

2246026 Measurement across corners is not working correctly for expressions without name

2245814 ADE Explorer slower than ADE L when ignoreDesignChangesDuringRun is set

2244573 Virtuoso RF Solution: Instantiated pins are no longer visible after changing the name of the Export Die library

2243791 Allegro Import translation fails with SiPtoOA error

2237464 Virtuoso exits unexpectedly when pasting objects which include one or more traces

2237124 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

2236937 Virtuoso exits unexpectedly when using the Fit Visible Traces command

2235874 Modgen template reuse gives warning and fails

2235872 Virtuoso exits unexpectedly when running simulations in ADE Assembler

2232020 Virtuoso RF Solution viaSelectionMode use non-Cutlayers blocks via selection

2229395 Limiting voltage parameter in variableGainAmplifier in Functional Library does not work

2228879 Output expressions with plot and save disabled should not be evaluated

2222659 Discrepancy between spectre_ddmrpt and ADE assembler fault report

2222582 Appearance of statement aging_analysis_name value=dc in the netlist

2215721 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2213922 Router routes over blockages for some differential pair nets

2210847 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

2208481 Model group name containing a dot (.) causes an error in worst case corners

2204742 Virtuoso exits unexpectedly when the hiRegZoomPanProc SKILL function is used

2203332 Spectre reliability relx_tran argument truncates decimal points

2200925 Reference History does not work as expected when using variables dependent on each other

2190802 Checks/Asserts tab reports 'inf' for Duration (%)

2188074 The rodFillBBoxWithRects SKILL function is creating fill shapes outside the given bounding box

2182019 In Pin to Trunk routing, Trunk Extend extends the trunk outside of selected area

2170762 ADE Assembler consumes large amounts of memory and does not release it until Virtuoso is closed

2150446 Pin Placement is creating shorts for existing power pins

2147838 SKILL function ddsSetLibManLCV does not work on combined libraries

2141130 Release memory after ADE Assembler is closed

2128122 The leGetCoordinateForm (bindkey Shift+N) Pan-to-coordinate is not compatible with infix mode

2112949 Discrepancies in the results displayed in Detail view and Yield view

2110671 Bug in waveform comparison across corner

2098875 Memory no longer needed by ADE Assembler should be released to OS

2067163 Memory consumed by ADE Assembler is not released when the tool is closed; need to close Virtuoso

2064375 Incremental netlisting does not work with AMS Designer in ADE Explorer

2035506 Typical implementation does not work with the model files that do not have section details

2025368 Incremental netlisting does not work with AMS Designer in ADE Explorer

2020300 Pin To Trunk routing chooses offset via for simple pattern

2007678 In ADE Assembler, the Create Test Copy command in the context menu of Corners does not copy enabled corners in the Corner Setup form

1994369 Creating a Test Copy does not copy the corners setup

1961784 Specifying a variable in the Relative Harmonic field in the Periodic Noise Analysis setup gives an error

1954211 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1928931 IgnoreDesignChangesDuringRun breaks netlisting if only Parameters check box is enabled

1832041 SKILL function ddsSetLibManLCV does not work on combined libraries

1767782 Allow to waive corner-specific violations

918684 Renaming an unmanaged library overwrites the DMTYPE setting in cdsinfo.tag

October 2020

The Cadence Virtuoso System Design Platform links two world-class Cadence technologies—custom IC design and package/PCB design/analysis—creating a holistic methodology that automates and streamlines the design and verification flow for multi-die heterogeneous systems.

Leveraging the Virtuoso Schematic Editor and the Virtuoso Analog Design Environment, it provides a single platform for IC-and package/system-level design capture, analysis, and verification. In addition, the Virtuoso System Design Platform provides an automated bidirectional interface with the Cadence SiP-level implementation environment and Clarity 3d Solver.

The Virtuoso System Design Platform allows IC designers to easily include system-level layout parasitics in the IC verification flow, enabling time savings by combining package/board layout connectivity data with the IC layout parasitic electrical model. The automatically generated “system-aware” schematic that results can then be easily used to create a testbench for final circuit-level simulation. The Virtuoso System Design Platform automates this entire flow, eliminating the highly manual and error-prone process of integrating system-level layout parasitic models back into the IC designer’s flow.

The Virtuoso Advanced-Node and Methodology Platform (ICADVM) consists of features and functionality required for creating 5nm designs, which include an accelerated, row-based custom placement and routing methodology that enables users to improve productivity and better manage complex design rules. Cadence introduced several features that support the 5nm process including stacked gate support, universal poly grid snapping, area-based rule support, asymmetric coloring and voltage-dependent rule support, analog cell support and support for various new devices and design constraints that are part of TSMC’s 5nm technology offering.

Schematic to Layout Design Flow in Cadence Virtuoso

This video will guide you to how to do circuit design in Cadence Virtuoso schematic and making its layout

Cadence enables electronic systems and semiconductor companies to create the innovative end products that are transforming the way people live, work and play. Cadence software, hardware and semiconductor IP are used by customers to deliver products to market faster. The company’s System Design Enablement strategy helps customers develop differentiated products—from chips to boards to systems—in mobile, consumer, cloud datacenter, automotive, aerospace, IoT, industrial and other market segments. Cadence is listed as one of Fortune Magazine's 100 Best Companies to Work

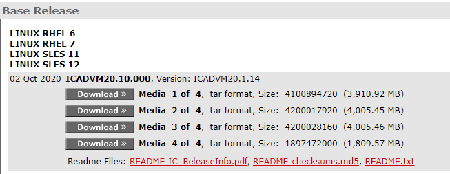

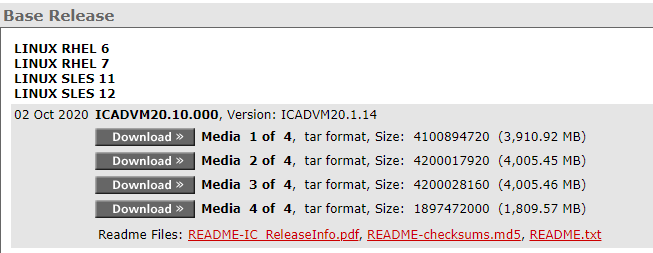

Product: Cadence Virtuoso ICADVM

Version: 20.10.000 Base

Supported Architectures: lnx86

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 10.1 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please