Cadence Sigrity and Systems Analysis 2023.1 HF003 Linux | 29.5 Gb

Cadence Design Systems, Inc., a leader in global electronic design innovation, is pleased to announce the availability of Sigrity and Systems Analysis 2023.1 HF003 (23.10.300) is a supplier of software for IC package physical design and for analyzing power integrity and signal integrity.

Sigrity and Systems Analysis 2023.1 HF3 Release - Date: 12-22-2023

2864358 3D_FDTD Add units to the field plots in Clarity 3D Transient Solver

2883040 3D_FDTD The Field Output results are not displayed when opened from the menu in Clarity 3D Transient Solver

2899832 CLARITYQS A medium-sized design cannot be completed in Sigrity2023.1 HF2 in mesh iteration stage but works in Sigrity2023.1 HF1

2637391 CLARITY A design works with 'D Mesh' but fails using 'X Mesh' in Clarity 3D Workbench

2709977 CLARITY Polygon simplification prevents initial mesh from starting in Clarity 3D Layout and Clarity 3D Workbench

2714140 CLARITY The Z coordinate of a new oblong based on start node and end node cannot be changed in Clarity 3D Workbench

2837823 CLARITY S-parameter files generated when wave ports are used are not recognized as Touchstone

2849630 CLARITY A waveport design is simulated correctly after removing the DC point

2871948 CLARITY LMesh fails if the dielectric is not specified on the inner trace in trace coating

2875045 CLARITY Cannot change the port sequence because the terminals from the same surface are not sequential

2877294 CLARITY Change the flex bending radius definition in Clarity 3D Workbench

2878257 CLARITY Clarity 3D Workbench exits unexpectedly when launched from a Clarity 3D Layout model containing dielectrics blocks

2880015 CLARITY Flex translation issue occurs when translating from Clarity 3D Layout to Clarity 3D Workbench

2882393 CLARITY The S-parameter results show no difference with the capacitators enabled or disabled

2886572 CLARITY Postprocessing exits unexpectedly when clicking Composite Excitation

2890682 CLARITY The quasi-static solver fails on DTC structures

2893011 CLARITY The de-embedding direction shown in GUI is wrong

2893214 CLARITY Incorrect translation of void shape occurs from GDS database

2893489 CLARITY Circuit ports are incomplete in XMesh

2894047 CLARITY Clarity 3D Workbench fails to translate the SPD file with a specific translation option

2895894 CLARITY Short errors were found after translating SPD to Clarity 3D Workbench

2899318 CLARITY Clarity 3D Workbench creates unnecessary short edges in the geometry compared to Clarity 3D layout SPD

2906445 CLARITY Etching structure is wrong when translated from Clarity 3D Layout to Clarity 3D Workbench

2909235 CLARITY Cannot import a file in Clarity 3D Workbench in Sigrity2023.1 HF2

2860353 OPTIMIZEPI Fix the OptimizePI PowerTree setup

2890698 OPTIMIZEPI Reusing the SPD file in OptimizePI loads the impedance observation points and the decoupling capacitors are grayed out

2859463 POWERDC The Generate Comparison Report option is missing from PowerTree in the Sigrity2023.1 release

2868473 POWERDC Converting .htm report to PDF using the Tcl script does not work in PowerDC

2880708 POWERDC PowerDC simulation runs fine in Sigrity2022.1 HF5 but not in Sigrity 2023.1 HF1

2887886 POWERDC In PowerDC results, the absolute voltage is missing for a few pins in the Other Component Voltage section

2891542 POWERDC For a certification case, PowerDC does not show any VSS drop value

2908610 POWERDC PowerDC exits unexpectedly when Optimal Sense Location is enabled

2893068 POWERSI An SPD file cannot be opened in PowerSI in Sigrity2023.1 HF2

2827033 SIGRITY_SUITE Enhance Clarity 3D Layout to allow parametric import in Clarity 3D Workbench

2858305 SIGRITY_SUITE Simulation failed in Clarity 3D Layout and PowerSI

2858311 SIGRITY_SUITE Some of the traces are deleted after applying cut by layer

2863562 SIGRITY_SUITE Sigrity common UI display bug issue occurs due to Qt & MFC draw box logic inconsistency that introduces pixel mismatch

2866324 SIGRITY_SUITE Default Model Library Issues

2867866 SIGRITY_SUITE Clarity 3D Workbench cannot perform translation with port defined in the SPD file

2869117 SIGRITY_SUITE Loading/running TCL script for Clarity IC extraction takes longer to run

2881370 SIGRITY_SUITE The ASI_MODEL property is not recognized when opening Assign Models

2881406 SIGRITY_SUITE The assigned model is not displayed even if the Resister Model is assigned from Browse Model

2883935 SIGRITY_SUITE IBIS Model Assignment Component pin mismatch occurs in AMM library

2892410 SIGRITY_SUITE PowerSI fails to run with via backdrill in the attached test case

2898770 SIGRITY_SUITE Clarity coaxial lumped port is generated on an incorrect layer

2898776 SIGRITY_SUITE Clarity 3D Layout creates shorts during lumped port generation

2903900 SIGRITY_SUITE Reuse SPD does not import Multi-phase VRMs and Reference Node

2873438 TRANSLATOR Clarity 3D Layout exits unexpectedly when loading a brd file

2875895 TRANSLATOR Translation of a net with more than three alias nets does not work

2879211 TRANSLATOR Gds2Spd average_above and average_below do not work in the Sigrity2023.1 HF2 release

2882432 TRANSLATOR Importing an mcm file in layout with automatic bump creation set to 'Always' creates shorts in the attached design

2909493 TRANSLATOR The via connected to the same net shape behavior changed

2670293 XCITEPI Four bumps are being generated for each pad

2874119 XCITEPI XcitePI generates multiple tsv bumps for the attached case

2879201 XCITEPI Xcitepigen generates a rounding error for an encrypted ICT file

2901788 XCITEPI Bug in iRCX file in XcitePI

2883040 3D_FDTD The Field Output results are not displayed when opened from the menu in Clarity 3D Transient Solver

2899832 CLARITYQS A medium-sized design cannot be completed in Sigrity2023.1 HF2 in mesh iteration stage but works in Sigrity2023.1 HF1

2637391 CLARITY A design works with 'D Mesh' but fails using 'X Mesh' in Clarity 3D Workbench

2709977 CLARITY Polygon simplification prevents initial mesh from starting in Clarity 3D Layout and Clarity 3D Workbench

2714140 CLARITY The Z coordinate of a new oblong based on start node and end node cannot be changed in Clarity 3D Workbench

2837823 CLARITY S-parameter files generated when wave ports are used are not recognized as Touchstone

2849630 CLARITY A waveport design is simulated correctly after removing the DC point

2871948 CLARITY LMesh fails if the dielectric is not specified on the inner trace in trace coating

2875045 CLARITY Cannot change the port sequence because the terminals from the same surface are not sequential

2877294 CLARITY Change the flex bending radius definition in Clarity 3D Workbench

2878257 CLARITY Clarity 3D Workbench exits unexpectedly when launched from a Clarity 3D Layout model containing dielectrics blocks

2880015 CLARITY Flex translation issue occurs when translating from Clarity 3D Layout to Clarity 3D Workbench

2882393 CLARITY The S-parameter results show no difference with the capacitators enabled or disabled

2886572 CLARITY Postprocessing exits unexpectedly when clicking Composite Excitation

2890682 CLARITY The quasi-static solver fails on DTC structures

2893011 CLARITY The de-embedding direction shown in GUI is wrong

2893214 CLARITY Incorrect translation of void shape occurs from GDS database

2893489 CLARITY Circuit ports are incomplete in XMesh

2894047 CLARITY Clarity 3D Workbench fails to translate the SPD file with a specific translation option

2895894 CLARITY Short errors were found after translating SPD to Clarity 3D Workbench

2899318 CLARITY Clarity 3D Workbench creates unnecessary short edges in the geometry compared to Clarity 3D layout SPD

2906445 CLARITY Etching structure is wrong when translated from Clarity 3D Layout to Clarity 3D Workbench

2909235 CLARITY Cannot import a file in Clarity 3D Workbench in Sigrity2023.1 HF2

2860353 OPTIMIZEPI Fix the OptimizePI PowerTree setup

2890698 OPTIMIZEPI Reusing the SPD file in OptimizePI loads the impedance observation points and the decoupling capacitors are grayed out

2859463 POWERDC The Generate Comparison Report option is missing from PowerTree in the Sigrity2023.1 release

2868473 POWERDC Converting .htm report to PDF using the Tcl script does not work in PowerDC

2880708 POWERDC PowerDC simulation runs fine in Sigrity2022.1 HF5 but not in Sigrity 2023.1 HF1

2887886 POWERDC In PowerDC results, the absolute voltage is missing for a few pins in the Other Component Voltage section

2891542 POWERDC For a certification case, PowerDC does not show any VSS drop value

2908610 POWERDC PowerDC exits unexpectedly when Optimal Sense Location is enabled

2893068 POWERSI An SPD file cannot be opened in PowerSI in Sigrity2023.1 HF2

2827033 SIGRITY_SUITE Enhance Clarity 3D Layout to allow parametric import in Clarity 3D Workbench

2858305 SIGRITY_SUITE Simulation failed in Clarity 3D Layout and PowerSI

2858311 SIGRITY_SUITE Some of the traces are deleted after applying cut by layer

2863562 SIGRITY_SUITE Sigrity common UI display bug issue occurs due to Qt & MFC draw box logic inconsistency that introduces pixel mismatch

2866324 SIGRITY_SUITE Default Model Library Issues

2867866 SIGRITY_SUITE Clarity 3D Workbench cannot perform translation with port defined in the SPD file

2869117 SIGRITY_SUITE Loading/running TCL script for Clarity IC extraction takes longer to run

2881370 SIGRITY_SUITE The ASI_MODEL property is not recognized when opening Assign Models

2881406 SIGRITY_SUITE The assigned model is not displayed even if the Resister Model is assigned from Browse Model

2883935 SIGRITY_SUITE IBIS Model Assignment Component pin mismatch occurs in AMM library

2892410 SIGRITY_SUITE PowerSI fails to run with via backdrill in the attached test case

2898770 SIGRITY_SUITE Clarity coaxial lumped port is generated on an incorrect layer

2898776 SIGRITY_SUITE Clarity 3D Layout creates shorts during lumped port generation

2903900 SIGRITY_SUITE Reuse SPD does not import Multi-phase VRMs and Reference Node

2873438 TRANSLATOR Clarity 3D Layout exits unexpectedly when loading a brd file

2875895 TRANSLATOR Translation of a net with more than three alias nets does not work

2879211 TRANSLATOR Gds2Spd average_above and average_below do not work in the Sigrity2023.1 HF2 release

2882432 TRANSLATOR Importing an mcm file in layout with automatic bump creation set to 'Always' creates shorts in the attached design

2909493 TRANSLATOR The via connected to the same net shape behavior changed

2670293 XCITEPI Four bumps are being generated for each pad

2874119 XCITEPI XcitePI generates multiple tsv bumps for the attached case

2879201 XCITEPI Xcitepigen generates a rounding error for an encrypted ICT file

2901788 XCITEPI Bug in iRCX file in XcitePI

Cadence Sigrity provides a rich set of gigabit signal and power network analysis technologies, including a unique power-aware signal integrity analysis capability for system, printed circuit board (PCB), and IC package designs. The combination of Sigrity analysis technologies with Cadence Allegro and OrCAD design tools will provide a comprehensive front-to-back integrated flow to enable system and semiconductor companies to deliver high-performance devices employing gigabit interface protocols such as DDR and PCI Express. The integrated solution will particularly benefit customers delivering electronic systems in high-growth markets such as mobile multimedia devices and cloud computing infrastructure.

Systems Analysis products complement Sigrity tools and are focused on complete systems. Thermal, EMI, RF, and extraction simulations include design data beyond ECAD and often include MCAD components such as antennas, cables, connectors and enclosures.

Cadence Sigrity: How to Avoid Power Delivery Problems in your PCBs

Ensure uniform current density in your design and put a stop to the additional time and money spent on troubleshooting hard to find power delivery network issues in the lab with Allegro In-Design Analysis powered by Sigrity.

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For eight years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work.

Owner: Cadence Design Systems

Product Name: Sigrity and Systems Analysis

Version: 2023.1 HF003 (23.10.300) *

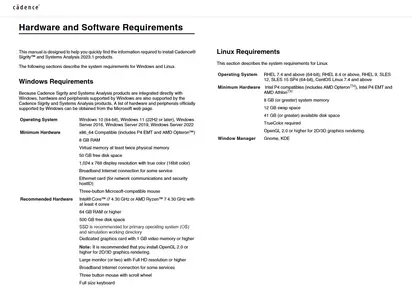

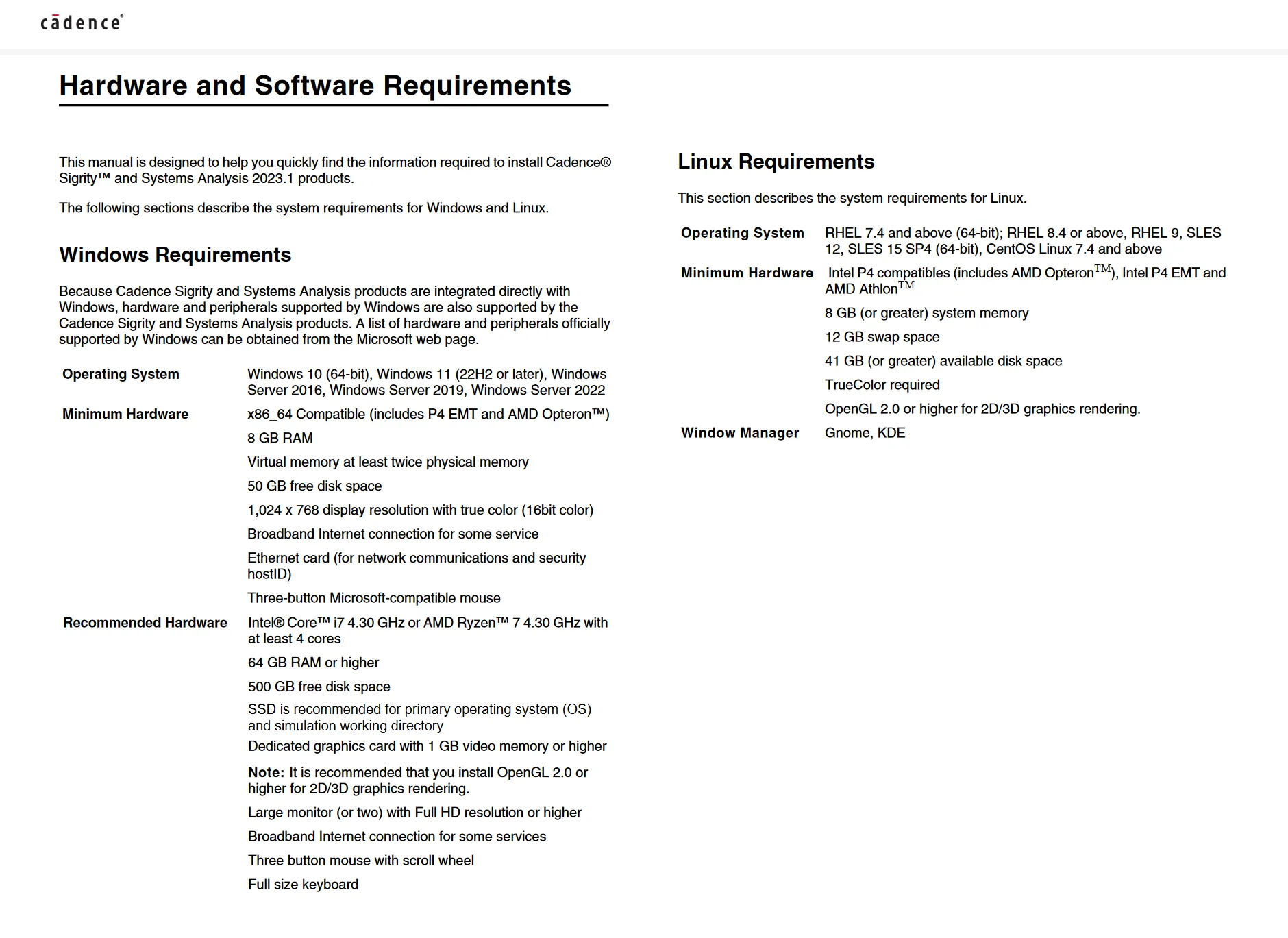

Supported Architectures: x64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux **

Size: 29.5 Gb

Base_SIG23.10.000_lnx86

Hotfix_SIG23.10.300-HF3_lnx86

Hotfix_SIG23.10.300-HF3_lnx86

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please