Cadence SPB Allegro and OrCAD 17.40.000-2022 HF037 | 7.6 Gb

The Cadence released HotFix 037 for OrCAD and Allegro 17.40.000-2022 is a sleeker and more modern version of the OrCAD and Allegro release, with enhanced usability and a slew of new productivity- enhancing features.

Cadence OrCAD and Allegro: What’s New in 17.40.037-2022 - Date: 06-09-2023

===================================================

CCRID Product ProductLevel2 Title

=======================================================

2763680 ADW FLOW_MGR Java certificate has expired

2755074 ALLEGRO_EDITOR 3D_CANVAS Incorrect bend radius when measured in 3D Canvas

2684422 ALLEGRO_EDITOR DATABASE Support for Nodrc_Component_Board_Overlap on Place Bound in Embedded Geometry Class

2726479 ALLEGRO_EDITOR DFA No DFA bubble appears for bottom side of design

2759267 ALLEGRO_EDITOR DFA DFA bubble no longer appears between components and through-hole pins after upgrading to 17.4

2731114 ALLEGRO_EDITOR DFM Silkscreen DFF check compares SS on TOP vs Solder mask on BOTTOM

2758861 ALLEGRO_EDITOR DFM DFF is not catching silkscreen that overlaps soldermask openings that are not associated with pins or vias

2692193 ALLEGRO_EDITOR DRC_CONSTR Import/Export constraints not working is all the options are selected

2752572 ALLEGRO_EDITOR DRC_CONSTR DFF Mask Slivers DRCs not flagged for subclasses not in stackup subclass group

2581646 ALLEGRO_EDITOR GRAPHICS Screen is not refreshing properly with nVidia RTX A2000 after installing HotFix 022 of Release 17.4-2019

2748880 ALLEGRO_EDITOR GRAPHICS Vias in QFN footprint display as pins not vias

2776902 ALLEGRO_EDITOR IPC Error (SPMHGE-268) appears but the Log file is empty.

2751853 ALLEGRO_EDITOR MCAD_COLLAB IDF Import not using the package symbol defined in emn file

2691946 ALLEGRO_EDITOR NC Donut pad creates wrong drill span

2701574 ALLEGRO_EDITOR NC NC Drill cannot detect counter sink drill

2712776 ALLEGRO_EDITOR REPORTS axlReportGenerate() error message/popup

2783156 ALLEGRO_EDITOR REPORTS axlReportGenerate with g_showReport nil cause error.

2784385 ALLEGRO_EDITOR REPORTS Error on axlReportGenerate

2781143 ALLEGRO_EDITOR SCHEM_FTB Component unplaced in System Capture on renaming RefDes

2796334 ALLEGRO_EDITOR SCHEM_FTB Components/Footprints are removed from board db after importing updated netlist file from Capture for attached test

2733186 ALLEGRO_EDITOR SHAPE Venture displays less performance than Designer license

2735260 ALLEGRO_EDITOR SHAPE Allegro PCB Editor stops responding on importing subdrawing

2764567 ALLEGRO_EDITOR SHAPE Allegro PCB Editor stops responding or exits with error while updating shape

2769657 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes when shape is edited

2798242 ALLEGRO_EDITOR SHAPE Crash when changing all static shapes on all layers to dynamic shapes or refreshing the shapes after changing

2773690 ALLEGRO_EDITOR SKILL axlDBCheck appears broken: The results are different from UI

2731988 ALLEGRO_EDITOR UI_GENERAL Cannot set function key for Alt key

2751216 ALLEGRO_EDITOR UI_GENERAL SKILL slower in releases 17.4-2019, HotFix 035 and 22.1, HotFix 002 than in release 17.2-2016, HotFix 079

2774400 ALLEGRO_VIEWER OTHER Allegro Free Physical Viewer: Incorrect project path on title bar and 'color load' not running

2745491 APD DRC_CONSTRAIN Function to check Etch-Back mask spacing

2779880 APD EXPORT_DATA Allegro Package Designer Plus: Time Delay report and Net Delay reports show different pin delays

2696789 APD INTERACTIVE Release 17.4-2019: 'Oops' after 'Edit' - 'Copy' followed by 'Move' resets starting origin in APD Plus

2763227 APD INTERACTIVE Find by Query with zero connection filter returning shapes with connections

2772712 APD INTERACTIVE Relative pick copy increments to new coordinate after clicking 'oops' and doing the pick again

2774190 APD INTERACTIVE 'oops' not working correctly during copy with incremental coordinates

2781882 APD INTERACTIVE In copy command, when using ix, oops improperly changes the reference location

2783620 APD INTERACTIVE 'Copy Via' and 'Oops' behavior: Resetting origin after 'Oops'

2801075 APD INTERACTIVE Query shape the parameter "Connection Number"

2784133 APD PLACEMENT Mirror Geometry does not work with BGA components.

2698597 CAPTURE CONSTRAINT_MG Rotated components copy Voltage value of CM to other net

2643208 CAPTURE LIBRARY OLBs on server path are not accessible when VPN is disconnected momentarily and reconnected again

2758532 CAPTURE LIBRARY OrCAD Capture stops responding when specific parts are updated

2512084 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2517769 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2522968 CAPTURE NETLISTS Netlist cannot be created after successful backannotation on the schematic

2720787 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2735713 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2743736 CAPTURE NETLISTS Netlist generation fails if pin swap is done between pins with different names across sections of a heterogeneous part

2752229 CAPTURE NETLISTS OrCAD Capture cannot update layout after successful backannotation from board to schematic.

2273620 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes more time in release 17.4-2019 than 17.2

2288828 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing with Allegro PCB Editor

2549412 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2575982 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2578090 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2585589 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing with Allegro PCB Editor

2612076 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing with Allegro PCB Editor

2693657 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2743729 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2745036 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding when multiple components are selected in Allegro PCB Editor simultaneously.

2746742 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing

2757949 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding when global nets are selected in Allegro PCB Editor.

2763068 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2312843 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2321565 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2323303 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2349502 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2411581 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2760463 CONCEPT_HDL AWR_TRANSLATO con2ul is not creating symbol views for a cell but reports that symbol view has been created

2792903 CONCEPT_HDL CORE Port group mapping issue with swap

2751889 CONCEPT_HDL OTHER Check SPCOCN-2089 not working.

2527679 CONSTRAINT_MGR INTERACTIV Do not export technology file with Physical/Spacing constraint data and no cross-section data

2762710 CONSTRAINT_MGR XNET_DIFFPAIR Disjointed design link extraction with SigXplorer

2759576 PCB_LIBRARIAN SYMBOL_EDITOR Master.tag is missing when creating new section in new Symbol Editor.

2781987 PCB_LIBRARIAN SYMBOL_EDITOR Part Developer does not generate complete verilog.v file when the master.tag file is missing

2767690 PSPICE SLPS PSpice SLPS multiple include file issues

2805032 PULSE ADHOC Opening project in gives warning CPBF-122 regarding conflicting projects

2769748 PULSE LIVEBOM Live BOM configuration list contains duplicate entries

2799108 PULSE MISCELLANEOUS Library Analysis utility fails to run if a 32-bit JRE is in system path

1451009 SIP_LAYOUT SHAPE Dynamic shape not showing the effect of aperture selection

1579231 SIP_LAYOUT SHAPE Rounding error shape minimum aperture for gap width

1689673 SIP_LAYOUT SHAPE Dynamic shape parameter is required for Min Shape Width regulation

1775149 SIP_LAYOUT SHAPE Shape for plane violates the 25-micron aperture setting causing manufacturing error

2024881 SIP_LAYOUT SHAPE Shape created with lesser copper between design elements than the constraint value

2038962 SIP_LAYOUT SHAPE Min aperture for gap width error not clearing shape properly

2102337 SIP_LAYOUT SHAPE Acute angles in dynamic shape

2287179 SIP_LAYOUT SHAPE Shape gap is less than minimum aperture for gap width setting

2321242 SIP_LAYOUT SHAPE Broken shape and Same Net Spacing issues and errors

2639368 SIP_LAYOUT SHAPE "Minimum aperture for gap width" does not work.

2686563 SIP_LAYOUT SHAPE Spikes in auto-voiding of dynamic shapes

2715338 SIP_LAYOUT SHAPE Spike in dynamic shape

861220 SIP_LAYOUT SHAPE Sharp angles in shapes causing excessive clearance

2766182 SYSTEM_CAPTURE ARCHIVER Archiver gives missing archiver.log error

2721060 SYSTEM_CAPTURE MISCELLANEOUS Power net names wrong in PNN mode

2733432 SYSTEM_CAPTURE MISCELLANEOUS rundbdoctor in PNN mode changes HDL_POWER value

2745819 SYSTEM_CAPTURE PACKAGER Increase of .sdax file size

2781518 SYSTEM_CAPTURE PACKAGER Unable to open design because of missing xcon file.

2793822 SYSTEM_CAPTURE PREFERENCES Reset shortcut in Preferences does not work correctly if CDS_CP_TRANSLATION_LANGUAGE

2770726 SYSTEM_CAPTURE REPLACE Part Manager crashes without updating parts

2774911 SYSTEM_CAPTURE REPLACE Some nets are not connected properly

2772456 SYSTEM_CAPTURE UI System Capture: large number of random crashes reported

2783471 SYSTEM_CAPTURE UI Physical Net Names are not updated dynamically as per the BLOCK_SUFFIX_PROP in System Capture.

2785217 SYSTEM_CAPTURE VARIANT_MANAG Variant Editor does not allow part substitutions between mechanical parts without footprints

2791593 SYSTEM_CAPTURE VARIANT_MANAG Variant Editor in System Capture is not always saving data correctly on migrated designs

2792599 SYSTEM_CAPTURE VARIANT_MANAG CPCB-72 error - Variant lst file could not be generated.

2791332 SYSTEM_CAPTURE WIRING Pressing undo after moving a group selection selects other items on the canvas which leads to invalid connectivity

2754092 SYS_RELIABILITY AUDIT_RULES 'Component Property offset' audit rule does not show property name

CCRID Product ProductLevel2 Title

=======================================================

2763680 ADW FLOW_MGR Java certificate has expired

2755074 ALLEGRO_EDITOR 3D_CANVAS Incorrect bend radius when measured in 3D Canvas

2684422 ALLEGRO_EDITOR DATABASE Support for Nodrc_Component_Board_Overlap on Place Bound in Embedded Geometry Class

2726479 ALLEGRO_EDITOR DFA No DFA bubble appears for bottom side of design

2759267 ALLEGRO_EDITOR DFA DFA bubble no longer appears between components and through-hole pins after upgrading to 17.4

2731114 ALLEGRO_EDITOR DFM Silkscreen DFF check compares SS on TOP vs Solder mask on BOTTOM

2758861 ALLEGRO_EDITOR DFM DFF is not catching silkscreen that overlaps soldermask openings that are not associated with pins or vias

2692193 ALLEGRO_EDITOR DRC_CONSTR Import/Export constraints not working is all the options are selected

2752572 ALLEGRO_EDITOR DRC_CONSTR DFF Mask Slivers DRCs not flagged for subclasses not in stackup subclass group

2581646 ALLEGRO_EDITOR GRAPHICS Screen is not refreshing properly with nVidia RTX A2000 after installing HotFix 022 of Release 17.4-2019

2748880 ALLEGRO_EDITOR GRAPHICS Vias in QFN footprint display as pins not vias

2776902 ALLEGRO_EDITOR IPC Error (SPMHGE-268) appears but the Log file is empty.

2751853 ALLEGRO_EDITOR MCAD_COLLAB IDF Import not using the package symbol defined in emn file

2691946 ALLEGRO_EDITOR NC Donut pad creates wrong drill span

2701574 ALLEGRO_EDITOR NC NC Drill cannot detect counter sink drill

2712776 ALLEGRO_EDITOR REPORTS axlReportGenerate() error message/popup

2783156 ALLEGRO_EDITOR REPORTS axlReportGenerate with g_showReport nil cause error.

2784385 ALLEGRO_EDITOR REPORTS Error on axlReportGenerate

2781143 ALLEGRO_EDITOR SCHEM_FTB Component unplaced in System Capture on renaming RefDes

2796334 ALLEGRO_EDITOR SCHEM_FTB Components/Footprints are removed from board db after importing updated netlist file from Capture for attached test

2733186 ALLEGRO_EDITOR SHAPE Venture displays less performance than Designer license

2735260 ALLEGRO_EDITOR SHAPE Allegro PCB Editor stops responding on importing subdrawing

2764567 ALLEGRO_EDITOR SHAPE Allegro PCB Editor stops responding or exits with error while updating shape

2769657 ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes when shape is edited

2798242 ALLEGRO_EDITOR SHAPE Crash when changing all static shapes on all layers to dynamic shapes or refreshing the shapes after changing

2773690 ALLEGRO_EDITOR SKILL axlDBCheck appears broken: The results are different from UI

2731988 ALLEGRO_EDITOR UI_GENERAL Cannot set function key for Alt key

2751216 ALLEGRO_EDITOR UI_GENERAL SKILL slower in releases 17.4-2019, HotFix 035 and 22.1, HotFix 002 than in release 17.2-2016, HotFix 079

2774400 ALLEGRO_VIEWER OTHER Allegro Free Physical Viewer: Incorrect project path on title bar and 'color load' not running

2745491 APD DRC_CONSTRAIN Function to check Etch-Back mask spacing

2779880 APD EXPORT_DATA Allegro Package Designer Plus: Time Delay report and Net Delay reports show different pin delays

2696789 APD INTERACTIVE Release 17.4-2019: 'Oops' after 'Edit' - 'Copy' followed by 'Move' resets starting origin in APD Plus

2763227 APD INTERACTIVE Find by Query with zero connection filter returning shapes with connections

2772712 APD INTERACTIVE Relative pick copy increments to new coordinate after clicking 'oops' and doing the pick again

2774190 APD INTERACTIVE 'oops' not working correctly during copy with incremental coordinates

2781882 APD INTERACTIVE In copy command, when using ix, oops improperly changes the reference location

2783620 APD INTERACTIVE 'Copy Via' and 'Oops' behavior: Resetting origin after 'Oops'

2801075 APD INTERACTIVE Query shape the parameter "Connection Number"

2784133 APD PLACEMENT Mirror Geometry does not work with BGA components.

2698597 CAPTURE CONSTRAINT_MG Rotated components copy Voltage value of CM to other net

2643208 CAPTURE LIBRARY OLBs on server path are not accessible when VPN is disconnected momentarily and reconnected again

2758532 CAPTURE LIBRARY OrCAD Capture stops responding when specific parts are updated

2512084 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2517769 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2522968 CAPTURE NETLISTS Netlist cannot be created after successful backannotation on the schematic

2720787 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2735713 CAPTURE NETLISTS Netlist generation fails on swapping pins with different names across sections of a heterogeneous part

2743736 CAPTURE NETLISTS Netlist generation fails if pin swap is done between pins with different names across sections of a heterogeneous part

2752229 CAPTURE NETLISTS OrCAD Capture cannot update layout after successful backannotation from board to schematic.

2273620 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes more time in release 17.4-2019 than 17.2

2288828 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing with Allegro PCB Editor

2549412 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2575982 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2578090 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2585589 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing with Allegro PCB Editor

2612076 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing with Allegro PCB Editor

2693657 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2743729 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2745036 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding when multiple components are selected in Allegro PCB Editor simultaneously.

2746742 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding during cross-probing

2757949 CAPTURE NETLIST_ALLEG OrCAD Capture stops responding when global nets are selected in Allegro PCB Editor.

2763068 CAPTURE NETLIST_ALLEG Cross-probing between Allegro PCB Editor and OrCAD Capture takes significant time to complete

2312843 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2321565 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2323303 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2349502 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2411581 CAPTURE SCHEMATIC_EDI Parts cannot be placed on the schematic when the page is in floating state

2760463 CONCEPT_HDL AWR_TRANSLATO con2ul is not creating symbol views for a cell but reports that symbol view has been created

2792903 CONCEPT_HDL CORE Port group mapping issue with swap

2751889 CONCEPT_HDL OTHER Check SPCOCN-2089 not working.

2527679 CONSTRAINT_MGR INTERACTIV Do not export technology file with Physical/Spacing constraint data and no cross-section data

2762710 CONSTRAINT_MGR XNET_DIFFPAIR Disjointed design link extraction with SigXplorer

2759576 PCB_LIBRARIAN SYMBOL_EDITOR Master.tag is missing when creating new section in new Symbol Editor.

2781987 PCB_LIBRARIAN SYMBOL_EDITOR Part Developer does not generate complete verilog.v file when the master.tag file is missing

2767690 PSPICE SLPS PSpice SLPS multiple include file issues

2805032 PULSE ADHOC Opening project in gives warning CPBF-122 regarding conflicting projects

2769748 PULSE LIVEBOM Live BOM configuration list contains duplicate entries

2799108 PULSE MISCELLANEOUS Library Analysis utility fails to run if a 32-bit JRE is in system path

1451009 SIP_LAYOUT SHAPE Dynamic shape not showing the effect of aperture selection

1579231 SIP_LAYOUT SHAPE Rounding error shape minimum aperture for gap width

1689673 SIP_LAYOUT SHAPE Dynamic shape parameter is required for Min Shape Width regulation

1775149 SIP_LAYOUT SHAPE Shape for plane violates the 25-micron aperture setting causing manufacturing error

2024881 SIP_LAYOUT SHAPE Shape created with lesser copper between design elements than the constraint value

2038962 SIP_LAYOUT SHAPE Min aperture for gap width error not clearing shape properly

2102337 SIP_LAYOUT SHAPE Acute angles in dynamic shape

2287179 SIP_LAYOUT SHAPE Shape gap is less than minimum aperture for gap width setting

2321242 SIP_LAYOUT SHAPE Broken shape and Same Net Spacing issues and errors

2639368 SIP_LAYOUT SHAPE "Minimum aperture for gap width" does not work.

2686563 SIP_LAYOUT SHAPE Spikes in auto-voiding of dynamic shapes

2715338 SIP_LAYOUT SHAPE Spike in dynamic shape

861220 SIP_LAYOUT SHAPE Sharp angles in shapes causing excessive clearance

2766182 SYSTEM_CAPTURE ARCHIVER Archiver gives missing archiver.log error

2721060 SYSTEM_CAPTURE MISCELLANEOUS Power net names wrong in PNN mode

2733432 SYSTEM_CAPTURE MISCELLANEOUS rundbdoctor in PNN mode changes HDL_POWER value

2745819 SYSTEM_CAPTURE PACKAGER Increase of .sdax file size

2781518 SYSTEM_CAPTURE PACKAGER Unable to open design because of missing xcon file.

2793822 SYSTEM_CAPTURE PREFERENCES Reset shortcut in Preferences does not work correctly if CDS_CP_TRANSLATION_LANGUAGE

2770726 SYSTEM_CAPTURE REPLACE Part Manager crashes without updating parts

2774911 SYSTEM_CAPTURE REPLACE Some nets are not connected properly

2772456 SYSTEM_CAPTURE UI System Capture: large number of random crashes reported

2783471 SYSTEM_CAPTURE UI Physical Net Names are not updated dynamically as per the BLOCK_SUFFIX_PROP in System Capture.

2785217 SYSTEM_CAPTURE VARIANT_MANAG Variant Editor does not allow part substitutions between mechanical parts without footprints

2791593 SYSTEM_CAPTURE VARIANT_MANAG Variant Editor in System Capture is not always saving data correctly on migrated designs

2792599 SYSTEM_CAPTURE VARIANT_MANAG CPCB-72 error - Variant lst file could not be generated.

2791332 SYSTEM_CAPTURE WIRING Pressing undo after moving a group selection selects other items on the canvas which leads to invalid connectivity

2754092 SYS_RELIABILITY AUDIT_RULES 'Component Property offset' audit rule does not show property name

Cadence Allegro PCB Design helps bring your innovative and bleeding-edge designs to life. The constraint-driven environment provides real-time visual feedback and ensures the functionality and manufacturability of your PCBs while allowing you to keep designing.

Cadence OrCAD is a driving force in the PCB design industry. In order to help desingers keep up with the constant pace of change Cadence has been accelerating the pace of innovation delivering a stream of updates and product enhancements to users. OrCAD provides insight into industry-first capabilities made available to customers such as real-time design, DesignTrue DFM, constraint manager, in-design analysis, and more.

Cadence OrCAD and Allegro 17.4-2019 is a sleeker and more modern version of the OrCAD and Allegro release, with enhanced usability and a slew of new productivity- enhancing features. You get more intuitive and easy- to- use flows that enable optimized schematic- to- board- to- manufacturing transitions. So, whether you design schematics, work with physical layouts, manage or create libraries and parts, or administer ECAD processes, there are features in this release that will benefit you.

Mar 31, 2022 · The Cadence released HotFix 028 (QIR4, indicated as 2022 in the application splash screens) for OrCAD and Allegro.

Tutorial OrCAD and Cadence Allegro PCB Editor | 2022 | Step by Step | For Beginners

After this tutorial you will know how to start designing your own boards in Cadence OrCAD and Allegro 17.4 . For everyone who would like to learn Allegro Design Entry CIS and Allegro PCB Editor and also for everyone who has never ever designed any boards, but would like to learn how to do it. Enjoy!

Cadence is a pivotal leader in electronic systems design, building upon more than 30 years of computational software expertise. The company applies its underlying Intelligent System Design strategy to deliver software, hardware and IP that turn design concepts into reality. Cadence customers are the world’s most innovative companies, delivering extraordinary electronic products from chips to boards to complete systems for the most dynamic market applications, including hyperscale computing, 5G communications, automotive, mobile, aerospace, consumer, industrial and healthcare. For eight years in a row, Fortune magazine has named Cadence one of the 100 Best Companies to Work.

Owner: Cadence

Product Name: SPB Allegro and OrCAD

Version: 17.40.033-2022 (HF037) Date: 06-09-2023

Supported Architectures: x64

Website Home Page : www.cadence.com

Languages Supported: english

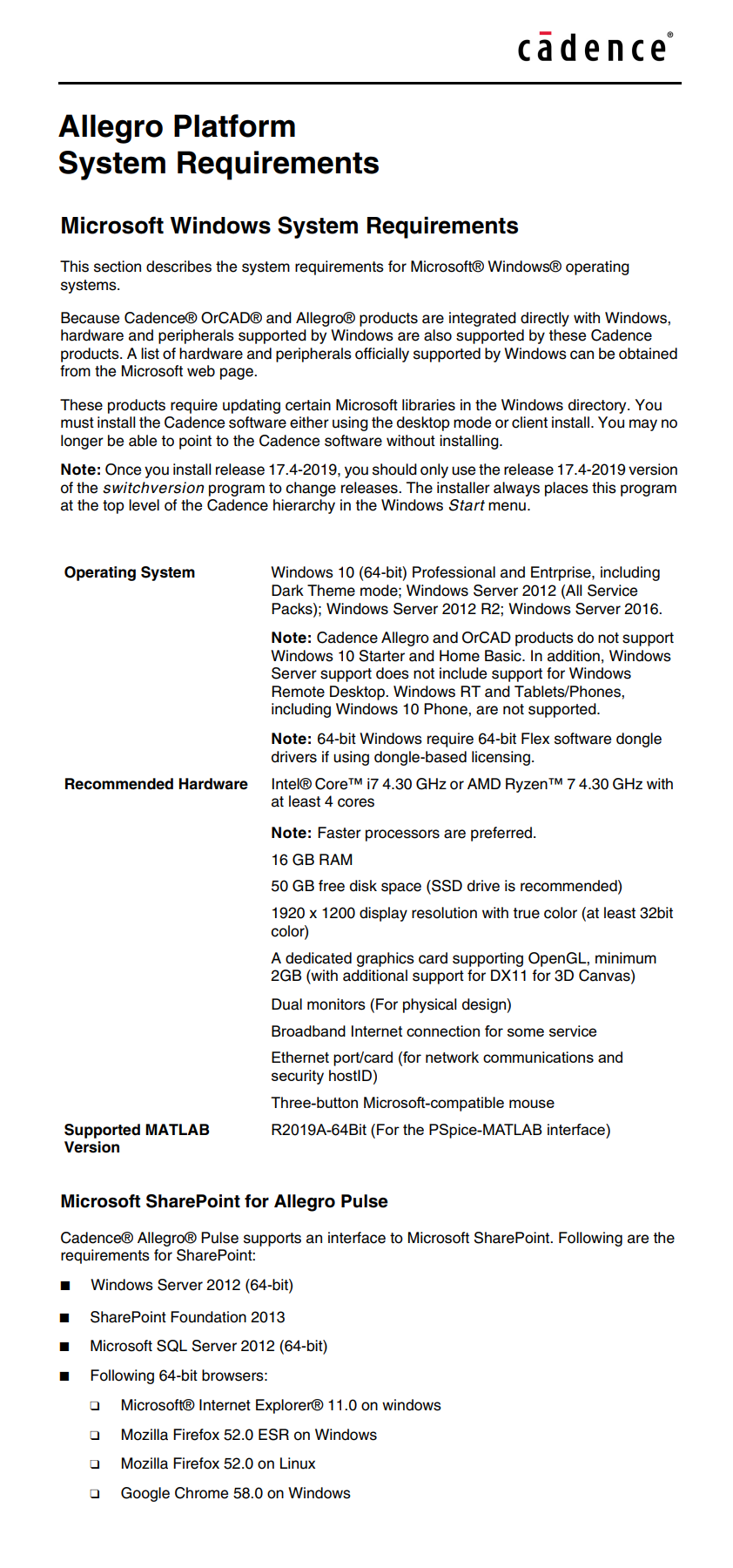

System Requirements: Windows *

Software Prerequisites: Cadence SPB Allegro and OrCAD 17.40.000 and above

Size: 7.6 Gb

Cadence SPB Allegro and OrCAD 17.40.000-2022 HF033

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please