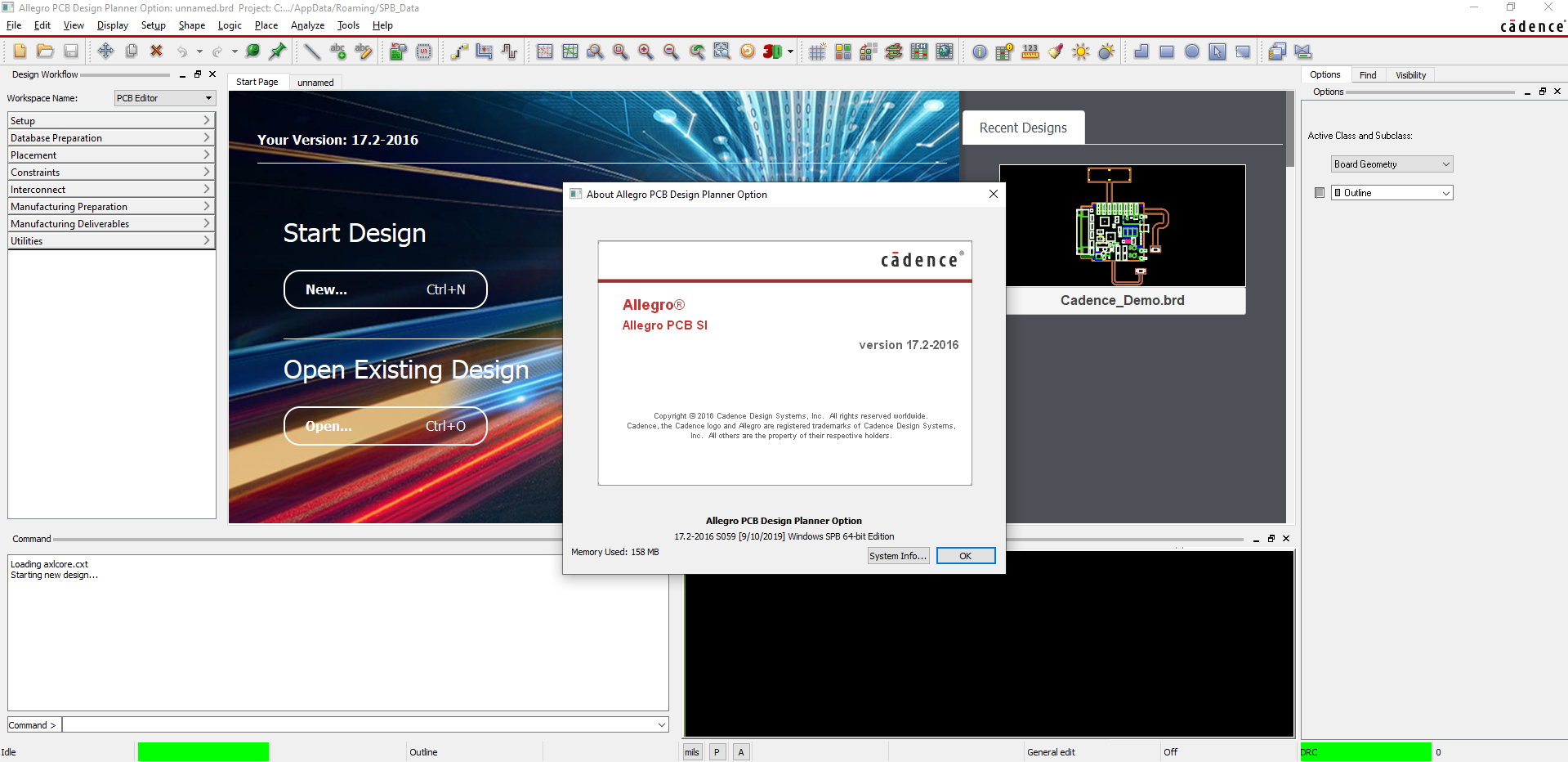

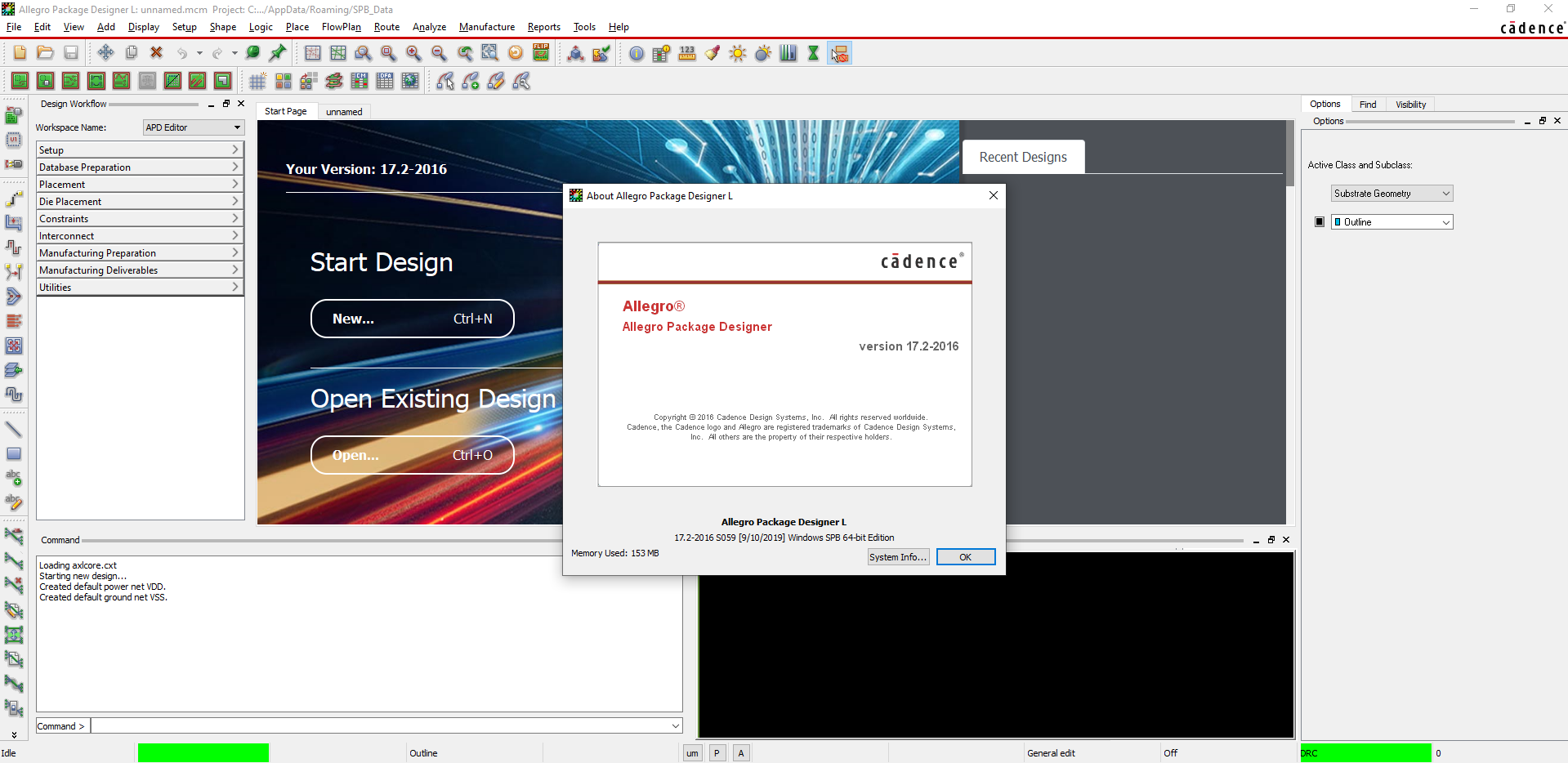

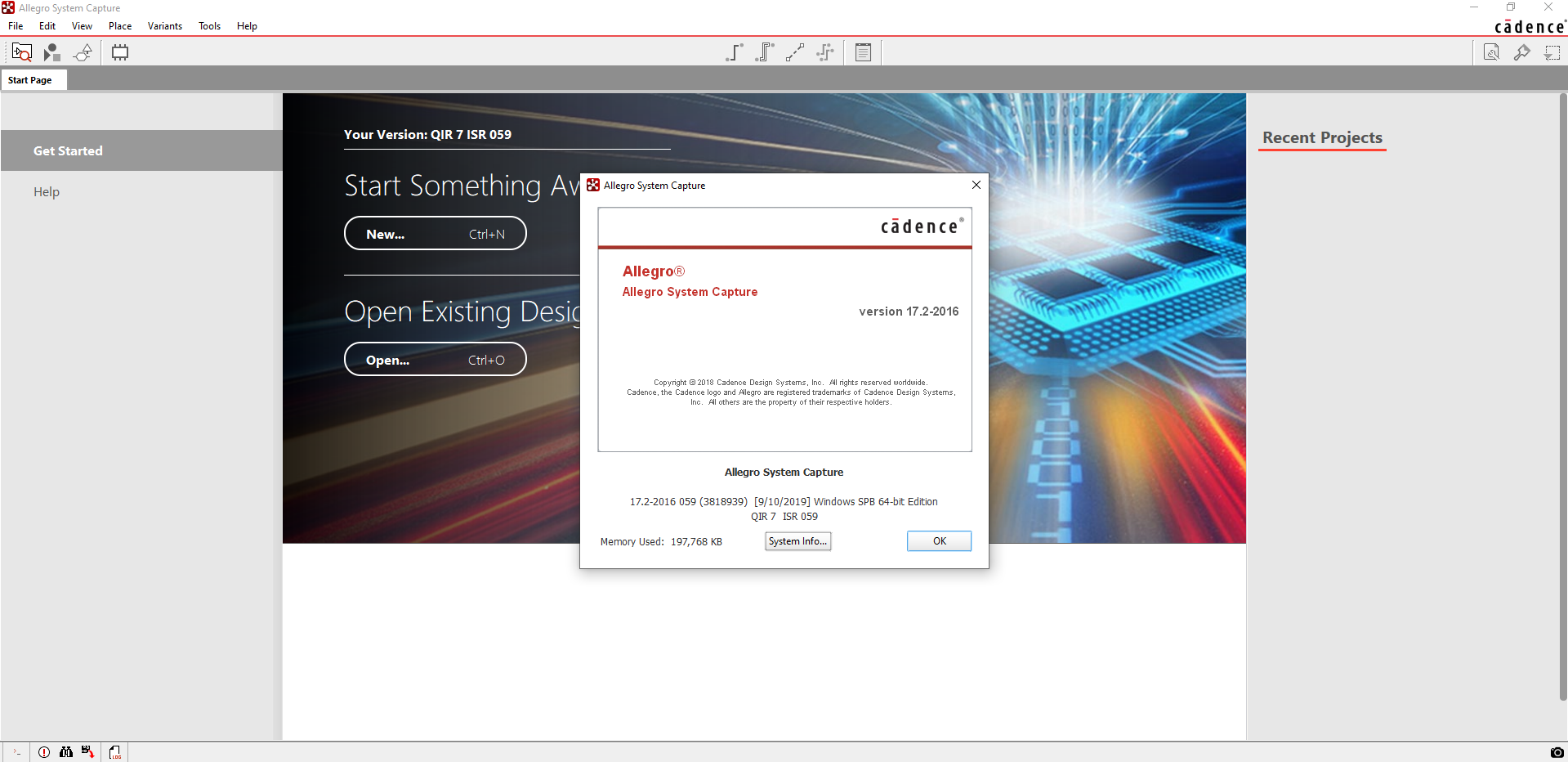

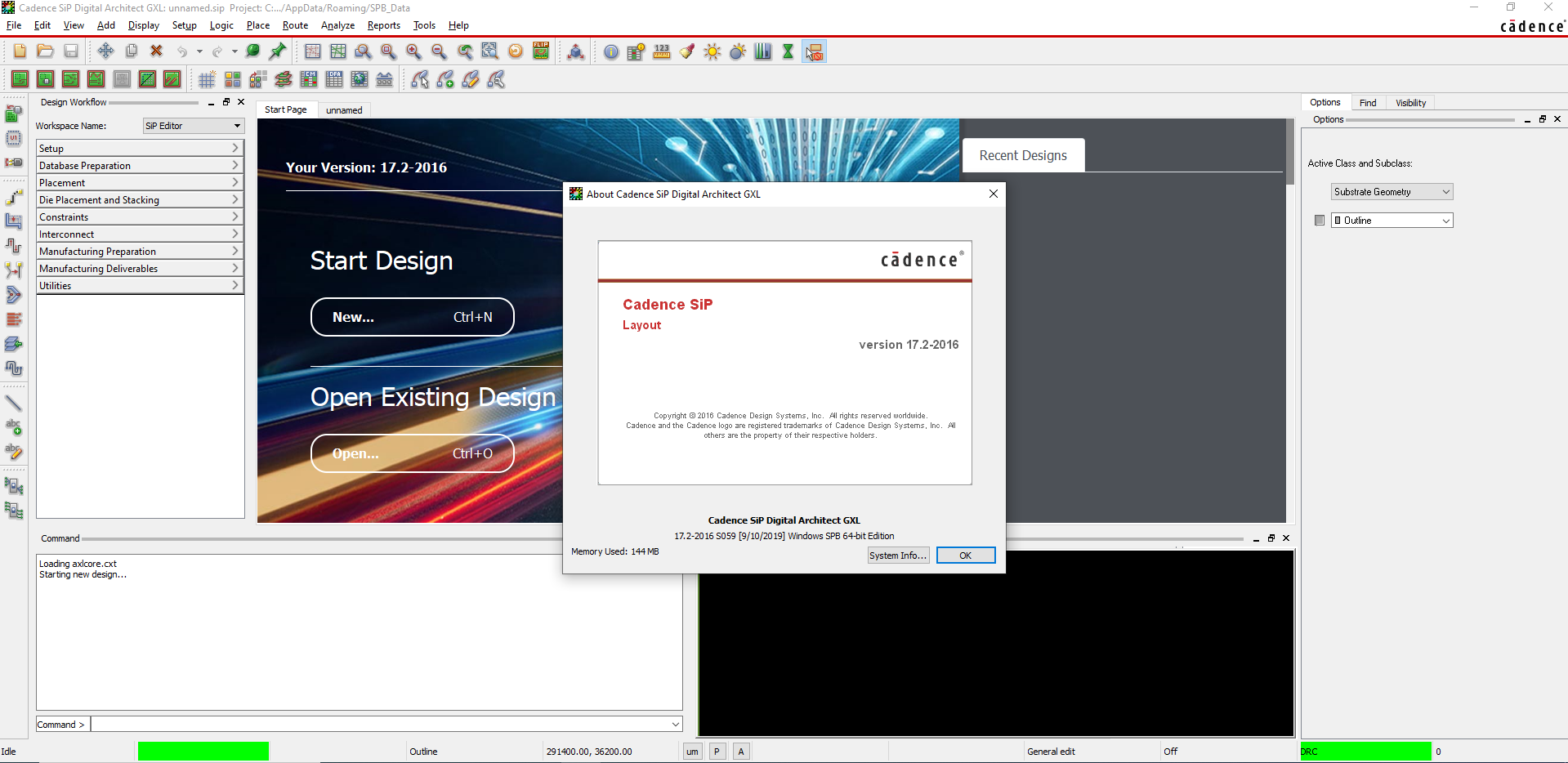

Cadence SPB Allegro and OrCAD 17.20.000-2016 HF059 | 3.9 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled a new of improvements to the Cadence SPB Allegro and OrCAD 17.20 families of products aimed at boosting performance and productivity through improvements features and big fixed issues.

- ADW DBEDITOR Icons in DBEditor do not start applications after renaming a model

- ADW LIBIMPORT Missing alternate footprints from vault area after library import.

- ADW PART_BROWSER Component Browser does not start after installing HotFix 057 of release 17.2-2016

- ALLEGRO_EDITOR ARTWORK Coverlay details not being output to Artwork data as per the visibility

- ALLEGRO_EDITOR ARTWORK Artwork dimensions do not match Allegro PCB Editor

- ALLEGRO_EDITOR DATABASE Through hole mechanical pin in zone area without Soldermask Top still shows a pad on Soldermask Top

- ALLEGRO_EDITOR DATABASE No soldermask for mechanical holes within zone

- ALLEGRO_EDITOR DATABASE Unused Pad Suppression removes pin connected to shape using Net_short property

- ALLEGRO_EDITOR EDIT_ETCH Allegro PCB Editor crashes when routing with VOID_SAME_NET property on cline

- ALLEGRO_EDITOR INTERACTIV GUI ( Quickplace ) not adjusted to current resolution

- ALLEGRO_EDITOR INTERACTIV Quickplace GUI not adjusted to lower resolution

- ALLEGRO_EDITOR INTERACTIV Dialog boxes do not fit vertically on the screen

- ALLEGRO_EDITOR INTERACTIV Quickplace pop-up window does not fit vertically on the screen

- ALLEGRO_EDITOR INTERACTIV Cannot resize or move dialog box to access buttons

- ALLEGRO_EDITOR IN_DESIGN_ANA Impedance vision data not available for cline segments for some nets

- ALLEGRO_EDITOR IN_DESIGN_ANA Impedance check results are incorrect and Crosstalk analysis stops running after updating to HotFix 057

- ALLEGRO_EDITOR NC Improve the User Preference description for BACKDRILL_OVERSIZE_OPTION

- ALLEGRO_EDITOR SCHEM_FTB Netrev.lst is written in the package folder

- ALLEGRO_EDITOR SCHEM_FTB netrev.lst is not created in the correct folder - error displayed for neltist import

- ALLEGRO_EDITOR SHAPE PCB Editor crashes while performing shape operation 'andnot'

- ALLEGRO_EDITOR SHAPE No Void Overlap option is not working in AMB

- ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes for a RAVEL rule

- ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes on creating dynamic shape

- ALLEGRO_PROD_TOOLB CORE Shield Router - cline end caps treated differently than cline-segment end caps

- ALLEGRO_PROD_TOOLB CORE Productivity Toolbox Z-DRC with multiple net classes: script selects only the last two classes in a group

- CAPTURE SCHEMATICS Slow response when selecting parts in schematic

- CAPTURE SCHEMATICS Slowness in OrCAD Capture when ITC is enabled

- CAPTURE SCHEMATICS Inter-tool communication needs to be disabled to resolve the lag issues in Capture

- RF_PCB ROUTING PCB Editor stops responding on using RF - Add Connect

- SCM OTHER Thevenin Termination dialog displays resistors incorrectly

- SIP_LAYOUT WLP Advanced WLP Non-standard fillets not working properly: fillets not added

- ADW LIBIMPORT Missing alternate footprints from vault area after library import.

- ADW PART_BROWSER Component Browser does not start after installing HotFix 057 of release 17.2-2016

- ALLEGRO_EDITOR ARTWORK Coverlay details not being output to Artwork data as per the visibility

- ALLEGRO_EDITOR ARTWORK Artwork dimensions do not match Allegro PCB Editor

- ALLEGRO_EDITOR DATABASE Through hole mechanical pin in zone area without Soldermask Top still shows a pad on Soldermask Top

- ALLEGRO_EDITOR DATABASE No soldermask for mechanical holes within zone

- ALLEGRO_EDITOR DATABASE Unused Pad Suppression removes pin connected to shape using Net_short property

- ALLEGRO_EDITOR EDIT_ETCH Allegro PCB Editor crashes when routing with VOID_SAME_NET property on cline

- ALLEGRO_EDITOR INTERACTIV GUI ( Quickplace ) not adjusted to current resolution

- ALLEGRO_EDITOR INTERACTIV Quickplace GUI not adjusted to lower resolution

- ALLEGRO_EDITOR INTERACTIV Dialog boxes do not fit vertically on the screen

- ALLEGRO_EDITOR INTERACTIV Quickplace pop-up window does not fit vertically on the screen

- ALLEGRO_EDITOR INTERACTIV Cannot resize or move dialog box to access buttons

- ALLEGRO_EDITOR IN_DESIGN_ANA Impedance vision data not available for cline segments for some nets

- ALLEGRO_EDITOR IN_DESIGN_ANA Impedance check results are incorrect and Crosstalk analysis stops running after updating to HotFix 057

- ALLEGRO_EDITOR NC Improve the User Preference description for BACKDRILL_OVERSIZE_OPTION

- ALLEGRO_EDITOR SCHEM_FTB Netrev.lst is written in the package folder

- ALLEGRO_EDITOR SCHEM_FTB netrev.lst is not created in the correct folder - error displayed for neltist import

- ALLEGRO_EDITOR SHAPE PCB Editor crashes while performing shape operation 'andnot'

- ALLEGRO_EDITOR SHAPE No Void Overlap option is not working in AMB

- ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes for a RAVEL rule

- ALLEGRO_EDITOR SHAPE Allegro PCB Editor crashes on creating dynamic shape

- ALLEGRO_PROD_TOOLB CORE Shield Router - cline end caps treated differently than cline-segment end caps

- ALLEGRO_PROD_TOOLB CORE Productivity Toolbox Z-DRC with multiple net classes: script selects only the last two classes in a group

- CAPTURE SCHEMATICS Slow response when selecting parts in schematic

- CAPTURE SCHEMATICS Slowness in OrCAD Capture when ITC is enabled

- CAPTURE SCHEMATICS Inter-tool communication needs to be disabled to resolve the lag issues in Capture

- RF_PCB ROUTING PCB Editor stops responding on using RF - Add Connect

- SCM OTHER Thevenin Termination dialog displays resistors incorrectly

- SIP_LAYOUT WLP Advanced WLP Non-standard fillets not working properly: fillets not added

Cadence Design Systems announced new capabilities for OrCAD Capture, PSpice Designer and PCB Designer 17.2-2016 that address challenges with flex and rigid-flex design as well as mixed-signal simulation complexities in IoT, wearables and wireless mobile devices. This latest release reduces PCB development time by addressing the need to design reliable circuits for smaller, more compact devices.

This OrCAD portfolio includes new advanced technology enabled for integrated rigid-flex planning, design and real-time visualization, as well as built-in translators that enable direct design imports from select EDA vendors. PSpice Designer now supports system-level simulation using C/C++/SystemC and VerilogA, via the new PSpice compact model interface. This enables hardware/software virtual prototyping so that electrical engineers can design and simulate intelligent IoT devices. OrCAD is the only fully scalable PCB design solution available in the market that seamlessly transitions from mainstream to enterprise PCB solution with the Allegro environment.

To enable a faster and more efficient flex and rigid-flex design creation critical to IoT, wearables and wireless devices, the OrCAD portfolio uses a new multi-stack-up database capability and extensive in-design inter-layer checks, which helps users avoid errors introduced through manual checking. The OrCAD portfolio also features enhancements targeted towards improving PCB editors’ productivity and ease-of-use in padstack editing, constraint management, shape editing and in-design DRCs. To address efficiency needs, the portfolio includes an advanced design differencing engine that enables design review with global teams using state of art visuals. Finally, to give designers more control over their design component annotation process, advanced annotation and auto-referencing capabilities are now available.

Allegro 17.2 release introduces many new capabilities for Flex and Rigid-Flex designs.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

Product: Cadence SPB Allegro and OrCAD (Including EDM)

Version: 17.20.000-2016 HF059 *

Supported Architectures: x64

Website Home Page : www.cadence.com

Language: english

System Requirements: PC **

Supported Operating Systems: **

System Requirements: Cadence SPB Allegro and OrCAD (Including EDM) version 17.20.000-2016 and above

Size: 3.9 Gb

Remove the previous version and install the Cadence License Manager 12.06 and the show-license request file, close it. Then the program with the default settings, install it.

Now LicenseManager folder in the folder Crack in the installation program (by default C: \ Cadence)

copy and file it with the Run as administrator LicenseManagerPubKey.bat on the run. Tools folder in

the path C: \ Cadence \ SPB_17.2 copy and run the file and wait for the operation to be performed ToolsPubKey.bat.

LicenseServerConfiguration.exe file to the path C: \ Cadence \ LicenseManager Run as administrator

to run the License.lic files in the folder, enter the crack and without changing

the Double-click Next and then Finish. A new license in the path C: \ Cadence \ LicenseManager

named license.dat is produced, it will run Notepad with only two lines after the DAEMON

cdslmd (including address and port is cdslmd.exe file) and delete the file save.

Finally lmtools.exe file to run the same route and in the tab Start / Stop / Reread first on Stop Server and then click Start Server or ReRead License File again.

! Installing the update cause failure of fluff and not a result of the program and should be done before installing the following:

To install the program and folder names SPB_17.2 change; for example SPB_17.2

The new folder name and file SPB_17.2 SPB_17.2 compnts.dat in the folder in which to

copy. Now update the default path is the folder SPB_17.2 install.

After the installation, the folder and the folder Crack Crack, tools folder in the folder

SPB_17.2 copy and then run the file ToolsPubKey.bat. After the closure of the

window operation, all the files and folders

in the folder to the folder SPB_17.2 SPB_17.2 move. The folder name in the form

of the previous SPB_17.2 SPB_17.2 back

Note:apply Hotfix before apply patch the files (Use Cadence SPB OrCAD 17.2-2016 Crack Fixed from hotfix folder for crack

Now LicenseManager folder in the folder Crack in the installation program (by default C: \ Cadence)

copy and file it with the Run as administrator LicenseManagerPubKey.bat on the run. Tools folder in

the path C: \ Cadence \ SPB_17.2 copy and run the file and wait for the operation to be performed ToolsPubKey.bat.

LicenseServerConfiguration.exe file to the path C: \ Cadence \ LicenseManager Run as administrator

to run the License.lic files in the folder, enter the crack and without changing

the Double-click Next and then Finish. A new license in the path C: \ Cadence \ LicenseManager

named license.dat is produced, it will run Notepad with only two lines after the DAEMON

cdslmd (including address and port is cdslmd.exe file) and delete the file save.

Finally lmtools.exe file to run the same route and in the tab Start / Stop / Reread first on Stop Server and then click Start Server or ReRead License File again.

! Installing the update cause failure of fluff and not a result of the program and should be done before installing the following:

To install the program and folder names SPB_17.2 change; for example SPB_17.2

The new folder name and file SPB_17.2 SPB_17.2 compnts.dat in the folder in which to

copy. Now update the default path is the folder SPB_17.2 install.

After the installation, the folder and the folder Crack Crack, tools folder in the folder

SPB_17.2 copy and then run the file ToolsPubKey.bat. After the closure of the

window operation, all the files and folders

in the folder to the folder SPB_17.2 SPB_17.2 move. The folder name in the form

of the previous SPB_17.2 SPB_17.2 back

Note:apply Hotfix before apply patch the files (Use Cadence SPB OrCAD 17.2-2016 Crack Fixed from hotfix folder for crack

Cadence Allegro and OrCAD 17.2-2016 Hardware and Software Requirements:

Operating System:

Microsoft Windows 7 Professional, Enterprise, Ultimate or Home Premium (64-bit); Windows 8 (64-bit) (All Service Packs); Windows 10 (64-bit); Windows 2008 R2 Server; Windows 2012 Server (All Service Packs).

Note:Cadence Allegro and OrCAD (Including EDM) products do not support Windows 7 Starter and Home Basic. In addition, Windows Server support does not include support for Windows Remote Desktop. Windows RT and Tablets are not supported.

Minimum Hardware:

- Intel Pentium 4 or AMD Athlon XP 2000 with multi-core CPU

- Ram:8 GB RAM

- Virtual memory at least twice physical memory

- 50 GB free disk space

- 1,024 x 768 display resolution with true color (16-bit color)

- Broadband Internet connection for some service

- Ethernet card (for network communications and security hostID)

- Three-button Microsoft-compatible mouse

Recommended Hardware:

- Intel Core 2 Duo 2.66 GHz or AMD Athlon 64 X2 5200+

- Note: Faster processors are preferred.

- RAM:8 GB RAM

- Disk:500 GB free disk space

- Display:1,280 x 1024 display resolution with true color (at least 32bit color)

- GPU:A dedicated graphics card

- Display:Dual monitors

- Microsoft Internet Explorer 11.0 or later

Operating System:

Microsoft Windows 7 Professional, Enterprise, Ultimate or Home Premium (64-bit); Windows 8 (64-bit) (All Service Packs); Windows 10 (64-bit); Windows 2008 R2 Server; Windows 2012 Server (All Service Packs).

Note:Cadence Allegro and OrCAD (Including EDM) products do not support Windows 7 Starter and Home Basic. In addition, Windows Server support does not include support for Windows Remote Desktop. Windows RT and Tablets are not supported.

Minimum Hardware:

- Intel Pentium 4 or AMD Athlon XP 2000 with multi-core CPU

- Ram:8 GB RAM

- Virtual memory at least twice physical memory

- 50 GB free disk space

- 1,024 x 768 display resolution with true color (16-bit color)

- Broadband Internet connection for some service

- Ethernet card (for network communications and security hostID)

- Three-button Microsoft-compatible mouse

Recommended Hardware:

- Intel Core 2 Duo 2.66 GHz or AMD Athlon 64 X2 5200+

- Note: Faster processors are preferred.

- RAM:8 GB RAM

- Disk:500 GB free disk space

- Display:1,280 x 1024 display resolution with true color (at least 32bit color)

- GPU:A dedicated graphics card

- Display:Dual monitors

- Microsoft Internet Explorer 11.0 or later

Cadence Allegro and OrCAD 17.20.000-2016

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please