Cadence PERSPECAGILE 24.03.001 | 4.1 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has released PERSPEC 24.03.001 is a portable stimulus, system-on-chip (SoC) verification solution.

PERSPEC-14113 | DOCUMENTATION | Document Ternary operator in the Reference Manual

PERSPEC-14108 | CODE_GENERATION | The "typemap" flow crashes when using the Linux integration utility

PERSPEC-14072 | CODE_GENERATION | Accessing token field in runtime during activity causes segfault

PERSPEC-14013 | PS_LIB_COHERENCY | Coherency lib test GenError in CPU based CMN2x1 environment

PERSPEC-13968 | PS_LIB_INTEGRATION | Qualify "block" data transactions with 'is_supporting_copy_block_data()' function

PERSPEC-13883 | SOLVER | Incorrect scheduling of inferred state writer actions with state reader actions when layered solving is required

PERSPEC-13782 | PS_LIB_COHERENCY | Data mismatch error after CACHE_ZERO op codes in fill_shareable_cache_clean_invalidte_check

PERSPEC-13757 | PS_LIB_COHERENCY | Per-cluster post-power-down scheduling fix

PERSPEC-13605 | AUTO_DOC | Perspec 'document' in PDF adds internal constructs that are not seen in HTML option

PERSPEC-13532 | SOLVER | State object inheritance breaks planning solver, thereby, resulting in contradiction

PERSPEC-13505 | PS_LIB_COHERENCY | Code generation fails while solving scenarios with mixed fs_ts_pe scenario for FULL/IO consistency

PERSPEC-13462 | PS_LIB_COHERENCY | TLBI runtime generated without EL context

PERSPEC-13223 | LANGUAGE | Support language part for [ in ref_path ]

PERSPEC-13100 | DOCUMENTATION | Document 'perspec report' and the sln_manager.create_report() API

PERSPEC-13047 | CODE_GENERATION | Issue with union typesize mismatch breaks code execution

PERSPEC-12558 | LANGUAGE | Checking if SLN multi-line string syntax is possible for PSS

PERSPEC-12551 | LANGUAGE | Provide enhancement to avoid cyclic code dependencies

PERSPEC-12547 | SOLVER | forall constraint does not support [ in ref_path ] option syntax

PERSPEC-12285 | SOLVER | Constraining non-rand array with a rand array access attribute is not supported

PERSPEC-12255 | LANGUAGE | Support array/list pseudo methods, such as count

PERSPEC-12024 | PS_LIB_PCIE | Set 'data_chunk_size' to avoid Denali memory allocation error for huge data size

PERSPEC-11886 | DOCUMENTATION, PS_LIB_COHERENCY | Improve documentation for the processor_info configuration table

PERSPEC-11723 | LANGUAGE | Support mustache notation in strings in procedural solve-time code

PERSPEC-10723 | USER_API | Use PCIE-AVIP's reset event (once supported) in our PCIE library tests

PERSPEC-9640 | PS_LIB_COHERENCY | Allow setting of architecture kind and architecture version in Processor Info Table for each core

PERSPEC-8880 | PS_LIB_COHERENCY | Generate address from cacheable range by default for cross_cache_boundaries action

PERSPEC-8195 | PS_LIB_COHERENCY | Enable Producer-Consumer CPU-to-CPU in the Coherency PSLIB

PERSPEC-14108 | CODE_GENERATION | The "typemap" flow crashes when using the Linux integration utility

PERSPEC-14072 | CODE_GENERATION | Accessing token field in runtime during activity causes segfault

PERSPEC-14013 | PS_LIB_COHERENCY | Coherency lib test GenError in CPU based CMN2x1 environment

PERSPEC-13968 | PS_LIB_INTEGRATION | Qualify "block" data transactions with 'is_supporting_copy_block_data()' function

PERSPEC-13883 | SOLVER | Incorrect scheduling of inferred state writer actions with state reader actions when layered solving is required

PERSPEC-13782 | PS_LIB_COHERENCY | Data mismatch error after CACHE_ZERO op codes in fill_shareable_cache_clean_invalidte_check

PERSPEC-13757 | PS_LIB_COHERENCY | Per-cluster post-power-down scheduling fix

PERSPEC-13605 | AUTO_DOC | Perspec 'document' in PDF adds internal constructs that are not seen in HTML option

PERSPEC-13532 | SOLVER | State object inheritance breaks planning solver, thereby, resulting in contradiction

PERSPEC-13505 | PS_LIB_COHERENCY | Code generation fails while solving scenarios with mixed fs_ts_pe scenario for FULL/IO consistency

PERSPEC-13462 | PS_LIB_COHERENCY | TLBI runtime generated without EL context

PERSPEC-13223 | LANGUAGE | Support language part for [ in ref_path ]

PERSPEC-13100 | DOCUMENTATION | Document 'perspec report' and the sln_manager.create_report() API

PERSPEC-13047 | CODE_GENERATION | Issue with union typesize mismatch breaks code execution

PERSPEC-12558 | LANGUAGE | Checking if SLN multi-line string syntax is possible for PSS

PERSPEC-12551 | LANGUAGE | Provide enhancement to avoid cyclic code dependencies

PERSPEC-12547 | SOLVER | forall constraint does not support [ in ref_path ] option syntax

PERSPEC-12285 | SOLVER | Constraining non-rand array with a rand array access attribute is not supported

PERSPEC-12255 | LANGUAGE | Support array/list pseudo methods, such as count

PERSPEC-12024 | PS_LIB_PCIE | Set 'data_chunk_size' to avoid Denali memory allocation error for huge data size

PERSPEC-11886 | DOCUMENTATION, PS_LIB_COHERENCY | Improve documentation for the processor_info configuration table

PERSPEC-11723 | LANGUAGE | Support mustache notation in strings in procedural solve-time code

PERSPEC-10723 | USER_API | Use PCIE-AVIP's reset event (once supported) in our PCIE library tests

PERSPEC-9640 | PS_LIB_COHERENCY | Allow setting of architecture kind and architecture version in Processor Info Table for each core

PERSPEC-8880 | PS_LIB_COHERENCY | Generate address from cacheable range by default for cross_cache_boundaries action

PERSPEC-8195 | PS_LIB_COHERENCY | Enable Producer-Consumer CPU-to-CPU in the Coherency PSLIB

Cadence Perspec System Verifier is a robust tool that automates the generation of test cases. It creates test cases in the C language, which can be used with various testbench environments. The Perspec System Verifier can effectively validate SoC's performance, function, and power by using an appropriate level of abstraction. It is a portable platform that can be reused across different scopes, including hardware-aware software, from IP to the system level. This approach focuses on both vertical and horizontal reuse - vertical reuse covers IP level verification to subsystem to SOC level verification. In contrast, horizontal reuse involves using the test intent across virtual prototype platforms, simulation, emulation, and FPGA. Ultimately, this approach helps to reduce the time and effort spent on creating tests. PSS provides a single abstract specification of verification intent, which allows tools to generate target-specific implementations of the test for the various platforms involved in verification. This frees teams to focus on what should be tested instead of implementing the same test multiple times. PSS can also automate the process by randomly generating scenarios subject to the rules and constraints defined in the abstract specification, maximizing coverage, and ensuring efficient execution of a wide range of tests on multiple platforms.

Cadence Perspec System Verifier SW Driven SoC Verification Automation – Cadence Design Systems

Verification of your mixed-signal design can be a nightmare, with clashing disciplines and engineering cultures, and challenging use-case requirements. In this episode of Chalk Talk, Amelia Dalton chats with Steve Carlson of Cadence Design Systems about a comprehensive approach to mixed-signal system verification.

Cadence is a pivotal leader in electronic design and computational expertise, using its Intelligent System Design strategy to turn design concepts into reality. Cadence customers are the world’s most creative and innovative companies, delivering extraordinary electronic products from chips to boards to systems for the most dynamic market applications.

Owner: Cadence Design Systems Inc.

Product Name: PERSPEC Agile

Version: 24.03.001 Base release

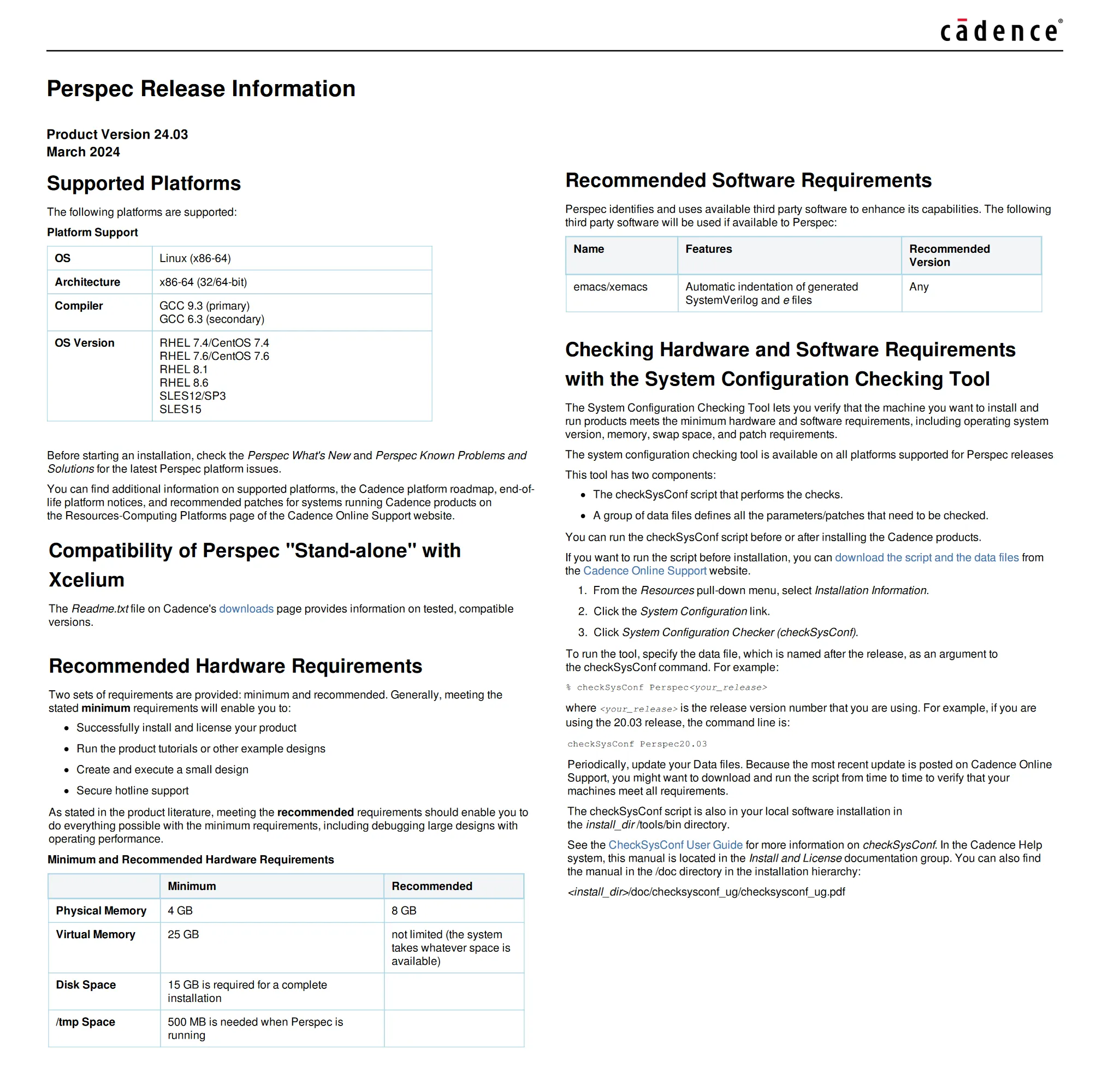

Supported Architectures: x86_64

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: Linux *

Size: 4.1 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please