Cadence JasperGold 23.03.001 | 3.5 Gb

Cadence has released JasperGold 23.03.01 is the first verification product to deliver complete "deep formal" systematic verification, ensuring correctness where it matters most.

Jasper Apps Version 2023.03

The release of Jasper Apps version 2023.03 includes several new features and enhancements in the areas listed below.

*****************************IMPORTANT NOTICE***************************

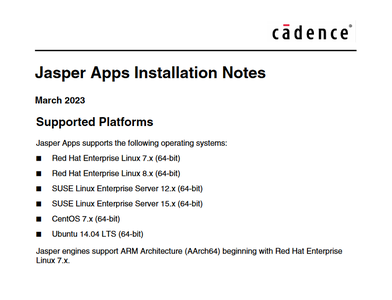

UPCOMING CHANGE IN PLATFORM SUPPORT: Beginning with version 2023.06, Jasper will no longer support Red Hat Enterprise Linux 7.1, 7.2, or 7.3 or CentOS 7.1, 7.2, or 7.3.

IMPORTANT INFORMATION ON KERNEL SUPPORT: Currently, a bug in kernel versions 4.18.0-358.el8_6 through 4.18.0-372.19.el8_6, which are present in Red Hat Enterprise Linux 8.x operating systems, prevents you from running Jasper Apps. You must upgrade the kernel version to run Jasper. For additional information about this issue, consult the QTBUG-100174 bug report.

JAVA RETIREMENT: Beginning with the 2023.03 FCS release, Jasper will not load a Java Virtual Machine or provide the Java Runtime Environment with the build. One known side effect is that the “hs_err_pid<PID>.log” files will no longer be created if Jasper exits unexpectedly.

*************************************************************************

List of Features and Enhancements

––––––––––––––––-

* C to RTL Equivalence Checking (C2RTL) App

* C/C++ Call Stack Now Visible by Default in C2RTL Source Browser

* C Structs Now Accepted as Inputs for C2RTL

* Improved Messaging for Synthesis Errors

* JASPER_ASSUME Now Works as Expected for .c Files

* Automatically Constraining Enum Type Inputs

* C/C++ Compilation Warnings Now Printed to Console

* Warning Now Issued for Termination Due to Insufficient Unwind Limit

* InsufficientUnwindLimit Safety Assertion Renamed to InsufficientUnrollLimit

* Multi-Context Debugging

* Clock Domain Crossing (CDC) App

* Creating a Clock Definition

* Deprecated RPT_NO_STBL, WPT_NO_STBL, RPT_OP_GRAY, and WPT_OP_GRAY Violations

* CDC Now Automatically Detects Multi-Bit Schemes

* Editing SDC Files from the Source Line in the Signal Info Pane

* "check_cdc -init" Now Mandatory for CDC Flow

* New Violation Message Field in Violation Info Table

* Rating Multiple Ports Simultaneously from the GUI

* Violation Table Updates with New Switches and Associated Deprecations

* Renamed Tables in Schematic Viewer

* Violation Info Table Now Shows Disabled Synchronizers

* New RDC Check for Sync Reset Connected Asynchronously (RDC_RS_SYCA)

* Enhanced CDC Detection of Edge and MUX Synchronizers

* Updated Violation Info Details for RDC_RS_DFRS Violations

* Changes to RDC_RS_DFRS Detection

* New Show Parameters Dialog

* Connectivity Verification App

* "save" and "restore" Now Work with Connectivity

* Enhanced Width Mismatch Warning WCON001

* Updated Connectivity Examples in Doc Directory

* Coverage App

* COV Now Supports ProofMaster

* Viewing Details of Unknown/Unprocessed Properties After Measure

* Setting Artificial Bounds for Bound Analysis Independent of FPV

* Coverage Now Shows Proof Structure Nodes in Task Dialog

* Reusing Proof Results in Coverage App

* Coverage Unreachability (UNR) App

* Added "-covscope" and "-covworkdir" Switches to "check_unr -init"

* UNR Now Supports ProofMaster

* Low Power Verification (LPV) App

* UPF "-is_analog" Attribute Now Supported

* LPV Now Supports "query_supply_port"

* Security Path Verification (SPV) App

* Creating Precondition Covers for SPV Cover Properties

* Visualize Now Enabled for SPV and X-Prop Properties with No Trace

* SPV Now Supports "visualize -replot"

* Disabled Warnings WSPV025, WSPV026, and WSPV027

* SPV GUI Now Supports Multiple Properties for Proof Strategy

* Differentiating Between COI Analysis and Pre-Processing

* Enhanced "check_spv -list -properties"

* Enhanced SPV Initialization

* "check_spv -prove -property" Now Supports Regular Expressions

* "check_spv -create" Now Supports Wildcards

* Instances and Wildcards as Arguments to "-through" and "-not_through"

* "check_spv -create" Now Supports Wildcards

* Sequential Equivalence Checking (SEC) App

* SEC Now Supports Restoring Elaborated Designs

* Restoring an Elaborated Design to SEC Spec, Imp, or Both

* Parent Assertion Now Marked Proven if Any Related Cover is Unreachable

* Superlint App

* New Superlint Rules Files

* Enhanced CND_NR_COMM

* New Superlint Checks

* Reporting Missing Case Items for CAS_NR_DEFN Violations

* IDN_NR_ALCA Now Skips Function Ports by Default

* X-Propagation (XPROP) Verification App

* X-Prop Now Synthesizes $isunknown Properties by Default

* Prove Options in X-Prop Context Menus Now Issue "check_xprop -prove"

* X-Prop Re-Architecture

* X-Prop Does Not Support Trace Extension

* Visualize

* Plotting All Bits of Enum on Why Result

* Improve Messaging for QuietTrace

* Improved Messaging for Debugging Cell Defines

* Clocks and Reset

* Enhanced Messaging for Formal Reset Sequence

* Combinational loop

* Enhanced Glitch Debugging

* Deep Bug Hunting

* Additional Engine Support for Cycle and Bound Swarm Modes

* Design Compilation

* Related Assertions for Safety Component in Liveness

* Spurious VERI-1208 Warnings No Longer Issued for Unsized Literals

* Design Exploration

* Enhanced "-list interface*" Options for Instance and Module Scopes

* Now Showing Inline Annotation for Outermost Instead of Slicing Signal

* Visualize Now Automatically Shows the Why Result for All Traces

* Macros Automatically Expanded in Superlint Violations

* Design Exploration and Verification Management

* Enhanced Options for "get_property_info -list"

* Language Support

* Previewing Witness Properties

* Jasper Now Evaluates the Condition Expression to 1'bx

* Miscellaneous

* Updated Jasper Functional Safety Verification (FSV) App User Guide

* Proof Structure Hard Case Split

* "cte.log" Path on ISCD001 Now a Link

* Enhanced SDC Reporting

* Proofs and ProofGrid

* You Can Now Run Formal Profiler on Multiple Properties in Parallel

* Jasper Now Saves and Restores Proof Structure Operations

* Bound Aggregation in ProofGrid

* User Interface

* Traces Column of the FPV Property Table Now Beside Bound Column

* Verification Management

* "get_needed_assumptions" Now Reports Property Name

* Compressing Databases During "save"

* New "related_property_type" Attribute for "get_property_list"

* vManager Integration

* Elaborated Design Now Used to Save and Open Traces

* SPV Assertions Now Supported in vManager

New Features and Enhancements

=============================

This section provides details about the new features and enhancements listed

above. Refer to the Jasper Apps manuals and incremental training slides

(Tech Updates) for additional information.

C to RTL Equivalence Checking (C2RTL) App

––––––––––––––––––––-

* C Structs Now Accepted as Inputs for C2RTL

The C2RTL flow now supports structs as interfaces of the formal model.

Given a struct expression "expr", you can declare x as either an input or

output of the formal model using the existing macros JASPER_INPUT_LVAL and

JASPER_OUTPUT_RVAL. For example:

JASPER_INPUT_LVAL(expr, myname);

JASPER_OUTPUT_RVAL(expr , myname)

If "expr" is a variable and also the desired name of the interface signal

in the formal model, you can write the following:

JASPER_INPUT(expr);

JASPER_OUTPUT(expr);

* C/C++ Call Stack Now Visible by Default in C2RTL Source Browser

Jasper C2RTL now shows the C/C++ function call stack tree in the Spec

and Imp design source browser.

* C/C++ Compilation Warnings Now Printed to Console

C/C++ compilation warnings are now printed in the Jasper console along

with errors.

* Automatically Constraining Enum Type Inputs

The release includes a new switch "-create_valid_enum_value_input_constraints"

for the "check_c2rtl -compile" command. With this command, for each enum

variable declared using JASPER_INPUT(SIGNAL_NAME), the tool generates an

assumption for which the input can be only one of the declared enum values.

The assumption name is in the form

"<constraints>/_type_constraint_SIGNAL_NAME".

An additional new command "check_c2rtl -set_dynamic_pruning

-use_valid_enum_value_input_constraints", when set to "true", ensures

dynamic path pruning considers only the valid enum values for inputs declared

using JASPER_INPUT, while pruning the C++ model. Thus, when this configuration

is "true", you cannot disable the assumptions described above.

* Warning Now Issued for Termination Due to Insufficient Unwind Limit

If formal model generation finds a deterministic loop for which the unrolling

bound is too low, it issues a warning that the formal model is probably

incomplete.

* JASPER_ASSUME Now Works as Expected for .c Files

You can now use JASPER_ASSUME and JASPER_ASSERT on .c files in addition

to .cpp files.

* Multi-Context Debugging

Prior to this release, C2RTL supported a single debugging context only in

Visualize. However, debugging through C++ and RTL models is usually done at

different cycles. With this release, C2RTL now supports multi-context

debugging in Visualize by default. After a Why, Driver, or Load operation,

Visualize automatically creates two independent markers for the spec and imp

contexts and updates these for every subsequent debugging operation.

* InsufficientUnwindLimit Safety Assertion Renamed to InsufficientUnrollLimit

With the 2022.12 FCS release, unwind switches were renamed to unroll. This

release changes the name of the "InsufficientUnwindLimit" property to

"InsufficientUnrollLimit".

* Improved Messaging for Synthesis Errors

ECTR057 has been deprecated and replaced with ECTR034:

ECTR034: Synthesis errors that might indicate a tool bug have been found.

Contact support@cadence.com.

Clock Domain Crossing (CDC) App

–––––––––––––––-

* Deprecated RPT_NO_STBL, WPT_NO_STBL, RPT_OP_GRAY, and WPT_OP_GRAY Violations

CDC no longer reports RPT_NO_STBL, WPT_NO_STBL, RPT_OP_GRAY, or WPT_OP_GRAY

violations.

* Creating a Clock Definition

You can now use the following command to create a CDC clock definition

that drives the specified signals:

config_rtlds -clock -create {target_signal_list}

[-name clock_name] [-factor N] [-add]

NOTE:

. Clocks defined with this command are available for formal use only

after running the CDC command "check_cdc -clock_domain -find".

. See the full help for additional details (help config_rtlds -gui).

* Renamed Tables in Schematic Viewer

The "CDC Violation Info" and "CDC Signal Info" tables in the CDC Schematic

Viewer GUI were renamed to "Violation Info" and "Signal Info", respectively.

* CDC Now Automatically Detects Multi-Bit Schemes

CDC now automatically detects multi-bit schemes of type Pulse and Edge.

* Enhanced CDC Detection of Edge and MUX Synchronizers

CDC now automatically detects MUX_NDFF schemes that are controlled by a

single bit of an NDFF_BUS scheme. It also detects MUX_PULSE schemes that are

controlled by a single-bit Edge scheme or by a bit of a multi-bit Edge or

Pulse scheme.

* "check_cdc -init" Now Mandatory for CDC Flow

The "check_cdc" command now issues an error if "check_cdc -init" has not yet

been issued. Also, all "config_rtlds" commands require that CDC or Superlint

has already been initialized.

NOTE:

. CDC can be initialized only if "check_superlint -init" has not already

been issued.

. The "check_cdc -init" or "check_superlint -init" commands are automatically

issued if you launch Jasper with the "-cdc" or "-superlint" command-line

switches.

* Rating Multiple Ports Simultaneously from the GUI

You can now simultaneously select multiple rows of the CDC Port

Configuration table (Ctrl or Shift + Click), and then right-click the

selection to open the "Set signal clock" dialog and set the clock for the

selected ports. Also with this change, the "Set signal clock" dialog is now

wider and shows all the selected ports in the "Signal Name(s)" field.

* Violation Info Table Now Shows Disabled Synchronizers

A new "Disabled Auto Detection" row was added to the "Violation Info" table

in the CDC Schematic Viewer GUI for no_scheme (CDC_NO_SYNC) violations. This

new field contains a list of all the CDC synchronizer types for which

automatic detection is disabled (either by default or by the user).

* New Violation Message Field in Violation Info Table

The "Violation Info" table of the CDC Schematic Viewer now includes a new

"Violation Message" field. This new field contains the same violation message

that is currently displayed in the "Review Violations" pane of the CDC main

window.

* Editing SDC Files from the Source Line in the Signal Info Pane

The file name and line number in the Clock Source Location row of the

Schematic Viewer's Signal Info pane is now a hyperlink. Clicking on this

link opens the file in an editor pointing to the line number.

* Violation Table Updates with New Switches and Associated Deprecations

The following CDC violation fields were renamed as follows in the GUI, in

the output of the "check_cdc -list" command, and in the reports generated

with "check_cdc -report":

. Source Reset -> Local Source Reset

. Destination Reset -> Local Destination Reset

. Reset Sources -> Reset Domain

. Source Declared Resets -> Source Reset Domain

. Destination Declared Resets -> Destination Reset Domain

. Source Domain -> Source Clock Domain

. Destination Domain -> Destination Clock Domain

The corresponding switches in the "check_cdc -filter -add" command were also

renamed. See the full help for additional details (help check_cdc -gui).

NOTE: The old switches have been deprecated but are maintained for

backward compatibility. These will be removed in a future release.

* Updated Violation Info Details for RDC_RS_DFRS Violations

Now, the "Reset Sources" field is replaced with "Source Unit" for RDC_RS_DFRS

violations.

* Changes to RDC_RS_DFRS Detection

RDC_RS_DFRS pair detection now takes reset rating of top ports, blackbox

ports, and flops into consideration. It also uses the information available

in the hierarchical database if the above information is not available. This

violation now detects RDC pairs whose connection passes through one or more

hierarchical blackbox internal combinational connections.

The RDC_RS_DFRS violation now compares source and destination root resets

instead of reset sources. Different reset polarity between the source and the

destination of the RDC pair is no longer a sufficient condition to lead to a

different RDC_RS_RFRS violation. Also, as before, RDC pairs with destination

units with no reset conditions are ignored if "ignore_non_resettable_flop" is

"true".

Assuming "ignore_rdc_from_same_reset_source" is "true", an RDC pair does not

lead to a different reset violation when each synchronized or async reset in

the source side of the pair has at least one equivalent synchronized or async

reset in the destination side that ensures that, whenever the source flop is

in reset state, the destination side is also in reset state.

Assuming "ignore_rdc_from_same_reset_source" is "false", an RDC pair does not

lead to a different reset violation when there is a path between the

asynchronous reset pin of the source flop and the asynchronous reset pin of

the destination flop, and this path is composed of buffers and wires only.

Thus, the signals reaching the asynchronous reset pins are either equal or

inverse.

* New RDC Check for Sync Reset Connected Asynchronously (RDC_RS_SYCA)

CDC reports the new RDC_RS_SYCA RDC violation for RDC pairs where the source

unit has at least one fully sync reset connected asynchronously, which is not

connected asynchronously to the destination unit. The referred fully sync

resets can be declared using the "config_rtlds -reset -sync" command, be

synchronized by a direct reset scheme, or be a data signal that is synchronous

to the RDC pair.

The reference resets used for comparisons are as follows:

. Flop units: The signals connected to the asynchronous reset condition pins.

. Port units: The "config_rtlds" reset ratings.

. Unrated blackbox ports: The reset sequential abstract arcs from the

hierarchical flow, if available.

* New Show Parameters Dialog

This release adds a new "Show Parameters" option to the Preview Violations

context menu (right-click). When you choose this option, the tool opens a

dialog showing the list of parameters and their values that influence the

selected domain or tag.

NOTE: Some of the domain-level parameters might not affect all tags under

that domain.

Connectivity Verification App

––––––––––––––-

* "save" and "restore" Now Work with Connectivity

You can now save and restore loaded connection maps, COI check information,

toggle check results, and proof status with the Jasper "save" and "restore"

commands. The flow is as follows:

// In the current session, issue the following command:

% save -jdb my_session.jdb -capture_setup -capture_session_data

// Close the session and start a new session:

% jg -conn

// Restore the saved session:

% restore -jdb my_session.jdb

NOTE: See Appendix B in the Connectivity App user guide for additional

information.

* Updated Connectivity Examples in Doc Directory

The Connectivity examples in the doc directory have been updated to use

"clock -none" and "reset -none".

* Enhanced Width Mismatch Warning WCON001

Warning WCON001 has been enhanced to include the width of each signal and to

specify the signal used in the analysis. The message now reads as follows:

WCON001: Size mismatch in signals "%s" and "%s" from connection "%s".

Source width is %d, but destination width is %d. Width %d will be

considered for analysis."

Coverage App

––––––

* COV Now Supports ProofMaster

"check_cov -measure" now supports ProofMaster.

NOTE: The COV App does not support proof cache when running checker coverage.

* Viewing Details of Unknown/Unprocessed Properties After Measure

Now, when running bound analysis, you can click on unknown/unprocessed

results to view the bounded coverage details in the Assert Analysis tab.

Previously, the tool did not permit this action.

* Setting Artificial Bounds for Bound Analysis Independent of FPV

You can now use the following command to artificially set a bound to

an assertion and then run "check_cov -measure -type {bound}" to analyze the

results from the Assert Analysis tab:

check_cov -assert_analysis -assert <name> (-set_bound <value> |-clear_bound)

Also with this change, the Coverage Assert Analysis "Assert Bound" column

indicates when a bound is "(Artificial)".

NOTE:

. This artificial bound does not alter proof results. If you subsequently run

a "prove", the tool overwrites the artificial bounds you had previously set.

. This command does not work for proven assertions or counterexamples.

. One command must be issued per assertion.

* Reusing Proof Results in Coverage App

Previously, attempting to restore FPV proof results with "restore -jdb"

cleared the Coverage database. Now, the restoration works as expected, so you

can reuse FPV proof results for both Coverage proof and assertion analysis.

* Coverage Now Shows Proof Structure Nodes in Task Dialog

Warning WCOV103 is now issued if you use a Proof Structure node as a task in

"check_cov -measure -task". These nodes are handled as any other task and

merged results are not guaranteed to be safe and sound.

Coverage Unreachability (UNR) App

––––––––––––––––-

* Added "-covscope" and "-covworkdir" Switches to "check_unr -init"

With this release, you can use the following switches with "check_unr -init":

. -covscope: Specifies the scope directory name for the UNR database.

. -covworkdir: Specifies the working directory name for the UNR database.

* UNR Now Supports ProofMaster

"check_unr -prove" now supports ProofMaster. Use "set_proofmaster on" to

enable ProofMaster for UNR.

Low Power Verification (LPV) App

––––––––––––––––

* UPF "-is_analog" Attribute Now Supported

The UPF command "set_port_attributes" now supports the "-is_analog" switch

in UPF3.1 and the "is_analog (true | false)" attribute in UPF2.1.

* LPV Now Supports "query_supply_port"

LPV now supports the "query_suppy_port" UPF command. This command

lists created supply ports or shows information about specific

supply ports.

Security Path Verification (SPV) App

––––––––––––––––––

* Enhanced "check_spv -list -properties"

"check_spv -list -properties" now displays the following additional

details:

. no precondition covers

. include/exclude control paths

. driving logic

. feedback loops

. precise rating

* Differentiating Between COI Analysis and Pre-Processing

SPV properties that are proven structurally because the "from" signals are not

in the COI of the "to" signals will now show "COI" in the Strategy column and

"PRE in the Engine column in the GUI. Previously, these proofs showed an empty

Strategy column and "PRE" for the Engine, making them indistinguishable from

properties proven during later engine pre-processing.

* Enhanced SPV Initialization

All disabled properties are now hidden from the SPV Property table on

initialization.

* Disabled Warnings WSPV025, WSPV026, and WSPV027

Warnings WSPV025, WSPV026, and WSPV027, which are relevant only when

transitioning from the old SPV flow, are no longer printed by default.

* SPV Now Supports "visualize -replot"

You can now use "visualize -replot" on windows that were generated by SPV.

* Creating Precondition Covers for SPV Cover Properties

You can now create related precondition covers for SPV cover properties as

well as SPV assertions. These include from precondition, to precondition, and

combined precondition properties.

* Visualize Now Enabled for SPV and X-Prop Properties with No Trace

As with FPV, Visualize now runs a proof on the property and shows the found

trace or informs you that no trace exists.

* "check_spv -create" Now Supports Wildcards

The "-from" and "-to" switches of the "check_spv -create" command now support

wildcards.

* "check_spv -prove -property" Now Supports Regular Expressions

"check_spv -prove -property" now supports regular expressions with the

"-regexp" switch. Previously, only wildcards were supported.

* SPV GUI Now Supports Multiple Properties for Proof Strategy

You can now use the SPV Viewer Properties Table context-menu option "Prove

Property Proof Strategy" to prove any number of provable properties. This

option issues the "check_spv -prove -property <property_name_tcl_list>

-strategy -proof" command, which might fail if the properties do not have

the same signature or propagation environment.

* Instances and Wildcards as Arguments to "-through" and "-not_through"

You can now pass instances and wildcards as arguments to "check_spv

-create… -through" and "check_spv -create… -not_through".

* "check_spv -create" Now Supports Wildcards

The "-from" and "-to" switches of the "check_spv -create" command now support

wildcards.

Sequential Equivalence Checking (SEC) App

––––––––––––––––––––-

* SEC Now Supports Restoring Elaborated Designs

You can now restore a design elaborated with SEC and saved with the "save

-elaborated_design" command before issuing "check_sec -setup". Previously,

this required that you have a .jdb file.

* Parent Assertion Now Marked Proven if Any Related Cover is Unreachable

SEC properties are now marked proven if any of their related covers are

unreachable.

* Restoring an Elaborated Design to SEC Spec, Imp, or Both

This capability applies to designs that have been elaborated with any of the

following SEC commands:

. "check_sec -elaborate"

. "elaborate" after running "check_sec -compile_context (spec | imp | both)"

. "check_sec -setup -elaborate_opts …" (joint setup)

. "elaborate" after running "set_sec_elaborate_mode on"

NOTE: The new "set_sec_elaborate_mode on" command specifies that an

elaboration include configuration and modeling specific to SEC.

To restore the elaborated design for a specified side, first run "check_sec

-compile_context (spec | imp | both)". Then run "restore -elaborated_design

<dir_or_file>", which restores the design to the specified side.

NOTE If the directory contains more than one file, you must provide the path

of the file instead of the directory.

* New Configuration Command Enables SEC Elaboration Mode

You can now use the following configuration command to specify that

an elaboration include configuration and modeling specific to SEC:

set_sec_elaborate_mode (on | off)

. on: Run "elaborate" with SEC configurations and modeling. The elaborated

design is identical to that generated by "check_sec -elaborate".

. off: Do not run "elaborate" with SEC configurations and modeling. This is

the default.

Superlint App

––––––-

* New Superlint Rules Files

This release includes four new Superlint rules files as follows:

. superlint_core.def: Reduced set of LINT/DFT checks for initial deployment.

NOTE:

. Use "include superlint_core" to include the new core rules file in a

custom rules file.

. Beginning with this release, the following command in any Tcl scripts

will execute fewer checks: config_rtlds -rule -enable -domain {LINT DFT}

. superlint_D0254.def: Checks RTL for compliance with D0254 coding guidelines.

NOTE: Compliance with DO254 ruleset does not ensure certification.

. superlint_VHDL.def: Applicable to VHDL only.

. superlint_Verilog_SystemVerilog.def: Applicable to Verilog and SystemVerilog

only.

All new rules files are a subset of the rules available in "superlint.def",

which remains the default, and all can be found at the following location:

<install>/etc/res/rtlds/rules/.

* IDN_NR_ALCA Now Skips Function Ports by Default

The following parameter is added to IDN_NR_ALCA, which now avoids violations

on function ports by default:

params IDN_NF_ALCA {skip_function_ports=yes}

Set this parameter to "no" if you prefer Superlint report this violation on

function ports as well.

* Enhanced CND_NR_COMM

CND_NR_COMM now checks expression for logical AND operator only.

* Reporting Missing Case Items for CAS_NR_DEFN Violations

You can now set the following new parameter to report the missing items in

CAS_NR_DEFN violations:

params CAS_NR_DEFN {verbose_report_all_missing_case_items="yes"|"no"}

To report missing items, set this parameter to "yes". "no" if the default.

* New Superlint Checks

This release includes the following new checks:

. CODINGSTYLE

. INS_NR_DRCT (Warning): "In design-unit '%s', instantiation '%s' of the

VHDL entity '%s' is done directly without component declaration"

. MOD_NR_DSSL (Warning): "Design-unit '%s' contains declaration and

statement '%s' in a single line"

. STRUCTURAL

. SIG_IS_INIT (Error): "%s '%s' in the design unit '%s' is not initialized

to a uniquely determined value"

X-Propagation (XPROP) Verification App

–––––––––––––––––––

* Prove Options in X-Prop Context Menus Now Issue "check_xprop -prove"

The "Prove Property" and "Prove Task" context-menu options of the X-Prop task

task and property tables now issue a "check_xprop -prove" command instead of

the platform "prove" command.

* X-Prop Now Synthesizes $isunknown Properties by Default

The X-Prop App now always synthesizes $isunknown properties.

* X-Prop Re-Architecture

***IMPORTANT: CHANGE IN TOOL BEHAVIOR***

Beginning with this release, the X-Prop App must be initialized with

the new "check_xprop -init" command. You must call this command before

any other X-Prop-related command and before the "analyze" and

"elaborate" commands.

NOTE: When you launch Jasper with the "-xprop" command-line switch, the

X-Prop App is automatically initialized with "check_xprop -init" command.

Also with this change, you can now use a "basic" or "proof" strategy to prove

X-Prop properties:

. check-xprop -prove -strategy basic: Run the proof in a single-threaded

proof environment. This is the default.

. check_xprop -prove -strategy proof: Run the proof in a sophisticated,

multi-threaded, and collaborating proof environment.

See the X-Prop Tech Update slides for additional information about associated

command changes and limitations.

* X-Prop Does Not Support Trace Extension

X-Prop does not support trace extension. If you attempt a proof run with

a "trace_extension" value other that 0, the tool issues an error and asks you

to set "trace_extension" to 0.

Visualize

––––-

* Plotting All Bits of Enum on Why Result

Added new option "Plot all bits of Why result" in "Preferences - Visualize -

Plot", which can be set using the GUI or the "set_preference

{Visualize/PlotAllBitsOfWhyResult} true" command.

If this option is true, Visualize plots all bits of "Why" results signals to

the primary waveform when you choose the "Adding Why Signals" context menu

option or to the "Preview Why Results" waveform when performing the "Why"

operations in the Source Browser and in the primary waveform.

* Improve Messaging for QuietTrace

QuietTrace now issues a more informative message when it stops mid job:

EVS177: QuietTrace stopped with {remaining} remaining soft constraints.

Satisfied: {satisfied}. Not Satisfied: {failed}.

Proof has timed out, exceeded memory limit, or found another issue.

* Improved Messaging for Debugging Cell Defines

The tool now issues the following warning when the trace driver is on a

boundary with a cell define and visibility is "off":

WNL089: The driver trace will not go into cell defines. If you need to debug

cell defines, use "set_cell_define_debug_visibility on".

Clocks and Reset

––––––––

* Enhanced Messaging for Formal Reset Sequence

Formal reset sequence now issues the error below when you use an incorrect

bound:

ERS065: The argument to "start_formal_bound" must be an integer between 0

and the sequence's total number of cycles.

Combinational loop

–––––––––

* Enhanced Glitch Debugging

If there is a :noGlitch counterexample detected by "check_loop -formal glitch",

the "check_loop -formal -show_schematic" command displays the ":noGlitch Loop

Viewer", which is a special Schematic Viewer that displays customized colors

and annotations as follows to help with glitch debugging:

. white : Glitch gate source and the flop that contains a glitch

. red : Glitch propagation path

. green : Asynchronous variables impacted by the glitch

. symbol: High/low glitch and late posedge/negedge

Deep Bug Hunting

––––––––

* Additional Engine Support for Cycle and Bound Swarm Modes

Now, the "hunt -config -strategy" command "bound_swarm" and "cycle_swarm"

modes support engines Ht and Hts.

Design Compilation

–––––––––

* Spurious VERI-1208 Warnings No Longer Issued for Unsized Literals

Unsized decimal-based numbers larger than 64-bits (for example,

'd34359738368) are no longer truncated to 32 bits.

* Related Assertions for Safety Component in Liveness

By default, the tool now automatically creates related assertions on mixed

liveness properties. These related assertions are the pure safety part of the

mixed liveness. The related assertions behave as related covers, and an

exclamation mark in added to the main property if a CEX is found.

Design Exploration

–––––––––

* Enhanced "-list interface*" Options for Instance and Module Scopes

The "-list interface", "-list interface_instance", "-list interface_port", and

"-list interface_no_param" options of the "get_design_info -instance" and

"get_design_info -module" commands no longer return information transitively.

By default, these commands now return information for the queried hierarchy

level only.

NOTE: With this change, these commands now include an optional

"-transitive" switch for backward compatibility.

* Now Showing Inline Annotation for Outermost Instead of Slicing Signal

In the Visualize Source Browser, array slices are now annotated inline with

the value of the outermost signal instead of the slicing signal.

* Visualize Now Automatically Shows the Why Result for All Traces

Visualize now automatically shows the Why result when opening any type of

trace, including cover and liveness targets. Thus, the Visualize Plot

Preferences option "Show the Why result automatically when opening a CEX

trace" has been modified to read "Show the Why result automatically when

opening a trace".

NOTE: The Preference key "Visualize/ShowWhyOnCEXAutomatically" was not

changed.

* Macros Automatically Expanded in Superlint Violations

Now, when you click on a violation in the Superlint "Automatic Formal

Properties" table and the source location of the violation is inside

a macro, the macro is automatically expanded, and the star icon is

moved to the violation line inside the expansion.

Design Exploration and Verification Management

–––––––––––––––––––––––

* Enhanced Options for "get_property_info -list"

You can now use the following new options with "get_property_info -list":

. related_asserts: Lists any related assertions for the specified property.

. is_related_cover: Returns "1" if the property is a related cover;

otherwise, returns "0".

. is_related_assert: Returns "1" if the property is a related assertion;

otherwise, returns "0".

. related_property_type: Identifies the type of the related property:

. none

. precondition

. contrapositive

. witness

. precondition_infinite

. precondition_late

. infinite_contrapositive

. safety_in_liveness_assert

NOTE: The "precondition" attribute will be deprecated in a future release.

Language Support

––––––––

* Previewing Witness Properties

The property detail pane now shows the expression of witness properties by

default. If the tool is unable to regenerate the expression, it continues

to show the line-file of the main property in the property detail pane.

* Jasper Now Evaluates the Condition Expression to 1'bx

Now, Jasper respects the SystemVerilog LRM when dealing with constant Xs in

the condition for single-bit logic AND/OR evaluation. According to the LRM,

the condition expression should be evaluated to 1'bx.

* Improved Actual versus Formal Type Checks

Jasper has improved the checks for actual versus formal type during module

and interface instantiation. Due to this improvement, new VERI-1370 errors

might be issued if there is a type mismatch between formal and actual.

Miscellaneous

––––––-

* Updated Jasper Functional Safety Verification (FSV) App User Guide

You can now consult the new section about saving and restoring FSV designs and

session data in the Jasper FSV App User Guide.

* Proof Structure Hard Case Split

Previously, the Proof Structure case split operation worked by adding

preconditions, but sometimes, the complexity is much better if you add

assumptions instead. With this release, the new hard case split operation is

introduced. This operation implements the case split using assumptions instead

of preconditions, and adds a "-validity" switch, which checks that the proof

is safe to propagate. If the validity node fails, local proofs do not

propagate upward. However, individual case nodes can always propagate a

counterexample or cover.

NOTE: See the full help for additional details (help proof_structure -gui).

* "cte.log" Path on ISCD001 Now a Link

ISCD001 now includes a hyperlink to the "cte.log" file. Clicking on the

hyperlink opens the "cte.log" in a text editor.

* Enhanced SDC Reporting

Now, unsupported SDC commands are reported under a new "Ignored" category

in the command execution summary report, and the tool issues warning WSDC008.

Also with this release, the SDC command execution log (cte.log) is a link in

the message that can be opened directly from the console.

Proofs and ProofGrid

––––––––––

* You Can Now Run Formal Profiler on Multiple Properties in Parallel

Formal Profiler now supports multiple parallel runs. Run the

"formal_profiler -property" command repeatedly to trigger each new run.

The new "-stop" switch now optionally accepts a run name as argument,

but if no name is provided, this command stops the last run by default.

With this change, the Formal Profiler GUI now has a dropdown menu that

enables choosing from all available runs, that is, the current, ongoing

runs as well as past, completed runs.

* Jasper Now Saves and Restores Proof Structure Operations

The command "save -jdb database -capture_session_data" now captures

the data from all Proof Structure operations. The Proof Structure

tree is restored between sessions with the command "restore -jdb database".

LIMITATION: Saving and restoring Proof Structure is not supported with C2RTL.

* Bound Aggregation in ProofGrid

Each property has a "min_length" attribute, measured in cycles, that indicates

the earliest cycle where a trace might exist (for example, bounded proof depth

= min_length-1). When running hunt "cycle_swarm" or "bound_swarm" modes, or

proofs that use engines with elastic BMC configurations, individual cycles can

become fully analyzed. "min_length" calculations now automatically account

for contributions made by elastic BMC-based engines running in the same proof

thread.

User Interface

–––––––

* Traces Column of the FPV Property Table Now Beside Bound Column

The "Traces" column of the FPV Property Table is now located to the right of

the "Bound" column to improve its visibility.

Verification Management

–––––––––––-

* "get_needed_assumptions" Now Reports Property Name

Now, the "get_needed_assumptions" summary result prints the property on which

the analysis is performed.

Also with this release, you will see changes to the indentation of the

summary results.

* Compressing Databases During "save"

You can now use the new "set_save_compress_database" configuration to specify

whether a session must automatically run Gzip to compress the generated files

when saving databases. The syntax follows:

set_save_compress_database (on | off)

. on: Use Gzip to compress the databases.

. off: Does not use Gzip to compress databases. This is the default.

NOTE:

. This command is supported by "save -elaborated_design" and "save -jdb"

only, and does not affect "save -dir" or "save -script".

. Gzip cannot reduce file size when compressing a file that is encrypted

or has already been compressed.

* New "related_property_type" Attribute for "get_property_list"

***IMPORTANT: CHANGE IN TOOL BEHAVIOR***

This release adds the new attribute {related_property_type <type_list>} to the

"get_property_list (–include |-exclude)" command. This includes or excludes

the specified related property types:

. none

. precondition

. contrapositive

. witness

. precondition_infinite

. infinite_contrapositive

. safety_in_liveness_assert

. precondition_late

Also with this release, the new Boolean attributes "is_related_assert",

and "is_related_cover" return a list of all related assertions (safety_

in_liveness_assert), and all related covers, respectively.

vManager Integration

––––––––––

* SPV Assertions Now Supported in vManager

SPV assertions and covers are now exported for vManager signoff when you use

the following command-line options:

jg run.tcl -cov_init "-coverage u -covoverwrite [-task spv] -write_metrics -witness_resolution any_unr"

* Elaborated Design Now Used to Save and Open Traces

Previously, saving and opening traces from Jasper runs on Verisium Manager

required rerunning all steps, including "analyze" and "elaborate", for each

trace. Now, Jasper-Verisium Manager integration uses the elaborated design

instead. Each test saves one elaborated design database; thus, waveforms

reopen faster.

Resolved Issues

===============

The following reported issues have been fixed in 2023.03.

Clock Domain Crossing (CDC) App

–––––––––––––––-

* CDC Phases Pairs Table Filtering Again Working as Expected

You are once again able to see only the pairs associated with a selected CDC

crossing from the CDC Phases Pairs table. This functionality stopped working

with the 2022.12 release, but this release resolves the issue.

* Metastability No Longer Injected when a Synchronous Signal Toggles

You no longer see metastability effects being injected in simulation for

synchronous changes in input signals when the duration of the change is

smaller than the time window considered.

* Resolved Issue with Missing Default Clock Declaration

Assertions for constant signal constraints exported with "check_cdc -export

-type signal_config_property" now contain a sensitivity list with the fastest

clock available in the design.

For example:

//before

assert property (signal == 1'b0);

//after

assert property (@(posedge _clock) signal == 1'b0);

Connectivity Verification App

––––––––––––––-

* Macro Now Recognized as Expected in Source Block of Connection

Connectivity now processes macros on the source and destination block fields

of CSV files.

* Improved Blackbox Assistant Handling of Implicit Port Mapping Elements

Blackbox Assistant can now handle implicit port mapping elements (dot-star)

combined with port name mapping.

* Improved Error Messaging

Connectivity now correctly raises EWB045 or EWB04 when a signal does not

exist on the connection block but exists with the same name on the top module.

* Considering Clock Edge in PIPE Calculation

Reverse Connectivity now considers clock edge in PIPE calculation.

* Resolved Issue with Unexpected Connections

When running Reverse Connectivity, if you use the "-src" switch and the

instance has no output ports or you use the "-dest" switch and the instance

has no input ports, the Connectivity App stops and returns no connections.

Previously, the tool behaved as if the "-src" or "-dest" switches were not

passed to the command.

* Resolved Issue with EWB058 Error

Reverse Connectivity no longer issues EWB058 when the generated CSV file

includes function signals.

Connectivity Verification App and Coverage App

–––––––––––––––––––––––

* Resolved Issue with Undetectable COI

Intermediate wires of connections being checked by Connectivity are now,

once again, correctly reported as "Checked" by Coverage. This functionality

stopped working as expected with the 2022.12 release, but this release

resolves the issue.

Coverage App

––––––

* Resolved Issue with Proof Core when Property Proven with Engine PRE

Standard precision proof core now returns results with as much as or more

over approximation as high precision proof core.

* Resolved Issue with "Refresh Coverage Measurement" Button

Clicking the "Refresh Coverage Measurement" button in the COV GUI no longer

issues an invalid command to the console. Instead, this button issues

"check_cov -measure -refresh", which refreshes all tasks as expected.

* Disabled Assertions No Longer Spuriously Proven

Disabled properties copied among tasks are no longer spuriously proven by

Coverage Proof Core measurement in high precision mode.

* Resolved Issue with Unexpected ENL108 Error

With this release, Coverage completes the elaboration as expected when

macros are used.

* Flops Now Unchecked Only if Register Outputs Not in Proof Core

Beginning with this release, flops appear as unchecked only if their register

outputs are also not in proof core.

* Mutation Coverage Logs Now Show Percentage of Determined Cover Items

The mutation logs metric now prints the percentage of determined cover items

instead of the computing progress.

* Improved Show/Hide Columns Filter

Previously, in the Coverage App when you used the "Show/Hide Columns" filter

to show only relevant columns of the Expression and Toggle tables, the column

headers disappeared. This release resolves the issue.

* Detailed Report in GUI Now Shows Correct Coverage Percentage

The Detailed coverage model now shows correct results in the report summary

shown in the header of the table, which displays coverage percentage for

Formal, Stimuli, and Checker coverage.

* "check_cov -measure" No Longer Resets Coverage Results

Mutation results from a previous run are now reused as a starting point for

a later run.

* Resolved Issue with "check_cov -measure -refresh"

Prior to this release, the "-refresh" switch did computations, such as

traversals for COI, bound, and proof, when used with "check_cov -measure".

Now, "check_cov -measure -refresh" is interpreted as a "refresh after measure"

command that impacts only the GUI.

NOTE: The "-refresh" switch cannot be use with the "-type" switch.

* Coverage Now Supports Scoring of Expressions in Function Arguments

Coverage now scores VHDL expressions used inside function arguments.

Coverage Unreachability (UNR) App

––––––––––––––––-

* Resolved Issue with Incorrect UNR Marking

This release resolves an issue that might have previously led to incorrect

UNR marking for simple expressions.

* Resolved Spurious VHDL-1174 Error

This release resolves a spurious VHDL-1174 error found in VHDL component

instantiation with configuration.

Low Power Verification (LPV) App

––––––––––––––––

* LPV Now Correctly Handles "." as Current Scope in Top Module

LPV now correctly handles the use of dot (.) to represent the current scope

in the top module.

* Fixed Consistency of Retention Sub-Strategies Generated by LPV

Retention sub-strategies are now generated deterministically.

* Improved LPV "-signal -list" Command

"check_lpv -signal -list source_domain" and "check_lpv -signal -list

sink_domain" now return unique values and do not consider the domains that

include the supply nets.

* Now Displaying Low Power Corruption Annotation in Waveforms by Default

***IMPORTANT: CHANGE IN TOOL BEHAVIOR***

Low power corruption annotation in Visualize waveforms is now enabled by

default. Thus, corrupted signals have a red cross-hatch annotation for the

cycles where their related power domain is off.

Use the "set_lpv_enable_corrupt_annotation off" command to disable this

feature .

Security Path Verification (SPV) App

––––––––––––––––––

* "visualize -stopat" Blocked for X-Prop and SVA Traces

You can no longer use "visualize -stopat" on an X-Prop or SPV trace.

* "-no_preconditions" Switch Replaced with "-no_precondition_covers"

This release replaces the "-no_preconditions" switch of the "check_spv

-create" command with "-no_precondition_covers". The old "-no_preconditions"

switch has been maintained for backward compatibility but will be removed

in a future release.

Sequential Equivalence Checking (SEC) App

––––––––––––––––––––-

* Incremental Elaboration Automatically Disabled on Initialization

With this release, the following apps automatically disable

"incremental_elaborate_wrapper_mode" on initialization:

. SEC (Excluding hierarchical flow)

. SPV

. XPROP

. FSV

* Resolved Issue with Unexpected Exit after Incremental Elaboration

SEC, SPV, FSV, and SPV now automatically enable "elaborate_single_run_mode".

This setting cannot be changed for these apps.

* Imp Packages Now Displayed on Right Side as Expected

Jasper FSV, C2RTL, and SEC Apps now show packages and compilation units from

the imp side on the right side of the hierarchy and source browser windows.

Superlint App

––––––-

* ASG_IS_OVFL Now Supported for Assignment Statements

Superlint now supports ASG_IS_OVFL checks for continuous assignments.

* Improved MOD_NR_SYXZ Check

MOD_NR_SYXZ is now generated as expected when "skip_tristate_logic" is set to

"yes".

* Improved SHF_IS_ABSO Check

Shift operations that include constant RHS no longer generate all bits

are lost violations.

* Resolved Issue with PRT_NR_ORDR

Superlint now reports PRT_NR_ORDR violations as expected, though only one

violation is reported in the GUI. all connected violations are passed to an

extra data report.

* ESW023 No Longer Issued Unexpectedly

Previously, Superlint might have exited unexpectedly with ESW023 in the event

of a loop. This release resolves the issue.

* Improved FIL_NR_MLEN Check

Superlint no longer considers the size of macro expansions as part of the

physical line length.

* Resolved Violations Tree Refresh Issue

Previously, the error and warning count on the Superlint violations tree

might not have been updated after adding waivers. This release resolves the

issue.

* Resolved Issue with Spurious FNC_MS_MTYP/FNC_MS_AFPR Violations

Superlint no longer issues FNC_MS_MTYP or FNC_MS_AFPR violations if a

function is declared in class.

X-Propagation (XPROP) Verification App

–––––––––––––––––––

* Expert System No Longer Supports SPV or X-Prop

Beginning with this release, the Jasper Expert System does not support the

SPV or X-Prop Apps. Thus, running "check_spv -init" or "check_xprop -init"

automatically disables the Expert System.

This limitation will be removed in a future release.

Visualize

––––-

* Resolved Issue with Spurious ETR032 Errors

Jasper no longer issues spurious trace inconsistency errors (ETR032) when

clocked bounded assumptions are present. Previously, clocked bounded

assumptions triggered a pessimistic inconsistency check.

* Resolved Issue "visualize -trace_id"

The "visualize -trace_id" command now shows the following error when used

without the switch "-property":

ERROR (ESW011): The "-trace_id" switch is only allowed with "-property"."

The TclHelp for "visualize -trace_id" was updated to reflect more accurately

the tool behavior. This switch selects one trace to plot when a property has

multiple traces. You must combine it with "-property" to indicate which

property the ID is related to.

Auto Black Box

–––––––

* Blackbox Assistant Not Supported with CDC, COV, FSV, Superlint, SEC, UNR

Jasper does not currently support using Blackbox Assistant with CDC, COV,

FSV, SUPERLINT, SEC, or UNR.

Clocks and Reset

––––––––

* ESW064 Now Issued if "-none" Is Used with Reset Expression

When "reset -formal -none" is used with a reset expression, the tool now

issues ESW064.

Clocks and Reset and Engines

––––––––––––––

* Improved Messaging for Property Declaration

When a property is declared with @(edge <clock name>) or @(<clock name>)

and its clock is not declared as -both_edges, the tool now displays the

following downgradable error:

ECK062: Jasper detected a property that requires a different clock declaration

for clock <clock name>.

Consider changing the clocking of the property, or declare clock

<clock name> with both_edges.

Use "sanity_check" for more information about which clocks have an

inconsistent clock declaration.

NOTE: The fix addresses only properties with a simple clock without factors

declared with @(edge <clock name>) or @(<clock name>). It DOES NOT cover

property declarations with @(posedge clk or negedge clk) or flop declarations,

gated clock declarations, or slow clock declarations. These situations

still do not result in an error.

Deep Bug Hunting

––––––––

* Resolved Issue with Spurious EHT003 Errors

Previously, the tool might have generated an invalid set of first trace

attempts and issued an error if you defined invalid "max_first_trace_attempts"

with engine Bm for Cycle Swarm and Bound Swarm "hunt" strategies. This release

resolves the issue.

* Handling Property Names with Name Clashes and Escaped IDs

Now, Jasper correctly handles property names with escaped IDs when there are

name clashes with other properties or signals.

Design Compilation

–––––––––

* Signals No Longer Incorrectly Reported as Multiple-Driven

Jasper no longer incorrectly reports signals as multiple-driven.

* Issue with Default Clocking Clauses Resolved

The Jasper clock flow is now correctly resolved concerning default clocking

clauses together with SystemVerilog interfaces.

* "connect -bind" Now Returns Warning Instead of Exiting Unexpectedly

Jasper no longer exits unexpectedly when the "connect -bind" command binds

one bus of multidimensional array input port to the elaborated module

port bus. If the port cannot be connected, the tool now issues a message like

the following:

WARNING (WNL024): Connect: unable to connect port

"i_cpux_link0_rom_start_addr[0]"

* VERI-2669 Now Issued when "disable iff" Used as Property Operand

Jasper now issues the following error when a property instance with disable

iff clause is used as a property operand:

[ERROR (VERI-2669)] test.v(16): property instances with disable iff cannot be

used as operand of property expression

* Spurious ENL163 Errors No Longer Issued

This release resolves an unexpected elaboration error related to invalid

external references involving missing indexation, for example, "m1i.si.b",

where "m1i" is an external module instance and "si" is an array without

indexation.

* Resolved Issue with "elaborate -extract_case_assertions"

Now, when extracting case assertions (elaborate -extract_case_assertions),

unique and unique0 automatic properties follow section 12.5.3 of the

SystemVerilog LRM'17 and do not fail if more than one case item expression

matches the case expression in a single case item.

NOTE: Related Superlint properties have also been impacted by this change.

* Resolved Issue with Property Hash Mismatch

This release resolves an issue with non-determinism in property hash when

running a design with hierarchical references in different sessions.

* Resolved Elaboration Run Time Degradation Introduced in 2022.09

Fixed elaboration performance degradation that might have affected modules

with many unresolved references.

Design Compilation and Infrastructure

––––––––––––––––––-

* WOBS004 Now Upgradeable

You can now upgrade WOBS004 to an error with the following command:

set_message -error WOBS004

To revert, use "set_message -warning WOBS004".

Design Compilation and Language Support

–––––––––––––––––––-

* Resolved Unexpected Exit During Elaboration

The related cover preview flow no longer exits unexpectedly when a functional

with only internal signals has a loop in itself, for example,

$past(function_call(sig)).

Design Exploration

–––––––––

* "show_source_browser -signal" Now Accepts Packed Structs

Now, "show_source_browser -signal" accepts packed struct signals as argument.

Infrastructure

–––––––

* Resolved Issue with "export -to_sva"

"export -to_sva" now correctly exports the reset expression when there is an

"assume -bound".

Infrastructure and Proofs and ProofGrid

–––––––––––––––––––-

* Jasper No Longer Exits Unexpectedly on Long Directory Path Name

Jasper no longer exits unexpectedly when the path to the "trace database"

file is too long. However, the solution to avert this issue comes at the

cost of traces not being "converted", which means that affected properties

do not have any traces, though their statuses are updated properly. When a

problematic situation has been detected during a proof, Jasper issues error

message ETR087 for every failure to "convert" a trace. For example,

ERROR (ETR087): Unable to convert trace for "counter == 'hF0".

Details: database connection failure: unable to open database file

NOTE:

. By default, the "trace database" file is located in the project directory.

. What the tool determines to be too long is dependent on the system and can

even be different for different paths on the same system since it might

depend on the file system type.

Language Support

––––––––

* Resolved Issue with Unexpected Precondition Expression

This release resolves an issue with the synthesis of precondition expressions

with the following pattern:

@(posedge clk) disable iff (rst) expr1 ##1 1'b1 |-> expr2

Before this change, Jasper created a precondition like the following:

@(posedge clk) disable iff (rst) expr

However, the 1'b1 cannot be optimized since there is still one cycle for

which disable iff might work. The precondition Jasper now generates follows:

@(posedge clk) disable iff (rst) expr1 ##1 1'b1

Miscellaneous

––––––-

* Updated CDC Documentation for "all_clocks_sync_by_default=false"

The CDC documentation now includes information on "all_clocks_sync_by_default=

false" for all applicable examples.

* Corrected Typo in the "set_sec_show_proof_log" Command Documentation

The Jasper Apps Command Reference Manual now shows the proper options for the

"set_sec_show_proof_log" command.

* Corrected Documentation for the "-cov_init" Command-line Options

The Jasper Apps Command Reference Manual now shows the proper options for the

"-cov_init" command-line options.

* Correctly Mapping SDC Constraint Targets when Using VHDL

You can now use the new "set_sdc_vhdl_expr_mode on" command to enable the

processing of SDC files in VHDL. By default, the tool processes SDC commands

in Verilog (sdc_vhdl_expr_mode=off).

Proofs and ProofGrid

––––––––––

* Proof Structure Now Updates GUI as Expected in the Absence of Any Operation

Proof Structure now shows results on root nodes even when the root node has

no operation.

* ProofMaster Cache Now Generating Consistent Results for Liveness

The information retrieved from the cache and displayed in the Property Table

is now consistent across runs as expected.

* Improved ProofMaster Summary

The ProofMaster summary report now includes visible build-in targets and is,

thus, more consistent with what the regular proof summary reports.

* Corrected ProofMaster Summary

When there are no properties to prove, the ProofMaster summary now shows

"0%" instead of "-nan%".

Property and Configuration Database

–––––––––––––––––-

* Improved Messaging for "get_property_list -task"

Previously, the command "get_property_list -task" returned the properties of

the current task if the specified task was not found. With this change, when

at least one of the task names specified is not found, the command issues a

warning. If none of the specified task names are found, it issues an error.

User Interface

–––––––

* Failed :live Property No Longer Reported as Vacuous

When the :live property fails, all liveness properties are labeled vacuous,

but the :live property itself is no longer reported as vacuous.

Verification Management

–––––––––––-

* Jasper Now Supports "assume -from_assert -env"

You can now use the "-env" switch with "assume -from_assert" to apply a newly

created assumption to the global environment instead of the current task.

Deprecation Notices

===================

The following commands are being deprecated.

The tool issues a warning if you use the following commands. No changes to

your scripts are required at this time; however, in a future release, these

commands will trigger a downgradable error message, and ultimately, they will

be retired. We strongly encourage you to adjust your scripts as soon as it

is practical to do so.

. check_cdc -filter -add -source_domain: Use "-source_clock_domain" instead.

. check_cdc -filter -add -destination_domain: Use "-destination_clock_domain"

instead.

. check_cdc -filter -add -source_reset: Use "-local_source_reset" instead.

. check_cdc -filter -add -destination_reset: Use "-local_destination_reset"

instead.

. check_cdc -filter -add -source_declared_resets: Use "-source_reset_domain"

instead.

. check_cdc -filter -add -destination_declared_resets: Use

"-destination_reset_domain" instead.

. check_cdc -filter -add -reset_sources: Use "-reset_domain" instead.

. check_superlint -waiver -add -message: Use "check_superlint -waiver -add

-argument" instead.

. visualize -explore

The following commands have been deprecated, and any use of them triggers a

downgradable error message. Remove them from your scripts or use

"set_message -warning". These commands will be retired in a future version of

the tool.

. check_lpv -save triggers EDEP283: Use "save -elaborated_design" instead.

. check_lpv -restore triggers EDEP283: Use "restore -elaborated_design" instead.

. export -afl: Use "check_superlint -export" instead or "set_message -warning

EDEP287" to downgrade this message to a warning.

. export -sps: Use "check_superlint -export" instead or "set_message -warning

EDEP287" to downgrade this message to a warning.

. export -superlint: Use "check_superlint -export" instead or "set_message

-warning EDEP287" to downgrade this message to a warning.

. check_superlint -waiver -import -text_format triggers ESL042: Use

"check_superlint -waiver -import -file_name" to generate a Tcl waiver file.

. check_superlint -waiver -add -check_type triggers ESL041

. check_superlint -waiver -list -check_type triggers ESL041

. check_superlint -waiver -export -text_format triggers ESL043

. set_auto_bothedge_optimization triggers EDEP290

. get_auto_bothedge_optimization triggers EDEP290

. prove -max_licenses: Use "prove -per_engine_max_jobs" instead or "set_message

-warning EPF111" to downgrade this message to a warning.

. set_proofgrid_privileged_licenses: Use

"set_jasper_proofgrid_per_engine_privileged_jobs" instead or use "set_message

-warning EPF110" to downgrade this message to a warning.

. get_proofgrid_privileged_licenses: Use

"get_jasper_proofgrid_per_engine_privileged_jobs" instead or use "set_message

-warning EPF110" to downgrade this message to a warning.

. set_proofgrid_max_local_licenses: Use

"set_jasper_proofgrid_per_engine_max_local_jobs" instead or use "set_message

-warning EPF109" to downgrade this message to a warning.

. get_proofgrid_max_local_licenses: Use

"get_jasper_proofgrid_per_engine_max_local_jobs" instead or use "set_message

-warning EPF109" to downgrade this message to a warning.

. set_proofgrid_max_licenses: Use "set_jasper_proofgrid_per_engine_max_jobs"

instead or use "set_message -warning EPF108" to downgrade this message to a

warning.

. get_proofgrid_max_licenses: Use "get_jasper_proofgrid_per_engine_max_jobs"

instead or use "set_message -warning EPF108" to downgrade this message to a

warning.

. jg_history triggers EDEP284: Use "jasper_history" instead or use

"set_message -warning EDEP284" to downgrade this message to a warning.

. set_jg_history_per_command_limit triggers EDEP285: Use

"set_jasper_history_per_command_limit" instead or use "set_message -warning

EDEP285" to downgrade this message to a warning.

. get_jg_history_per_command_limit triggers EDEP285: Use

"get_jasper_history_per_command_limit" instead or use "set_message -warning

EDEP285" to downgrade this message to a warning.

The following commands are retired. They no longer have any effect, and you

should remove them from your scripts.

. get_fanin -addClockLogic: Use "get_fanin -add_clock_logic" (snake case).

Changes in Messaging

====================

Also see sections above.

***** Messages Removed from the Current Version *****

EXPR004: error {EXPR004 {{Unable to start the proof. The required setting for the "-leverage_sec" switch was not completed before design setup.}}}

WDFV008: warning {WDFV008 {{The expression computed for signal %s at time %s (sequence %s) is not boolean.}}}

––-

***** Messages That Were Introduced in the Current Version *****

EAS033: error {EAS033 {{Cannot convert X-Prop assertions to environment assumptions.}}}

ECDC135: error {ECDC135 {{The CDC App has not been initialized. You must first run "check_cdc -init".}}}

ECDC136: error {ECDC136 {{Unable to initialize CDC App because {app_name} App is already initialized.}}}

ECK062: error {ECK062 {{Jasper detected a property that requires a different clock declaration for clock "%s".\n Consider changing the clocking of the property, or declare clock "%s" with both_edges.\n Use "sanity_check" for more information about which clocks have an inconsistent clock declaration.}}}

ECOV083: error {ECOV083 {{The "-set_bound_analysis" subcommand works with assertions only.}}}

ECOV084: error {ECOV084 {{The "-set_bound" switch does not work on CEX or Proven targets.}}}

ECSR033: error {ECSR033 {{Cannot load a .csv file with "check_csr -load_ipxact". The file must be an IP-XACT .xml file.\n Use "check_csr -load" to load a .csv workbook.}}}

ECTR062: error {ECTR062 {{Unable to find Property {property}.}}}

ECTR063: error {ECTR063 {{C/C++ linker error in file "{file}", line {line}:\n {error}}}}

ECTR064: error {ECTR064 {{Cannot %s property "%s" as this enum constraint is already embedded in the model.}}}

ECTR065: error {ECTR065 {{Formal model generation errors have been found.}}}

EDA003: error {EDA003 {{An internal error has occurred in the %s setup. Results are not guaranteed to be accurate.\n Contact support@cadence.com for additional information.}}}

EDA004: error {EDA004 {{%s encountered %s error(s).}}}

EDA010: error {EDA010 {{Cannot use the "check_{app1} -init" command after initializing the {app2} App.}}}

EDA011: error {EDA011 {{Cannot run "prove" on task while a background proof is running.\n Use "-basic" to run "prove" in parallel.}}}

EDA012: error {EDA012 {{Cannot run "prove" on task while a background proof is running.}}}

EDA013: error {EDA013 {{Cannot add a Visualize stopat on an X-Prop or SPV trace.}}}

EDEP283: error {EDEP283 {{The subcommands "check_lpv -save" and "check_lpv -restore" have been deprecated.\n Please use "save -elaborated_design" and "restore -elaborated_design" instead or use "set_message -warning EDEP283" to downgrade this message to a warning.}}}

EDEP284: error {EDEP284 {{The command "jg_history" has been deprecated and will be removed in the next release.\n Use "jasper_history" instead or use "set_message -warning EDEP284" to downgrade this message to a warning.}}}

EDEP285: error {EDEP285 {{The command "get/set_jg_history_per_command_limit" has been deprecated and will be removed in the next release.\n Use "get/set_jasper_history_per_command_limit" instead or use "set_message -warning EDEP285" to downgrade this message to a warning.}}}

EDEP286: error {EDEP286 {{The command "get/set_jg_history_arg_limit" has been deprecated and will be removed in the next release.\n Use "set_message -warning EDEP286" to downgrade this message to a warning.}}}

EDEP287: error {EDEP287 {{The command "export -superlint|-afl|-sps" has been deprecated.\n Use "check_superlint -export" instead or "set_message -warning EDEP287" to downgrade this message to a warning.}}}

EDEP288: error {EDEP288 {{The command "get/set_visualize_enable_quiet_last_cycles" has been deprecated.\n Remove it or use "set_message -warning EDEP288" to downgrade this message to a warning.}}}

EDEP289: error {EDEP289 {{The command "get/set_visualize_enable_quiet_selected_signals" has been deprecated.\n Remove it or use "set_message -warning EDEP289" to downgrade this message to a warning.}}}

EDEP290: error {EDEP290 {{The command "get/set_auto_bothedge_optimization" has been deprecated.\n Remove it or use "set_message -warning EDEP290" to downgrade this message to a warning.}}}

EDEP291: error {EDEP291 {{The command "%s" has been deprecated and will be removed in the next release.\n Use "%s" instead or use "set_message -warning EDEP291" to downgrade this message to a warning.}}}

EFSV092: error {EFSV092 {{FSV does not support "elaborate %s".}}}

EFSV093: error {EFSV093 {{FSV does not support the "connect %s" command.}}}

EMTR414: error {EMTR414 {{%s does not support "elaborate %s".}}}

EMTR415: error {EMTR415 {{Running the clock gating proof strategy requires %s jobs, but max jobs is only %s.\n Either change proof strategy to basic or increase max jobs.}}}

EMTR416: error {EMTR416 {{Miter had %s error(s).}}}

ENL195: error {ENL195 {{"elaborate_single_run_mode" has been automatically {enabled_or_disabled}.\n "set_elaborate_single_run_mode" must be "{on_or_off}" to use this app or flow, and you cannot change this setting.\n Run "clear -all" to run a different app or flow.}}}

ENL196: error {ENL196 {{This app or flow does not support incremental elaboration.\n Run "clear -all" to run a different app or flow.}}}

EPF104: error {EPF104 {{{thread_id}: Morphing to a new engine when the proof is running with engineDFV alone is not supported.}}}

EPF105: error {EPF105 {{{thread_id}: Adding a new engine when the proof is running with engineDFV alone is not supported.}}}

EPF106: error {EPF106 {{{thread_id}: Running a new engine when the proof is running with engineDFV alone is not supported.}}}

EPF107: error {EPF107 {{{thread_id}: No eligible engines in engine mode.}}}

EPF108: error {EPF108 {{The command "get/set_proofgrid_max_licenses" has been deprecated and will be removed in the next release.\n Use "get/set_proofgrid_per_engine_max_jobs" instead or use "set_message -warning EPF108" to downgrade this message to a warning.}}}

EPF109: error {EPF109 {{The command "get/set_proofgrid_max_local_licenses" has been deprecated and will be removed in the next release.\n Use "get/set_proofgrid_per_engine_max_local_jobs" instead or use "set_message -warning EPF109" to downgrade this message to a warning.}}}

EPF110: error {EPF110 {{The command "get/set_proofgrid_privileged_licenses" has been deprecated and will be removed in the next release.\n Use "get/set_proofgrid_per_engine_privileged_jobs" instead or use "set_message -warning EPF110" to downgrade this message to a warning.}}}

EPF111: error {EPF111 {{The command "prove -max_licenses" has been deprecated and will be removed in the next release.\n Use "prove -per_engine_max_jobs" instead or use "set_message -warning EPF111" to downgrade this message to a warning.}}}

EPGJ006: error {EPGJ006 %s}

EPGJ007: error {EPGJ007 {{Unable to %s server with Jasper Cloud solution pipe mode.}}}

EPGJ008: error {EPGJ008 {{Invalid server ID.}}}

EPGJ009: error {EPGJ009 {{Unable to communicate with Jasper Cloud solution Manager.}}}

EPST048: error {EPST048 {{Unable to proceed with restoration of Proof Structure because of deprecated property "{propName}".\n Proof Structure cannot contain deprecated properties.}}}

ERS065: error {ERS065 {{The argument to "start_formal_bound" must be an integer between 0 and the sequence's total number of cycles.}}}

ERTL042: error {ERTL042 {{Configuration name "%s" is already used.}}}

ERTL043: error {ERTL043 {{Unable to continue as no supported app was initialized.\n You must first run "check_cdc -init" or "check_superlint -init".}}}

ESCH023: error {ESCH023 {{The design contains non-printable characters, which are not supported by the Schematic Viewer.}}}

ESEC391: error {ESEC391 {{An invalid elaborated design has been found for {spec_or_imp} side.\n Design must be elaborated with SEC commands.}}}

ESEC392: error {ESEC392 {{Specified directory must contain one elaborated design file only while using SEC compile context.\n Specify path of desired elaborated design file instead.}}}

ESEC393: error {ESEC393 {{Switch "{switch}" is not supported with "set_sec_elaborate_mode on".}}}

ESL041: error {ESL041 {{The switch "-check_type" has been deprecated.}}}

ESL042: error {ESL042 {{The waivers text file is deprecated.\n Use "check_superlint -waiver -import file_name" to generate a tcl waiver file.}}}

ESL043: error {ESL043 {{The waivers export with "text_format" switch is deprecated.\n Use "check_superlint -waiver -export -file_name file_name" to generate a Tcl waiver file.}}}

ESPV339: error {ESPV339 {{No signals matched the specified wildcard(s) %s.}}}

ESPV340: error {ESPV340 {{No signals or instances match the wildcard(s) passed to the "%s" %s.}}}

ESPV341: error {ESPV341 {{Invalid signal: The signal %s does not exist in this design.}}}

ESPV342: error {ESPV342 {{Invalid instance: The instance %s does not exist in this design.}}}

ESR019: error {ESR019 {{Periodic save is already running.\n Run "set_save_restore_periodic_save off" or "clear -all" before trying to save a new database.}}}

EVS177: error {EVS177 {{QuietTrace stopped with {remaining} remaining soft constraints. Satisfied: {satisfied}. Not Satisfied: {failed}.\n Proof has timed out, exceeded memory limit, or found another issue.}}}

EVS178: error {EVS178 {{The "visualize -replot" command does not support traces originated from a "prove -sst" flow.}}}

EVS179: error {EVS179 {{"visualize -sst" is not supported in the presence of a Compositional Assume-Guarantee assumption.}}}

EWB059: error {EWB059 {{Missing keyword "%s".}}}

EXPR018: error {EXPR018 {{Only the "basic" proof strategy provides the option to specify an engine mode.}}}

EXPR023: error {EXPR023 {{An internal error has occurred. Any results produced by this command are not guaranteed.\n Contact support@cadence.com for additional information.}}}

EXPR024: error {EXPR024 {{You must run "check_xprop -init" before running this command.}}}

EXPR025: error {EXPR025 {{X-Prop supports only "trace_extension" value 0.\n To enable the X-Prop proof run, use the following command: "set_trace_extension 0"}}}

EXPR026: error {EXPR026 {{Cannot run prove on X-Prop task while a background proof is running.}}}

EXPR027: error {EXPR027 {{Cannot run prove on X-Prop task while a background proof is running.\n Use "-basic" in order to run prove in parallel.}}}

EXPR028: error {EXPR028 {{X-Prop does not support the "visualize -replot" command.}}}

ICTR028: info {ICTR028 {{%s%u.%s: The Property "%s" under case %s was proven in %s.}}}

ICTR029: info {ICTR029 {{%s%u.%s: The Cover property "%s" under case %s was proven unreachable in %s.}}}

ICTR030: info {ICTR030 {{%s%u.%s: A counterexample (cex) with %u cycles was found for the property "%s" under case %s in %s.}}}

ICTR031: info {ICTR031 {{%s%u.%s: The Cover property "%s" under case %s was covered in %u cycles in %s.}}}

ICTR032: info {ICTR032 {{The Property "%s" was proven in %s.}}}

ICTR033: info {ICTR033 {{The Cover property "%s" was proven unreachable in %s.}}}

IDA011: info {IDA011 {{Preparing %s environment - started.}}}

IDA012: info {IDA012 {{Preparing %s environment - done.}}}