Cadence INNOVUS version 21.10.000 Base | 5.8 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled INNOVUS 21.10.000 is part of the broader Cadence digital and signoff suite, which provides customers with an integrated full flow, delivering a predictable path to design closure and also supports Cadence’s Intelligent System Design strategy, accelerating SoC design excellence.

CCMPR02229629 BUMP to Via spacing not honoring blockage spacing

CCMPR02213338 oasisOut broken in 19.13

CCMPR02210511 SEGV in clkPRO

CCMPR02207769 Internal error messages during optDesign at PRO stage

CCMPR02202724 ecoRoute not able to fix M1 DRC that can be fixed manually

CCMPR02201772 Preferred layer effort on clock nets not honored during ccopt_design V2

CCMPR02199590 saveDesign crash in 19.13-e033_1 (during saving pin access .apa file)

CCMPR02197202 SEGV observed during saveDesign

CCMPR02196641 tquantus signature flow hangs on top level design

CCMPR02195393 verifyPowerDomain -aoBufferType returns unwanted information

CCMPR02195093 Mixed placer places all HB with R90 orientation, although R90 R270 is allowed

CCMPR02194146 refine_macro_place hang

CCMPR02193823 Crash while running Floorplan tag

CCMPR02192205 fix_floorplan creates a rectangular routing blockage over a rectilinear shape

CCMPR02192195 SEGV observed during synthesize_ccopt_flexible_htrees

CCMPR02192020 SEGV during clock detail routing with 19.11

CCMPR02191939 Innovus crash during layer assignment due to route_design_top_routing_layer -1

CCMPR02191937 check_tracks crash due to route_design_top_routing_layer -1

CCMPR02191827 SEGV when compressedPGDB

CCMPR02190458 time_design shows more max_tran violations than report_constraints

CCMPR02189957 Memory jump during area/power/drv/setup Reclaim of place_opt_design

CCMPR02187977 verify_drc SEGV on IO Block

CCMPR02187892 place_opt_design crashes

CCMPR02186949 Innovus Timing Path Analyzer - Path SDC reports wrong SDC

CCMPR02186533 tQuantus extraction with compressed PG very slow

CCMPR02186528 SEGV during route_design

CCMPR02186365 addRepeaterByRule hangs

CCMPR02185337 saveDesign crashing in 18.16-e018_1

CCMPR02184701 Running flow tool Innovus crash at route

CCMPR02184668 Crash while running build_db target

CCMPR02183510 Add warning about not honoring user ggrid size setting if it will cause overflow

CCMPR02183022 Tool hangs at PRO hold stage during timing analysis

CCMPR02182632 optDesign -postRoute is crashing while clock DRV fixing

CCMPR02182538 prects segv: lsUsefulSkewToolboxCL.cpp dumpSDCInfoForDisabledViews

CCMPR02182076 Via Pillar leaves avoidable EndofLine SameMask spacing violations in-between

CCMPR02181237 checkplace does not report a strict point touch violation in the presence of placement blockage

CCMPR02181038 CTS routing Struck due to Memory Corrupted Error

CCMPR02180598 add_stripes causes DRCs by choosing the wrong VIA model

CCMPR02180502 Divider flop D pin balancing in CTS

CCMPR02179953 setAddStripeMode -keep_pitch_after_snap false is a part of PG script and cannot be converted to common UI

CCMPR02179239 Cannot create stripe with width upper that design height when design is thin

CCMPR02178155 Preferred layer effort on Clock nets not honored during ccopt_design

CCMPR02178143 Placement blockages shifted with createPlaceBlockage -boxList

CCMPR02178078 write_stream issues sub-block during GDSII export at top level not done

CCMPR02177656 saveDesign crashes in dbsSaveDesignSymbolTable::getPGTermId after deleteInst of TAP cells

CCMPR02177466 ecoRoute Scalability Statistics table is missing components

CCMPR02177350 route_secondary_pg_pins runtime degradation 18.14 vs 19.12

CCMPR02176589 routePGAsSignalRoute routed to lower layers after removing BottomRoutingLayer 4 and using preferred layer attribute

CCMPR02176537 Type fills routing blockage is not properly handled by verify_drc and verifyGeomentry commands

CCMPR02176194 Secondary PG high resistance problem

CCMPR02175736 Error when trying to run optDesign -postRoute -targeted -incr

CCMPR02175576 add_well_taps_insert_cells not accounting for last well_tap to boundary check

CCMPR02175545 set_flowkit_write_db_args does not accept new write_db options

CCMPR02175212 Innovus 19.11 got crash at sroute

CCMPR02175180 Innovus tool crashes during refinePlace

CCMPR02174968 write_multi_bit_flop_mapping_file needs to be able to direct output to a location

CCMPR02174964 gui_bind_key command sourced through GUI Menu tab is causing error IMPQTF-4044

CCMPR02174278 sroute do not create followpin connection for powerNet defined as bus

CCMPR02174256 Routing QOR is much degraded in 18.1x as compared to 17.1x

CCMPR02174227 powerVia enclosure does not match stripe width

CCMPR02173977 Another unspecifyIlm crash when ILM and UPF is used

CCMPR02173882 unflattenIlm crashed with 19.11 and 19.12

CCMPR02173861 Placeopt job is stuck while executing the place_opt_design command

CCMPR02173108 write_lef_library dumps out integer 0 for MINSPANLENGTH instead of 0.000

CCMPR02173067 M3 pins are not aligned with the tracks

CCMPR02172322 SEGV user defined attribute with set function

CCMPR02169916 The oaPurpose argument in add_text command does not work

CCMPR02169688 Empty '+ PORT' statements in DEF after delete_obj $thePortShapes

CCMPR02169625 clock_design runaway memory consumption during reducing clock tree power

CCMPR02169420 Innovus 19.11 got crash with place_opt_design -opt

CCMPR02167674 ecoDesign does not appear to read previously saved metrics and hence not appending to previous metrics

CCMPR02167436 During iSpatial flow in genus, Innovus terminated by SEGV while reading timing constraints

CCMPR02167335 Huge run Time during globalDetailRoute at detail pin access analysis

CCMPR02167209 setobjFPlanPolygon command to give warning/error message to improve usability

CCMPR02166582 Need method in verify_drc to ignore or override cell density checks

CCMPR02166218 globalDetailRoute runtime is too high for top level

CCMPR02166025 colorizeGeometry within placeDesign takes close to 5hrs

CCMPR02165892 Blocking issue for optDesign -trackOpt: tQuantus fails because of wrong auto mapping file while iQuantus runs fine

CCMPR02165496 Chip Top Stripegen Run time increases in P3 compared to P2

CCMPR02165436 CreateRow/initCoreRow creates rows outside core area

CCMPR02164744 addStackingVia on nets with NDR attribute fail with no Via Connection

CCMPR02164631 set_ideal_net crashes with DPO list

CCMPR02164462 route_flip_chip causes DRCs due to wrong way routing

CCMPR02164016 defIn/defOut runtime and memory issue

CCMPR02163872 Stack trace during clock_design

CCMPR02163206 route_special does not route over some endcaps

CCMPR02163202 oasisOut properties missing in 19.1*

CCMPR02162910 Innovus is not fixing Hold violations due to the fake congestion it's seeing during PRO step

CCMPR02162759 globalNetConnect does not report any errors/warning even though those pins does not exist

CCMPR02161151 Different pin placement results with assign_pins_edit_in_batch true vs false

CCMPR02160560 19.11/19.12 not inserting level shifters, UPF was working in 18.14/18.15

CCMPR02160518 Innovus 19.11 SEGV when I try to close a Kit menu

CCMPR02159270 Flattening connects wires of local power nets together

CCMPR02159151 Block crashes during ccopt_design in 19.12-e030_1 version

CCMPR02158986 The routeDesign -viaOpt fails to change single-cut to Multi-cut via

CCMPR02158869 editPowerVia to avoid using stack via

CCMPR02158434 Chip Top Run time increases in P3 compared to P2 for all Floorpaln flow Nodes

CCMPR02158243 timing_enable_multi_threaded_reporting set at false by route_design

CCMPR02157856 Zero Spacing OBS on non-orthogonal cut layer is showing false spacing violations

CCMPR02157708 editPowerVia -split_long_via is inconsistent in dropping PG vias in multiple rows

CCMPR02157331 Innovus did not keep terminals locations when creating a new logical Hierarchy

CCMPR02156819 Add jog_connect -layer option to move wire drop-down menu

CCMPR02156802 Miscorrelation between the EditMode setting and the GUI window

CCMPR02155959 gui_highlight - instant crash with invalid pattern

CCMPR02155957 Innovus is getting stuck at globalDetailRoute during Generating timing data

CCMPR02155385 Crash during routeDesign

CCMPR02153771 Innovus is getting crashed while running 'addWellTap'

CCMPR02153463 False VT violations reported by Innovus

CCMPR02151053 Innovus placeSpareModule command crash

CCMPR02150717 Nets with preferred bottom layer = 12 routed on 4 and router does not connect to top of via pillar stack

CCMPR02150607 Loading floorplan file in restoreDesign with design that was properly saved results in error IMPFP-707

CCMPR02150427 fix_ufc not following the macro profile when cutting ROWS around a multi-linear macro

CCMPR02150367 Massive number of IMPSP-5225 messages causing terabytes of log even when message_limit is 20

CCMPR02150268 unspecifyIlm crash when ILM and UPF used

CCMPR02149897 False parallel run length spacing in Innovus

CCMPR02149012 Flop merging left dangling instances in netlist that are not removed

CCMPR02148290 add_fillers corrupting y_flip_type

CCMPR02147778 editPowerVia long runtime

CCMPR02147686 fcroute length matching using the constraint file

CCMPR02147045 Right mouse click on cell obstruction results in SEGV

CCMPR02146910 ecoAddRepeater is crashing with hinstGuide option

CCMPR02146651 selectSecondaryPGNet issues when secondary PG has two pin shapes

CCMPR02146297 Setting opt_fix_hold_allow_setup_tns_degradation option to true is degrading Setup WNS during postCTS hold fix

CCMPR02146294 Innovus SEGV during write_db

CCMPR02145977 Tool is crashing during the ecoRoute step in Innovus

CCMPR02145497 ccopt_design long runtime in clustering

CCMPR02145489 Bug in error message IMPOPT-7027

CCMPR02145382 report_hidden_usage hangs, no return

CCMPR02143882 High DRC count seen with binary when run on UHD libs

CCMPR02143374 Innovus crash (seg fault) when attempting to overwrite existing OA library

CCMPR02143352 19.12 breaks scan chains during MBFF merge/split

CCMPR02143189 New Command to support sizing up/Down the bus bit

CCMPR02143110 MergeHierDef drops the pin shape of the block if RDL's DEF presented and caused I/O net to be skipped in signal EM analysis

CCMPR02143008 synthesize_ccopt_flexible_htrees hang

CCMPR02142308 addStripe hangs

CCMPR02142230 Innovus leaving many DRCs after routeDesign on a CTS DB

CCMPR02141093 Fatal error out during restore partition design.

CCMPR02140636 restoreDesign removing GNCs of secondary pgPin of cells when saved design executed with the globalNetConnect command

CCMPR02140403 saveDesign crash at postcts when ILM and UPF is used

CCMPR02139508 ecoRoute crash. Customer is in the eco phase and need quick help.

CCMPR02139269 add_io buffers takes long time to flip the inst to match row orientation

CCMPR02138981 restoreDesign hangs

CCMPR02138735 NR leaves partially open net in 19.1/19.2 but routes cleanly in 18.1

CCMPR02136378 Innovus read Virtuoso OA DB got wrong instance coordinate transform

CCMPR02136321 eco_pnr stage crashes during ecoRoute

CCMPR02135600 saveDesign crash while saving route file

CCMPR02134426 placeObject crashes when placement blockage is copied from GUI using copy button equivalent to uisetTool copy

CCMPR02133981 A proc with a foreach with a try/trap that is false, crashes 19.1 Innovus Legacy

CCMPR02133766 Innovus is crashing during postRoute OptDesign with internal (SEGV) error/signal

CCMPR02133363 ccopt places clock buffers where it is impossible to route the stacked vias cleanly

CCMPR02133061 ERROR: (IMPSYC-179): add_power_switches cannot create nets with special character

CCMPR02131617 read_def -keepPinGeometry is moving a child pin

CCMPR02131170 **ERROR: (IMPTCM-18): 1000001 is not in the legal range of float values for value

CCMPR02130658 Changing write_lec_directory_naming_style has no effect where lec dofiles are created

CCMPR02130351 Issue with read_def merge causing incorrect display of nets from the merged def

CCMPR02130328 ccopt_design -cts -check_prerequisites changes the constraint status in clock tree debugger

CCMPR02129538 SEGV in the init stage

CCMPR02128964 routeDesign crash during track assignment

CCMPR02128718 Enhancement request: dump and load specific wires and vias of signal net

CCMPR02128501 place_opt_design incremental placement SEGV

CCMPR02128047 Bad command structure can crash tool (get_property)

CCMPR02127426 Tool is unable to trace scan chain and issues IMPSC-1001/1144/1117 warnings

CCMPR02127381 Incorrect virtual power domain created by INVS

CCMPR02126378 Need to obsolete create_inst_group/update_inst_group

CCMPR02126071 GUI and Violation Browser Show non-existent DRC violation

CCMPR02126011 extractRC abnormal exit - out of memory in prepare_for_route

CCMPR02125868 Innovus (NR) not fixing Via enclosure rule but violates

CCMPR02125180 NanoRotute crash in delay calculation

CCMPR02124425 saveNetlist exportTopPGNets needs to be made public and documented

CCMPR02124286 Nanoroute creates odd M1 shapes and violations when adding via pillars

CCMPR02123763 check_power_vias runs very slow in 19.11 compared to 18.14

CCMPR02123612 check_process_antenna missing real violations

CCMPR02122983 Ruler should snap to die boundary

CCMPR02122553 Why do we have IMPCCOPT-4209 and how avoid it?

CCMPR02122311 Derive Power/Ground connectivity during addIOFiller

CCMPR02121806 ecoDeleteRepeter crash

CCMPR02120405 Wrong layer due WARN IMPPTN-1802 issue in assign_io_pins is a mix of Legacy/CUI syntax

CCMPR02118995 Innovus DIAG error at hold timing calculation in the postroute stage

CCMPR02118862 Tool crashes for ecoCompareNetlist

CCMPR02118703 Block ring extension problem

CCMPR02118446 Innovus 19.10 is locking up during ccopt_design CUI

CCMPR02117133 After addfillers removing GNCs for power pin for ESD cells

CCMPR02116891 Fatal crash during place_opt_design with Innovus 19.11-e081_1

CCMPR02116746 IMPMSMV-1130 with fine grain ground switched memory power switch strategy

CCMPR02116535 SEGV in the post-CTS step

CCMPR02116042 Difference in the reporting of Density by timeDesign and checkPlace

CCMPR02116003 saveDesign is crashing at the floorplan stage

CCMPR02115927 checkPlace -noCheckPinAccess crashes randomly

CCMPR02115765 verify_drc crashes with SEGV at process_net_stack_via(bool)

CCMPR02115755 ERROR with tCIC DBLK.LUP rule check

CCMPR02114432 DIAG SetParentChange::CheckNoAssign NonFatalAssert Failed: Created assign state

CCMPR02114395 place_opt_deisgn crash when ILM and UPF used

CCMPR02113715 select_bump -net <netname> is not selecting the corresponding bumps

CCMPR02113637 SEGV in postCTS optimization

CCMPR02113118 Innovus import design

CCMPR02113111 Tool crash while running verify_drc

CCMPR02113099 QoR: need to align delete_buffer_tree command behavior with the one embedded in place_opt_design

CCMPR02112460 addFiller is taking more than a day over top-level

CCMPR02112273 addStripe does not drop PGvia and leaves one side of stripe dangling

CCMPR02112262 routeDesign hangs with setnanoRouteMode -droutePostRouteSpreadWire true

CCMPR02112205 sroute command is not creating VSS followpin routing between two macros

CCMPR02112162 Tool flagging false C4 WidthTable violations

CCMPR02111913 Voltus should handle ambiguous NDR and VIA definitions in Signal EM analysis

CCMPR02111887 EcoDeleteRepeater crashes

CCMPR02111265 Innovus is crashing during verify power via

CCMPR02111140 Third party tool not able to read oasis generated by Innvous

CCMPR02110683 SEGV during trackOpt

CCMPR02110266 Long runtime on first GUI query

CCMPR02109985 Innovus crashed in optimization during DrvOpt

CCMPR02109555 flexible htree blocked resource prediction not correct for multiple clocks

CCMPR02107420 NR leaving MUSTJOIN ports unconnected

CCMPR02106071 Bus term definition related warning (IMPOAX-684) should occur during init_design stage

CCMPR02106045 Innovus streamout is showing warning of 1 empty cell

CCMPR02104944 routeDesign fails with ERROR (NREX-87) Failed to read tech file

CCMPR02104685 Innovus crash in place_opt_design 18.13 CUI

CCMPR02103946 eco_oa_design gives error in 18.14

CCMPR02102523 Tool crashes during the optDesign -postCTS command

CCMPR02102357 Innovus is unable to generate DRC clean multicut power vias

CCMPR02102330 Power routing is not adding vias in 18.14-e070 and later

CCMPR02099500 place_opt_design hangs after issuing **WARN: (IMPSP-9089): Feature 'LEF ROWPATTERN' is obsolete

CCMPR02099431 Set unreasonable wire length causes weird behavior of tools

CCMPR02098915 verify_drc does not detect all out of die area routes due to rectilinear block shape

CCMPR02098242 Align man page/map options for write_multi_bit_flop_mapping_file

CCMPR02097739 QoR degradation

CCMPR02097616 NR fails to close M2 same mask spacing violation aroudn pin access area

CCMPR02097472 Innovus 171 routeDesign segmentation fault

CCMPR02096143 False checkPlace pin access violations

CCMPR02096071 CUI/Stylus bus msb/lsb seems reversed

CCMPR02095372 addFiller is adding DCAP cells with the same name twice

CCMPR02094830 Crash during routeDesign -trackOpt

CCMPR02094036 CUI equivalent of legacy command setNanoRouteMode -drouteCheckMarOnCellPin

CCMPR02094024 Via pillar creates min step violation

CCMPR02093499 ecoDeleteRepeater crashed

CCMPR02093385 Issues with output from command convert_legacy_to_common_ui

CCMPR02093320 addStripe failed to create M4 PG stripes cross the whole core area correctly

CCMPR02092585 saveDesign Error out with **ERROR: (IMPSYC-1919)**

CCMPR02091577 ccopt_design continues to leave transition violations

CCMPR02090467 streamOut -mode FILLONLY includes MAXVOLTAGE/MINVOLTAGE labels for routing (non-fill) shapes

CCMPR02089999 Innovus cannot recognize the power switch cells it has been inserted into the power domain

CCMPR02089402 Crash in delay calculation in optDesign -postRoute

CCMPR02088896 Add support for ccopt property extract_non_integrated_clock_gates in CUI

CCMPR02086023 GUI hang after gui_highlight gui_show

CCMPR02085825 Long runtime and great numbers of DRC in routing stage

CCMPR02084630 Unwanted layer demotion to DPT layer near source, causing EM violations

CCMPR02084341 Crash during ECO commands

CCMPR02082870 Constrained path reported as unconstrained

CCMPR02082577 clock-PRO not working on 1st level gaters (closest to root—) std cell libs

CCMPR02082146 18.14: place_opt_design with early clock flow SEGV

CCMPR02081702 Using sroute to connect pad pins together

CCMPR02080990 Via pillars create short with M1 cell blockage

CCMPR02080792 The field pin group is not updated automatically in pin editor

CCMPR02079541 partition command hangs for over 20 hours

CCMPR02079337 Tie cell addition fails for many pins after taking 15+ hours, keep on applying GNCs in loop

CCMPR02078459 summaryReport -outDir does not output all files into the specified outdir

CCMPR02078017 routePGPinUseSignalRoute is crashing during detailed route routing second Power Pins using multi-threading

CCMPR02077263 setTopCell command is crashing when invoked from GUI

CCMPR02077202 Incorrect mbit naming by Innovus

CCMPR02077010 Highlight of hinst is not working in floorplan view

CCMPR02076934 convert_lib_clock_tree_latencies creating unexpected values

CCMPR02076630 [saveDesign huge runtime

CCMPR02076471 partition command creates new PG pins

CCMPR02074300 ccopt_design hang during clustering

CCMPR02074069 addStripe causing segmentation fault when -power_domains is specified

CCMPR02073825 Innovus cannot interpret defined tcl var reference inside 1801 when the tcl var is set outside UPF unlike Genus/CLP

CCMPR02073717 Pin access analysis takes 7 hours in one cell

CCMPR02073380 delete_dangling_port introduce error IMPSYC-1919

CCMPR02073245 SEGV during route_secondary_pg_pins in timing_driven

CCMPR02072971 DIAG in connectPinT

CCMPR02072858 addStripe creates euclidean spacing violations to 45-degree edges of bumps

CCMPR02072849 verify_drc -view_window takes long runtime

CCMPR02072754 Missing VIA definition in DEF

CCMPR02072464 This switch -usePostCTSHighFanoutNetFixing is still leaving some HFN unfixed during postcts

CCMPR02072224 User gets repeatable stack trace when selecting an IO pad

CCMPR02072148 Innovus gui_highlight and get_layer_preference problems

CCMPR02071315 Enhancements requests for dbQuery

CCMPR02071129 Wire spreading causes lots of DRC in LEF58_EOLEXTENSIONSPACING

CCMPR02070851 PSW enable In/Out pin are not in always on power domain

CCMPR02070093 partition command takes ~30 minutes to finish for a single partition

CCMPR02069357 addRepeaterByRule is not buffering some nets

CCMPR02068105 Via pillars create short with M2 cell blockage

CCMPR02068020 UPF constructs for create_power_domain out of Innovus triggers 1801_REF_OBJ_REDEFINED: Power intent object has been previously defined

CCMPR02067997 Innovus route stage end up with many un-routed (open net)

CCMPR02067971 connect_global_net changes not persistent in output netlist

CCMPR02065812 setEdit -extend_to_bdry 1 is not properly mapped to setEditMode

CCMPR02065573 Crash in top-level postcts_hold (ilm design)

CCMPR02064937 Superfluous warnings in Innovus

CCMPR02064336 Issues when importing Virtuoso colors into Innovus

CCMPR02064190 verify_drc seg faults with 18.1x

CCMPR02063539 verify_drc reports Minimum cut violation with 0-cut required

CCMPR02063352 snapFPlan -all command moved the IO driver cells to some strange locations

CCMPR02062972 1801 produces error IMPDB-1207 when supply set is not fully defined before apply_power_model

CCMPR02062862 Long runtime of editDelete -net command

CCMPR02062520 tQuantus R and C values are off compared to Sign-off quantus

CCMPR02061899 Remove check on tapeOut mode and update DF-1043 message

CCMPR02061887 addStripe breaks stripe at selected even when -break_at set to none when power domains exist in design

CCMPR02061181 Request ability to toggle visibility of exceptpgnet style blockage separately from regular cell blockages

CCMPR02061038 Core dumped at ediPowerVia

CCMPR02060219 Huge runtime during macro checker

CCMPR02060125 update_power_vias does not respect via11 blockage over m10 block pins but does over m10 stripes

CCMPR02059140 Innovus fails to optimize critical IO group timing with high effort and weight

CCMPR02058873 Need to issue a warning message related to tech file error

CCMPR02058738 Innovus crashing during CTS when using nested fences and the dont_touch_hports attributes after issuing IMPCCOPT-4283

CCMPR02057772 DIAG during saveDesign

CCMPR02057589 NR/Swapping vias does not respect hard NDR spacing besides verify_drc cannot detect the errors

CCMPR02057549 create_clock_tree_spec output file has typo

CCMPR02057316 set_port_attributes UPF command does not work properly in Innovus for port buses

CCMPR02056738 Appending empty lef file list to init_lef_file causes saveDesign link every file in the current run dir

CCMPR02055819 18.1x: RouteDesign crashes

CCMPR02055314 Clean up of DIAG messages during preroute extraction due to missing vias in LEF

CCMPR02055104 add_gui_shape or addCustomBox no longer allows user to manually resize using GUI due to fail of setObjFPlanBox

CCMPR02055067 18.13-e070_1 and 18.14 set is_memory to true even for all std cells when voltage scaling lib set is loaded

CCMPR02054916 Correlation of Innovus DRC rules with Signoff rules Same Metal Aligned Cuts

CCMPR02054834 Huge amount of Clock ID degradation is observed during egrpc

CCMPR02054814 Enhancement to stop writing out ppcmd files from Innovus in CUI mode to the database with write_db

CCMPR02054161 Innovus shows random behavior in optDesign -postRoute -setup -hold, in one run crashes during hold optimization

CCMPR02054105 Crash during placeDesign command

CCMPR02053080 CTS crashing at clustering with 17.15 version

CCMPR02051254 check_ndr_spacing false reports violation when NDR is defined as HARDSPACING

CCMPR02051164 Guide Overlapping Fence causes illegal cell placement

CCMPR02050703 flexible htree image colormap change makes the data difficult to use

CCMPR02049947 NR is not updating the default power domain dimension after switching partition

CCMPR02049164 Request to remove escape character in instance name for create_inst -inst

CCMPR02048563 saveDesign -addtiming

CCMPR02048438 Enhance VL-321 message and make it a warning message

CCMPR02048374 setDesignMode -node S5 causes huge jump in eGR congestion

CCMPR02048344 Strange routeDesign -wireOpt behavior in 19.10 std cell libs

CCMPR02047048 streamOut: wrong min/max voltage text labels for 45 degree shapes

CCMPR02046325 Tran violations reported with report_constraint and reportTranViolation have mismatch in postRoute

CCMPR02046088 DIAG during create_timing_budget

CCMPR02045621 Horizontal max length violations are not being fixed by tool

CCMPR02045449 editPowerVia - same mask metal aligned cuts

CCMPR02045423 Innovus addVia skips some M4 pin to M5 power/ground stripe connections

CCMPR02045272 Floorplan file saved with saveDesign is missing area-IO instances

CCMPR02044551 Power via array generated with insufficient space between cuts

CCMPR02044445 WARNING (EXTGRMP-574): There are 8 unrouted nets

CCMPR02043631 Pin Editor GUI not giving all the edges in side/edge option

CCMPR02042506 add/check_metal_fill SEGV

CCMPR02041649 Placer needs to align placement of insts with M3 via pillars wrt M3 PG

CCMPR02041585 Timing Debugger generates hold data instead of setup data when timing_analysis_check_type is set to hold

CCMPR02041173 DRV degradation after ecoRoute in postRoute hold only flow

CCMPR02040993 **ERROR: (IMPESI-3201): Delay calculation failed for net and causing SEGV

CCMPR02040038 IQRC does not see physical connectivity between terminal wire segment (IMPEXT-1392)

CCMPR02039519 CCOPT SEGV during refine Place

CCMPR02039421 Enhancement for verify_drc report with separate NDR categories

CCMPR02038277 checkPlace issues pin access warnings and violations while router is able to route

CCMPR02038098 Pin legality issue causing PG shorts

CCMPR02036853 Labels do not move with the pins when pins are placed by placer

CCMPR02035155 saveTestcase to copy only the design lib used in OA based flow

CCMPR02034885 write_lef_library omits MINIMUMCUT rules if no via is defined

CCMPR02033663 Vague errors on reading the same CPF after free_power_intent

CCMPR02033400 verify_drc does not report violations between stripes and 45-degree bump shapes

CCMPR02033201 Innovus reporting false minstep violation

CCMPR02032030 Single cut/Multi cut via report in Innovus

CCMPR02030617 No way to halt flow if pin placement is illegal

CCMPR02029175 Improve PRO TAT on large designs

CCMPR02028928 Crash during opt_design -post_route

CCMPR02028652 optDesign -postRoute is crashing due to memory corruption

CCMPR02027822 report_path_group_options fails to report -early options

CCMPR02027247 Colorization of VIA1 incorrect during place_opt -place, can only properly be done with checkPlace -inst

CCMPR02025993 NRHF hangs setting up constraints

CCMPR02025887 Command 'reportCapViolation -all -min' is not detecting min cap violation on port

CCMPR02025200 Automatic via tuning at addStripe could avoid missing vias

CCMPR02024770 Disabling socv analysis causes IMPLIC-90 license error

CCMPR02023492 NDR violations on M5(6) for via_pillar

CCMPR02022789 sroute routes tielo/hi signal pins on IO instances

CCMPR02022275 Lingering stacked via/MAXCELLEXTENSION issues

CCMPR02021035 Enhancement for command read_timing_debug_report

CCMPR02020619 The createSdpGroup command does not keep the order of cells specified in the command line

CCMPR02018943 Support for apply_power_model -port_map to a constant

CCMPR02016517 Lack of DRV fixing on top level with INVS 18.11 (unexpected behavior of spGetBoxDemandAndSupply)

CCMPR02014427 Add new object type pinShape in dbGet

CCMPR02012103 ERROR: (IMPVL-325) in ILM flow when an abstract (LEF) of a submodule is available

CCMPR02011414 Improve eGR runtime on large designs

CCMPR02008454 tQuantus w/virtual metal fill 15% optimistic on key nets vs QRC

CCMPR02007256 placeopt runtime is 56 hours on 3.5M block

CCMPR02004466 Command eco_design to support -lef_files option

CCMPR01998922 place_opt_design should filter out the delay cells automatically

CCMPR01995934 color highlight in other command does not work when we mix select commands

CCMPR01988788 Innovus fixes 300K max_trans in 25 hrs, and it hangs for 18 hours for 1st round fix, without increment info

CCMPR01973883 assembleDesign causes pWires to teleport to negative x-space

CCMPR01973806 dbQuery does not detect bump cell all times

CCMPR01972186 MAR on fixed VIA when route_eco

CCMPR01962428 Virtuoso registry file out-of-sync with other Cadence tools

CCMPR01951373 Crash with sroute without stack trace

CCMPR01932175 CCOpt run time degradation due to timing graph updates

CCMPR01906406 Native commands should accept get_db location output without requiring additional user processing

CCMPR01889342 verifyPowerVia command is flagging missing vias where cell blockage located

CCMPR01859285 Stacktrace during writing timing model

CCMPR01758160 dbiSnapCoordToTrackCmd ptnSnapCoordToTrack API is not snapping to next Mask1 rather than nearest track

CCMPR01540224 oasisOut does not allow to merge GDS files, streamOut does not allow oasis files

CCMPR01451111 Provide option to suppress flightline display inside partitions

May 07, 2020

CCMPR02213338 oasisOut broken in 19.13

CCMPR02210511 SEGV in clkPRO

CCMPR02207769 Internal error messages during optDesign at PRO stage

CCMPR02202724 ecoRoute not able to fix M1 DRC that can be fixed manually

CCMPR02201772 Preferred layer effort on clock nets not honored during ccopt_design V2

CCMPR02199590 saveDesign crash in 19.13-e033_1 (during saving pin access .apa file)

CCMPR02197202 SEGV observed during saveDesign

CCMPR02196641 tquantus signature flow hangs on top level design

CCMPR02195393 verifyPowerDomain -aoBufferType returns unwanted information

CCMPR02195093 Mixed placer places all HB with R90 orientation, although R90 R270 is allowed

CCMPR02194146 refine_macro_place hang

CCMPR02193823 Crash while running Floorplan tag

CCMPR02192205 fix_floorplan creates a rectangular routing blockage over a rectilinear shape

CCMPR02192195 SEGV observed during synthesize_ccopt_flexible_htrees

CCMPR02192020 SEGV during clock detail routing with 19.11

CCMPR02191939 Innovus crash during layer assignment due to route_design_top_routing_layer -1

CCMPR02191937 check_tracks crash due to route_design_top_routing_layer -1

CCMPR02191827 SEGV when compressedPGDB

CCMPR02190458 time_design shows more max_tran violations than report_constraints

CCMPR02189957 Memory jump during area/power/drv/setup Reclaim of place_opt_design

CCMPR02187977 verify_drc SEGV on IO Block

CCMPR02187892 place_opt_design crashes

CCMPR02186949 Innovus Timing Path Analyzer - Path SDC reports wrong SDC

CCMPR02186533 tQuantus extraction with compressed PG very slow

CCMPR02186528 SEGV during route_design

CCMPR02186365 addRepeaterByRule hangs

CCMPR02185337 saveDesign crashing in 18.16-e018_1

CCMPR02184701 Running flow tool Innovus crash at route

CCMPR02184668 Crash while running build_db target

CCMPR02183510 Add warning about not honoring user ggrid size setting if it will cause overflow

CCMPR02183022 Tool hangs at PRO hold stage during timing analysis

CCMPR02182632 optDesign -postRoute is crashing while clock DRV fixing

CCMPR02182538 prects segv: lsUsefulSkewToolboxCL.cpp dumpSDCInfoForDisabledViews

CCMPR02182076 Via Pillar leaves avoidable EndofLine SameMask spacing violations in-between

CCMPR02181237 checkplace does not report a strict point touch violation in the presence of placement blockage

CCMPR02181038 CTS routing Struck due to Memory Corrupted Error

CCMPR02180598 add_stripes causes DRCs by choosing the wrong VIA model

CCMPR02180502 Divider flop D pin balancing in CTS

CCMPR02179953 setAddStripeMode -keep_pitch_after_snap false is a part of PG script and cannot be converted to common UI

CCMPR02179239 Cannot create stripe with width upper that design height when design is thin

CCMPR02178155 Preferred layer effort on Clock nets not honored during ccopt_design

CCMPR02178143 Placement blockages shifted with createPlaceBlockage -boxList

CCMPR02178078 write_stream issues sub-block during GDSII export at top level not done

CCMPR02177656 saveDesign crashes in dbsSaveDesignSymbolTable::getPGTermId after deleteInst of TAP cells

CCMPR02177466 ecoRoute Scalability Statistics table is missing components

CCMPR02177350 route_secondary_pg_pins runtime degradation 18.14 vs 19.12

CCMPR02176589 routePGAsSignalRoute routed to lower layers after removing BottomRoutingLayer 4 and using preferred layer attribute

CCMPR02176537 Type fills routing blockage is not properly handled by verify_drc and verifyGeomentry commands

CCMPR02176194 Secondary PG high resistance problem

CCMPR02175736 Error when trying to run optDesign -postRoute -targeted -incr

CCMPR02175576 add_well_taps_insert_cells not accounting for last well_tap to boundary check

CCMPR02175545 set_flowkit_write_db_args does not accept new write_db options

CCMPR02175212 Innovus 19.11 got crash at sroute

CCMPR02175180 Innovus tool crashes during refinePlace

CCMPR02174968 write_multi_bit_flop_mapping_file needs to be able to direct output to a location

CCMPR02174964 gui_bind_key command sourced through GUI Menu tab is causing error IMPQTF-4044

CCMPR02174278 sroute do not create followpin connection for powerNet defined as bus

CCMPR02174256 Routing QOR is much degraded in 18.1x as compared to 17.1x

CCMPR02174227 powerVia enclosure does not match stripe width

CCMPR02173977 Another unspecifyIlm crash when ILM and UPF is used

CCMPR02173882 unflattenIlm crashed with 19.11 and 19.12

CCMPR02173861 Placeopt job is stuck while executing the place_opt_design command

CCMPR02173108 write_lef_library dumps out integer 0 for MINSPANLENGTH instead of 0.000

CCMPR02173067 M3 pins are not aligned with the tracks

CCMPR02172322 SEGV user defined attribute with set function

CCMPR02169916 The oaPurpose argument in add_text command does not work

CCMPR02169688 Empty '+ PORT' statements in DEF after delete_obj $thePortShapes

CCMPR02169625 clock_design runaway memory consumption during reducing clock tree power

CCMPR02169420 Innovus 19.11 got crash with place_opt_design -opt

CCMPR02167674 ecoDesign does not appear to read previously saved metrics and hence not appending to previous metrics

CCMPR02167436 During iSpatial flow in genus, Innovus terminated by SEGV while reading timing constraints

CCMPR02167335 Huge run Time during globalDetailRoute at detail pin access analysis

CCMPR02167209 setobjFPlanPolygon command to give warning/error message to improve usability

CCMPR02166582 Need method in verify_drc to ignore or override cell density checks

CCMPR02166218 globalDetailRoute runtime is too high for top level

CCMPR02166025 colorizeGeometry within placeDesign takes close to 5hrs

CCMPR02165892 Blocking issue for optDesign -trackOpt: tQuantus fails because of wrong auto mapping file while iQuantus runs fine

CCMPR02165496 Chip Top Stripegen Run time increases in P3 compared to P2

CCMPR02165436 CreateRow/initCoreRow creates rows outside core area

CCMPR02164744 addStackingVia on nets with NDR attribute fail with no Via Connection

CCMPR02164631 set_ideal_net crashes with DPO list

CCMPR02164462 route_flip_chip causes DRCs due to wrong way routing

CCMPR02164016 defIn/defOut runtime and memory issue

CCMPR02163872 Stack trace during clock_design

CCMPR02163206 route_special does not route over some endcaps

CCMPR02163202 oasisOut properties missing in 19.1*

CCMPR02162910 Innovus is not fixing Hold violations due to the fake congestion it's seeing during PRO step

CCMPR02162759 globalNetConnect does not report any errors/warning even though those pins does not exist

CCMPR02161151 Different pin placement results with assign_pins_edit_in_batch true vs false

CCMPR02160560 19.11/19.12 not inserting level shifters, UPF was working in 18.14/18.15

CCMPR02160518 Innovus 19.11 SEGV when I try to close a Kit menu

CCMPR02159270 Flattening connects wires of local power nets together

CCMPR02159151 Block crashes during ccopt_design in 19.12-e030_1 version

CCMPR02158986 The routeDesign -viaOpt fails to change single-cut to Multi-cut via

CCMPR02158869 editPowerVia to avoid using stack via

CCMPR02158434 Chip Top Run time increases in P3 compared to P2 for all Floorpaln flow Nodes

CCMPR02158243 timing_enable_multi_threaded_reporting set at false by route_design

CCMPR02157856 Zero Spacing OBS on non-orthogonal cut layer is showing false spacing violations

CCMPR02157708 editPowerVia -split_long_via is inconsistent in dropping PG vias in multiple rows

CCMPR02157331 Innovus did not keep terminals locations when creating a new logical Hierarchy

CCMPR02156819 Add jog_connect -layer option to move wire drop-down menu

CCMPR02156802 Miscorrelation between the EditMode setting and the GUI window

CCMPR02155959 gui_highlight - instant crash with invalid pattern

CCMPR02155957 Innovus is getting stuck at globalDetailRoute during Generating timing data

CCMPR02155385 Crash during routeDesign

CCMPR02153771 Innovus is getting crashed while running 'addWellTap'

CCMPR02153463 False VT violations reported by Innovus

CCMPR02151053 Innovus placeSpareModule command crash

CCMPR02150717 Nets with preferred bottom layer = 12 routed on 4 and router does not connect to top of via pillar stack

CCMPR02150607 Loading floorplan file in restoreDesign with design that was properly saved results in error IMPFP-707

CCMPR02150427 fix_ufc not following the macro profile when cutting ROWS around a multi-linear macro

CCMPR02150367 Massive number of IMPSP-5225 messages causing terabytes of log even when message_limit is 20

CCMPR02150268 unspecifyIlm crash when ILM and UPF used

CCMPR02149897 False parallel run length spacing in Innovus

CCMPR02149012 Flop merging left dangling instances in netlist that are not removed

CCMPR02148290 add_fillers corrupting y_flip_type

CCMPR02147778 editPowerVia long runtime

CCMPR02147686 fcroute length matching using the constraint file

CCMPR02147045 Right mouse click on cell obstruction results in SEGV

CCMPR02146910 ecoAddRepeater is crashing with hinstGuide option

CCMPR02146651 selectSecondaryPGNet issues when secondary PG has two pin shapes

CCMPR02146297 Setting opt_fix_hold_allow_setup_tns_degradation option to true is degrading Setup WNS during postCTS hold fix

CCMPR02146294 Innovus SEGV during write_db

CCMPR02145977 Tool is crashing during the ecoRoute step in Innovus

CCMPR02145497 ccopt_design long runtime in clustering

CCMPR02145489 Bug in error message IMPOPT-7027

CCMPR02145382 report_hidden_usage hangs, no return

CCMPR02143882 High DRC count seen with binary when run on UHD libs

CCMPR02143374 Innovus crash (seg fault) when attempting to overwrite existing OA library

CCMPR02143352 19.12 breaks scan chains during MBFF merge/split

CCMPR02143189 New Command to support sizing up/Down the bus bit

CCMPR02143110 MergeHierDef drops the pin shape of the block if RDL's DEF presented and caused I/O net to be skipped in signal EM analysis

CCMPR02143008 synthesize_ccopt_flexible_htrees hang

CCMPR02142308 addStripe hangs

CCMPR02142230 Innovus leaving many DRCs after routeDesign on a CTS DB

CCMPR02141093 Fatal error out during restore partition design.

CCMPR02140636 restoreDesign removing GNCs of secondary pgPin of cells when saved design executed with the globalNetConnect command

CCMPR02140403 saveDesign crash at postcts when ILM and UPF is used

CCMPR02139508 ecoRoute crash. Customer is in the eco phase and need quick help.

CCMPR02139269 add_io buffers takes long time to flip the inst to match row orientation

CCMPR02138981 restoreDesign hangs

CCMPR02138735 NR leaves partially open net in 19.1/19.2 but routes cleanly in 18.1

CCMPR02136378 Innovus read Virtuoso OA DB got wrong instance coordinate transform

CCMPR02136321 eco_pnr stage crashes during ecoRoute

CCMPR02135600 saveDesign crash while saving route file

CCMPR02134426 placeObject crashes when placement blockage is copied from GUI using copy button equivalent to uisetTool copy

CCMPR02133981 A proc with a foreach with a try/trap that is false, crashes 19.1 Innovus Legacy

CCMPR02133766 Innovus is crashing during postRoute OptDesign with internal (SEGV) error/signal

CCMPR02133363 ccopt places clock buffers where it is impossible to route the stacked vias cleanly

CCMPR02133061 ERROR: (IMPSYC-179): add_power_switches cannot create nets with special character

CCMPR02131617 read_def -keepPinGeometry is moving a child pin

CCMPR02131170 **ERROR: (IMPTCM-18): 1000001 is not in the legal range of float values for value

CCMPR02130658 Changing write_lec_directory_naming_style has no effect where lec dofiles are created

CCMPR02130351 Issue with read_def merge causing incorrect display of nets from the merged def

CCMPR02130328 ccopt_design -cts -check_prerequisites changes the constraint status in clock tree debugger

CCMPR02129538 SEGV in the init stage

CCMPR02128964 routeDesign crash during track assignment

CCMPR02128718 Enhancement request: dump and load specific wires and vias of signal net

CCMPR02128501 place_opt_design incremental placement SEGV

CCMPR02128047 Bad command structure can crash tool (get_property)

CCMPR02127426 Tool is unable to trace scan chain and issues IMPSC-1001/1144/1117 warnings

CCMPR02127381 Incorrect virtual power domain created by INVS

CCMPR02126378 Need to obsolete create_inst_group/update_inst_group

CCMPR02126071 GUI and Violation Browser Show non-existent DRC violation

CCMPR02126011 extractRC abnormal exit - out of memory in prepare_for_route

CCMPR02125868 Innovus (NR) not fixing Via enclosure rule but violates

CCMPR02125180 NanoRotute crash in delay calculation

CCMPR02124425 saveNetlist exportTopPGNets needs to be made public and documented

CCMPR02124286 Nanoroute creates odd M1 shapes and violations when adding via pillars

CCMPR02123763 check_power_vias runs very slow in 19.11 compared to 18.14

CCMPR02123612 check_process_antenna missing real violations

CCMPR02122983 Ruler should snap to die boundary

CCMPR02122553 Why do we have IMPCCOPT-4209 and how avoid it?

CCMPR02122311 Derive Power/Ground connectivity during addIOFiller

CCMPR02121806 ecoDeleteRepeter crash

CCMPR02120405 Wrong layer due WARN IMPPTN-1802 issue in assign_io_pins is a mix of Legacy/CUI syntax

CCMPR02118995 Innovus DIAG error at hold timing calculation in the postroute stage

CCMPR02118862 Tool crashes for ecoCompareNetlist

CCMPR02118703 Block ring extension problem

CCMPR02118446 Innovus 19.10 is locking up during ccopt_design CUI

CCMPR02117133 After addfillers removing GNCs for power pin for ESD cells

CCMPR02116891 Fatal crash during place_opt_design with Innovus 19.11-e081_1

CCMPR02116746 IMPMSMV-1130 with fine grain ground switched memory power switch strategy

CCMPR02116535 SEGV in the post-CTS step

CCMPR02116042 Difference in the reporting of Density by timeDesign and checkPlace

CCMPR02116003 saveDesign is crashing at the floorplan stage

CCMPR02115927 checkPlace -noCheckPinAccess crashes randomly

CCMPR02115765 verify_drc crashes with SEGV at process_net_stack_via(bool)

CCMPR02115755 ERROR with tCIC DBLK.LUP rule check

CCMPR02114432 DIAG SetParentChange::CheckNoAssign NonFatalAssert Failed: Created assign state

CCMPR02114395 place_opt_deisgn crash when ILM and UPF used

CCMPR02113715 select_bump -net <netname> is not selecting the corresponding bumps

CCMPR02113637 SEGV in postCTS optimization

CCMPR02113118 Innovus import design

CCMPR02113111 Tool crash while running verify_drc

CCMPR02113099 QoR: need to align delete_buffer_tree command behavior with the one embedded in place_opt_design

CCMPR02112460 addFiller is taking more than a day over top-level

CCMPR02112273 addStripe does not drop PGvia and leaves one side of stripe dangling

CCMPR02112262 routeDesign hangs with setnanoRouteMode -droutePostRouteSpreadWire true

CCMPR02112205 sroute command is not creating VSS followpin routing between two macros

CCMPR02112162 Tool flagging false C4 WidthTable violations

CCMPR02111913 Voltus should handle ambiguous NDR and VIA definitions in Signal EM analysis

CCMPR02111887 EcoDeleteRepeater crashes

CCMPR02111265 Innovus is crashing during verify power via

CCMPR02111140 Third party tool not able to read oasis generated by Innvous

CCMPR02110683 SEGV during trackOpt

CCMPR02110266 Long runtime on first GUI query

CCMPR02109985 Innovus crashed in optimization during DrvOpt

CCMPR02109555 flexible htree blocked resource prediction not correct for multiple clocks

CCMPR02107420 NR leaving MUSTJOIN ports unconnected

CCMPR02106071 Bus term definition related warning (IMPOAX-684) should occur during init_design stage

CCMPR02106045 Innovus streamout is showing warning of 1 empty cell

CCMPR02104944 routeDesign fails with ERROR (NREX-87) Failed to read tech file

CCMPR02104685 Innovus crash in place_opt_design 18.13 CUI

CCMPR02103946 eco_oa_design gives error in 18.14

CCMPR02102523 Tool crashes during the optDesign -postCTS command

CCMPR02102357 Innovus is unable to generate DRC clean multicut power vias

CCMPR02102330 Power routing is not adding vias in 18.14-e070 and later

CCMPR02099500 place_opt_design hangs after issuing **WARN: (IMPSP-9089): Feature 'LEF ROWPATTERN' is obsolete

CCMPR02099431 Set unreasonable wire length causes weird behavior of tools

CCMPR02098915 verify_drc does not detect all out of die area routes due to rectilinear block shape

CCMPR02098242 Align man page/map options for write_multi_bit_flop_mapping_file

CCMPR02097739 QoR degradation

CCMPR02097616 NR fails to close M2 same mask spacing violation aroudn pin access area

CCMPR02097472 Innovus 171 routeDesign segmentation fault

CCMPR02096143 False checkPlace pin access violations

CCMPR02096071 CUI/Stylus bus msb/lsb seems reversed

CCMPR02095372 addFiller is adding DCAP cells with the same name twice

CCMPR02094830 Crash during routeDesign -trackOpt

CCMPR02094036 CUI equivalent of legacy command setNanoRouteMode -drouteCheckMarOnCellPin

CCMPR02094024 Via pillar creates min step violation

CCMPR02093499 ecoDeleteRepeater crashed

CCMPR02093385 Issues with output from command convert_legacy_to_common_ui

CCMPR02093320 addStripe failed to create M4 PG stripes cross the whole core area correctly

CCMPR02092585 saveDesign Error out with **ERROR: (IMPSYC-1919)**

CCMPR02091577 ccopt_design continues to leave transition violations

CCMPR02090467 streamOut -mode FILLONLY includes MAXVOLTAGE/MINVOLTAGE labels for routing (non-fill) shapes

CCMPR02089999 Innovus cannot recognize the power switch cells it has been inserted into the power domain

CCMPR02089402 Crash in delay calculation in optDesign -postRoute

CCMPR02088896 Add support for ccopt property extract_non_integrated_clock_gates in CUI

CCMPR02086023 GUI hang after gui_highlight gui_show

CCMPR02085825 Long runtime and great numbers of DRC in routing stage

CCMPR02084630 Unwanted layer demotion to DPT layer near source, causing EM violations

CCMPR02084341 Crash during ECO commands

CCMPR02082870 Constrained path reported as unconstrained

CCMPR02082577 clock-PRO not working on 1st level gaters (closest to root—) std cell libs

CCMPR02082146 18.14: place_opt_design with early clock flow SEGV

CCMPR02081702 Using sroute to connect pad pins together

CCMPR02080990 Via pillars create short with M1 cell blockage

CCMPR02080792 The field pin group is not updated automatically in pin editor

CCMPR02079541 partition command hangs for over 20 hours

CCMPR02079337 Tie cell addition fails for many pins after taking 15+ hours, keep on applying GNCs in loop

CCMPR02078459 summaryReport -outDir does not output all files into the specified outdir

CCMPR02078017 routePGPinUseSignalRoute is crashing during detailed route routing second Power Pins using multi-threading

CCMPR02077263 setTopCell command is crashing when invoked from GUI

CCMPR02077202 Incorrect mbit naming by Innovus

CCMPR02077010 Highlight of hinst is not working in floorplan view

CCMPR02076934 convert_lib_clock_tree_latencies creating unexpected values

CCMPR02076630 [saveDesign huge runtime

CCMPR02076471 partition command creates new PG pins

CCMPR02074300 ccopt_design hang during clustering

CCMPR02074069 addStripe causing segmentation fault when -power_domains is specified

CCMPR02073825 Innovus cannot interpret defined tcl var reference inside 1801 when the tcl var is set outside UPF unlike Genus/CLP

CCMPR02073717 Pin access analysis takes 7 hours in one cell

CCMPR02073380 delete_dangling_port introduce error IMPSYC-1919

CCMPR02073245 SEGV during route_secondary_pg_pins in timing_driven

CCMPR02072971 DIAG in connectPinT

CCMPR02072858 addStripe creates euclidean spacing violations to 45-degree edges of bumps

CCMPR02072849 verify_drc -view_window takes long runtime

CCMPR02072754 Missing VIA definition in DEF

CCMPR02072464 This switch -usePostCTSHighFanoutNetFixing is still leaving some HFN unfixed during postcts

CCMPR02072224 User gets repeatable stack trace when selecting an IO pad

CCMPR02072148 Innovus gui_highlight and get_layer_preference problems

CCMPR02071315 Enhancements requests for dbQuery

CCMPR02071129 Wire spreading causes lots of DRC in LEF58_EOLEXTENSIONSPACING

CCMPR02070851 PSW enable In/Out pin are not in always on power domain

CCMPR02070093 partition command takes ~30 minutes to finish for a single partition

CCMPR02069357 addRepeaterByRule is not buffering some nets

CCMPR02068105 Via pillars create short with M2 cell blockage

CCMPR02068020 UPF constructs for create_power_domain out of Innovus triggers 1801_REF_OBJ_REDEFINED: Power intent object has been previously defined

CCMPR02067997 Innovus route stage end up with many un-routed (open net)

CCMPR02067971 connect_global_net changes not persistent in output netlist

CCMPR02065812 setEdit -extend_to_bdry 1 is not properly mapped to setEditMode

CCMPR02065573 Crash in top-level postcts_hold (ilm design)

CCMPR02064937 Superfluous warnings in Innovus

CCMPR02064336 Issues when importing Virtuoso colors into Innovus

CCMPR02064190 verify_drc seg faults with 18.1x

CCMPR02063539 verify_drc reports Minimum cut violation with 0-cut required

CCMPR02063352 snapFPlan -all command moved the IO driver cells to some strange locations

CCMPR02062972 1801 produces error IMPDB-1207 when supply set is not fully defined before apply_power_model

CCMPR02062862 Long runtime of editDelete -net command

CCMPR02062520 tQuantus R and C values are off compared to Sign-off quantus

CCMPR02061899 Remove check on tapeOut mode and update DF-1043 message

CCMPR02061887 addStripe breaks stripe at selected even when -break_at set to none when power domains exist in design

CCMPR02061181 Request ability to toggle visibility of exceptpgnet style blockage separately from regular cell blockages

CCMPR02061038 Core dumped at ediPowerVia

CCMPR02060219 Huge runtime during macro checker

CCMPR02060125 update_power_vias does not respect via11 blockage over m10 block pins but does over m10 stripes

CCMPR02059140 Innovus fails to optimize critical IO group timing with high effort and weight

CCMPR02058873 Need to issue a warning message related to tech file error

CCMPR02058738 Innovus crashing during CTS when using nested fences and the dont_touch_hports attributes after issuing IMPCCOPT-4283

CCMPR02057772 DIAG during saveDesign

CCMPR02057589 NR/Swapping vias does not respect hard NDR spacing besides verify_drc cannot detect the errors

CCMPR02057549 create_clock_tree_spec output file has typo

CCMPR02057316 set_port_attributes UPF command does not work properly in Innovus for port buses

CCMPR02056738 Appending empty lef file list to init_lef_file causes saveDesign link every file in the current run dir

CCMPR02055819 18.1x: RouteDesign crashes

CCMPR02055314 Clean up of DIAG messages during preroute extraction due to missing vias in LEF

CCMPR02055104 add_gui_shape or addCustomBox no longer allows user to manually resize using GUI due to fail of setObjFPlanBox

CCMPR02055067 18.13-e070_1 and 18.14 set is_memory to true even for all std cells when voltage scaling lib set is loaded

CCMPR02054916 Correlation of Innovus DRC rules with Signoff rules Same Metal Aligned Cuts

CCMPR02054834 Huge amount of Clock ID degradation is observed during egrpc

CCMPR02054814 Enhancement to stop writing out ppcmd files from Innovus in CUI mode to the database with write_db

CCMPR02054161 Innovus shows random behavior in optDesign -postRoute -setup -hold, in one run crashes during hold optimization

CCMPR02054105 Crash during placeDesign command

CCMPR02053080 CTS crashing at clustering with 17.15 version

CCMPR02051254 check_ndr_spacing false reports violation when NDR is defined as HARDSPACING

CCMPR02051164 Guide Overlapping Fence causes illegal cell placement

CCMPR02050703 flexible htree image colormap change makes the data difficult to use

CCMPR02049947 NR is not updating the default power domain dimension after switching partition

CCMPR02049164 Request to remove escape character in instance name for create_inst -inst

CCMPR02048563 saveDesign -addtiming

CCMPR02048438 Enhance VL-321 message and make it a warning message

CCMPR02048374 setDesignMode -node S5 causes huge jump in eGR congestion

CCMPR02048344 Strange routeDesign -wireOpt behavior in 19.10 std cell libs

CCMPR02047048 streamOut: wrong min/max voltage text labels for 45 degree shapes

CCMPR02046325 Tran violations reported with report_constraint and reportTranViolation have mismatch in postRoute

CCMPR02046088 DIAG during create_timing_budget

CCMPR02045621 Horizontal max length violations are not being fixed by tool

CCMPR02045449 editPowerVia - same mask metal aligned cuts

CCMPR02045423 Innovus addVia skips some M4 pin to M5 power/ground stripe connections

CCMPR02045272 Floorplan file saved with saveDesign is missing area-IO instances

CCMPR02044551 Power via array generated with insufficient space between cuts

CCMPR02044445 WARNING (EXTGRMP-574): There are 8 unrouted nets

CCMPR02043631 Pin Editor GUI not giving all the edges in side/edge option

CCMPR02042506 add/check_metal_fill SEGV

CCMPR02041649 Placer needs to align placement of insts with M3 via pillars wrt M3 PG

CCMPR02041585 Timing Debugger generates hold data instead of setup data when timing_analysis_check_type is set to hold

CCMPR02041173 DRV degradation after ecoRoute in postRoute hold only flow

CCMPR02040993 **ERROR: (IMPESI-3201): Delay calculation failed for net and causing SEGV

CCMPR02040038 IQRC does not see physical connectivity between terminal wire segment (IMPEXT-1392)

CCMPR02039519 CCOPT SEGV during refine Place

CCMPR02039421 Enhancement for verify_drc report with separate NDR categories

CCMPR02038277 checkPlace issues pin access warnings and violations while router is able to route

CCMPR02038098 Pin legality issue causing PG shorts

CCMPR02036853 Labels do not move with the pins when pins are placed by placer

CCMPR02035155 saveTestcase to copy only the design lib used in OA based flow

CCMPR02034885 write_lef_library omits MINIMUMCUT rules if no via is defined

CCMPR02033663 Vague errors on reading the same CPF after free_power_intent

CCMPR02033400 verify_drc does not report violations between stripes and 45-degree bump shapes

CCMPR02033201 Innovus reporting false minstep violation

CCMPR02032030 Single cut/Multi cut via report in Innovus

CCMPR02030617 No way to halt flow if pin placement is illegal

CCMPR02029175 Improve PRO TAT on large designs

CCMPR02028928 Crash during opt_design -post_route

CCMPR02028652 optDesign -postRoute is crashing due to memory corruption

CCMPR02027822 report_path_group_options fails to report -early options

CCMPR02027247 Colorization of VIA1 incorrect during place_opt -place, can only properly be done with checkPlace -inst

CCMPR02025993 NRHF hangs setting up constraints

CCMPR02025887 Command 'reportCapViolation -all -min' is not detecting min cap violation on port

CCMPR02025200 Automatic via tuning at addStripe could avoid missing vias

CCMPR02024770 Disabling socv analysis causes IMPLIC-90 license error

CCMPR02023492 NDR violations on M5(6) for via_pillar

CCMPR02022789 sroute routes tielo/hi signal pins on IO instances

CCMPR02022275 Lingering stacked via/MAXCELLEXTENSION issues

CCMPR02021035 Enhancement for command read_timing_debug_report

CCMPR02020619 The createSdpGroup command does not keep the order of cells specified in the command line

CCMPR02018943 Support for apply_power_model -port_map to a constant

CCMPR02016517 Lack of DRV fixing on top level with INVS 18.11 (unexpected behavior of spGetBoxDemandAndSupply)

CCMPR02014427 Add new object type pinShape in dbGet

CCMPR02012103 ERROR: (IMPVL-325) in ILM flow when an abstract (LEF) of a submodule is available

CCMPR02011414 Improve eGR runtime on large designs

CCMPR02008454 tQuantus w/virtual metal fill 15% optimistic on key nets vs QRC

CCMPR02007256 placeopt runtime is 56 hours on 3.5M block

CCMPR02004466 Command eco_design to support -lef_files option

CCMPR01998922 place_opt_design should filter out the delay cells automatically

CCMPR01995934 color highlight in other command does not work when we mix select commands

CCMPR01988788 Innovus fixes 300K max_trans in 25 hrs, and it hangs for 18 hours for 1st round fix, without increment info

CCMPR01973883 assembleDesign causes pWires to teleport to negative x-space

CCMPR01973806 dbQuery does not detect bump cell all times

CCMPR01972186 MAR on fixed VIA when route_eco

CCMPR01962428 Virtuoso registry file out-of-sync with other Cadence tools

CCMPR01951373 Crash with sroute without stack trace

CCMPR01932175 CCOpt run time degradation due to timing graph updates

CCMPR01906406 Native commands should accept get_db location output without requiring additional user processing

CCMPR01889342 verifyPowerVia command is flagging missing vias where cell blockage located

CCMPR01859285 Stacktrace during writing timing model

CCMPR01758160 dbiSnapCoordToTrackCmd ptnSnapCoordToTrack API is not snapping to next Mask1 rather than nearest track

CCMPR01540224 oasisOut does not allow to merge GDS files, streamOut does not allow oasis files

CCMPR01451111 Provide option to suppress flightline display inside partitions

May 07, 2020

The Cadence Innovus Implementation System is optimized for the most challenging designs, as well as the latest FinFET 16nm, 14nm, 7nm, and 5nm processes, helping you get an earlier design start with a faster ramp-up. With unique new capabilities in placement, optimization, routing, and clocking, the Innovus system features an architecture that accounts for upstream and downstream steps and effects in the design flow. This architecture minimizes design iterations and provides the runtime boost you’ll need to get to market faster. Using the Innovus system, you’ll be equipped to build integrated, differentiated systems with less risk.

The Innovus system features a variety of key capabilities. Its massively parallel architecture can handle large designs and take advantage of multi-threading on multi-core workstations, as well as distributed processing over networks of computers.

Based on the well-established NanoRoute engine, next-generation slack and power-driven routing with track-aware timing optimization addresses signal integrity early on and improves post-route correlation. The Innovus system includes full-flow multi-objective technology, which makes concurrent electrical and physical optimization possible. It also shares a customizable flow via a common UI and user commands with synthesis and signoff tools. As a result, you can take advantage of robust reporting and visualization, improving your design efficiency and productivity across the whole digital flow.

With block sizes growing in both cell count and complexity, the number of macros that need to be positioned in the floorplan is exploding. The Innovus system offers mixed-macro and standard-cell placement, which enables macro locations to be automatically generated, reducing the time to create an optimal floorplan from days to hours.

The latest advances in machine learning computer science are very relevant for digital implementation flows. The Innovus system incorporates machine learning technology to deliver the best PPA for the most challenging, high-performance blocks. The designer has complete control over the machine learning training, to ensure it is customized for their specific design requirements.

Cadence’s Genus Synthesis Solution is tightly integrated with the Innovus system, which enables a seamless move from RTL synthesis to implementation. With shared placement and optimization technology from the GigaPlace and GigaOpt engines for Genus physical synthesis, this offers a big benefit for advanced-node design convergence.

As voltage decreases in the latest FinFET process nodes, IR and EM constraints become increasingly important. The Innovus system includes comprehensive power integrity-aware placement, optimization, clock tree, and routing features to ensure IR and EM violations are addressed during implementation without impacting final PPA.

Cadence’s Tempus Timing Signoff Solution, Quantus Extraction Solution, and Voltus IC Power Integrity Solution are integrated with the Innovus system. With this integration, you can accurately model parasitics, timing, signal, and power integrity effects at the early stage of physical implementation, and achieve faster convergence on these electrical metrics, resulting in more efficient design closure.

Place and Route in Cadence Innovus

Complete flow of innovus tool has been demonstrated in this video. Both command line and GUI mode have been covered in the same video. Important input files for this flow has also been discussed and how to create them has been explained.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

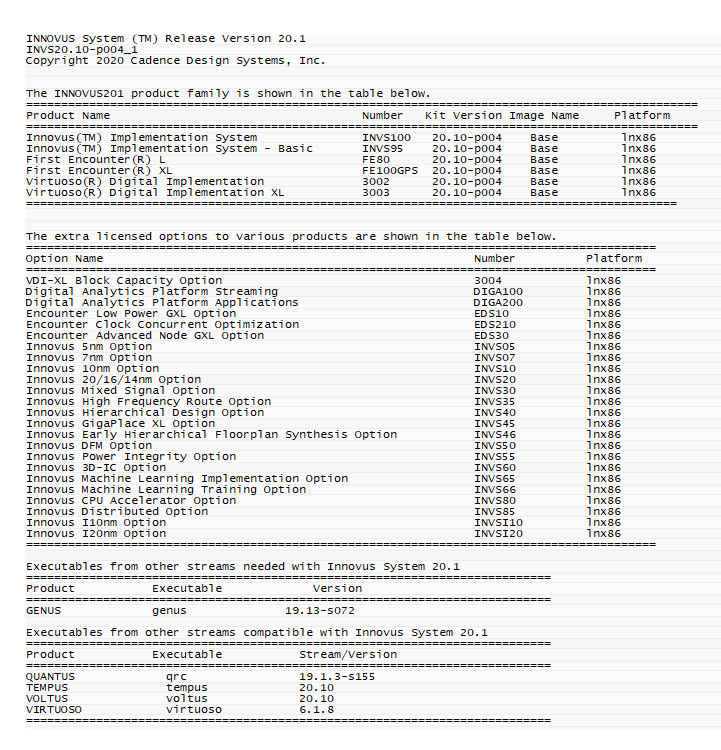

Product: Cadence INNOVUS

Version: 21.10.000 (INVS20.10-p004_1) Base release *

Supported Architectures: x86

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: RHEL 6 (lnx86)

Size: 5.8 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please