Cadence INNOVUS version 19.13.000 (ISR3) | 4.8 Gb

Cadence Design Systems, Inc. , the leader in global electronic design innovation, has unveiled INNOVUS 19.13.000 (ISR3) is part of the broader Cadence digital and signoff suite, which provides customers with an integrated full flow, delivering a predictable path to design closure and also supports Cadence’s Intelligent System Design strategy, accelerating SoC design excellence.

What's New in This Release

CCMPR02196454 Tool crash at place stage

CCMPR02196045 Tool is crashing during track assignment while running globalDetailRoute

CCMPR02195873 create_stack_via_rules writes association file in the legacy format which errors out while reading in CUI flow

CCMPR02195468 optDesign crash (in Reclaim via pillar)

CCMPR02195446 RX diffusion max-length rule leaves fillGap violations

CCMPR02195250 ecoAddRepeater issue: ERROR: (IMPOPT-7222): Cannot insert buffer legally in hierarchy

CCMPR02194449 Many X1 trim spacing violation after viaOpt

CCMPR02194150 dbQuery is 25x slower in 19.71-e102 compared to 19.71-e060

CCMPR02194079 Innovus crashes while doing defIn

CCMPR02193113 read_physical -add_oa_ref_libs is exiting Innovus shell abruptly when trying to read libs incrementally

CCMPR02192903 Need to solve trim to trim violation by trim color flipping

CCMPR02192195 SEGV observed during synthesize_ccopt_flexible_htrees

CCMPR02192020 SEGV during clock detail routing with 19.11

CCMPR02191827 SEGV when compressed PGDB

CCMPR02190492 Many IMPSP-2031 in high utilization:- From PA Checking

CCMPR02189417 Block becomes off placement grid when assembled

CCMPR02189378 push_down_network crashes when switch cell SLEEP pin is tied low

CCMPR02189343 Secondary PG via coloring issue when num_cpu > 1

CCMPR02188847 saveDesign crashed after ecoDeleteRepeater

CCMPR02188787 SEGV in CTE API during route

CCMPR02187901 Crash in checkPlace

CCMPR02187892 place_opt_design crashes

CCMPR02187757 SEGV in CCOpt without stack trace

CCMPR02187577 refine_macro_place hangs with set_macro_place_constraint -same_length_site 10

CCMPR02187355 place_opt_design long runtime when enabling pin-based uncertainty (divergence Modeling)

CCMPR02187183 Innovus crashes (SEGV) with reading AOCV tables

CCMPR02187143 Top category CTS nets are using lower layers other than rule specified

CCMPR02186365 addRepeaterByRule hangs

CCMPR02185913 Genus ispatial SEGV error @set_trim_grid_group()

CCMPR02185337 saveDesign crashing in 18.16-e018_1

CCMPR02185192 reportPinDensityMap hanging

CCMPR02185143 CCOPT SEGV

CCMPR02184857 ERROR (IMPSYUTIL-96): Cannot open (for read) symbol table file. The reason is “No such file or directory”

CCMPR02184668 Crash while running build_db target

CCMPR02184610 report_ccopt_cell_halo_violations does not use real shape of rectilinear blocks

CCMPR02184595 Need to fix V0 enclosure with OBS patching having length limitation

CCMPR02184580 NRHF routes bus nets shorting PG vias and pins

CCMPR02184469 Crash during saveDesign after ECOs

CCMPR02184055 Crash during delay calculation within prects optimization

CCMPR02183516 NanoRoute flags false Nut Wire violations on M11-M12 vias

CCMPR02183285 Tempus ECO time_design_signoff errors out during LEF reading

CCMPR02183184 Crash reported in saveDesign at the ECO stage

CCMPR02183057 signoffOptDesign -setup core dump crash

CCMPR02183011 QRC random fail when it was called in specific Innovus version with the setDistributeHost setting

CCMPR02182813 Non-colored trim cut connected by OBS shape

CCMPR02182330 eGR congestion map cannot reflect NR real situation on PSH cells

CCMPR02182200 DB crash

CCMPR02182141 Missing violation X2 trim to trim spacing

CCMPR02182110 ILM pin connectivity is not displayed in the Design Browser

CCMPR02182076 Via Pillar leaves avoidable EndofLine SameMask spacing violations in-between

CCMPR02181948 Seen crash during postRoute Hold Opt

CCMPR02181464 ccopt_design SEGV for design w/ dont_touch on clock gates

CCMPR02181448 19.71 to issue WARN for hardmacro-only PD and should not stop the flow with error

CCMPR02181354 Loading a DB aborts if the user does not have access to QRC file

CCMPR02181038 CTS routing stuck due to Memory Corrupted error

CCMPR02181007 ESD results GUI missing in Innovus 19.11

CCMPR02180609 Mismatch connectivity between hierarchical and flat verilog netlist

CCMPR02180598 add_stripes causes DRCs by choosing the wrong VIA model

CCMPR02180538 Tool exiting with segmentation fault error

CCMPR02180502 Divider flop D pin balancing in CTS

CCMPR02180248 place_opt_design crash in timing calculation

CCMPR02180147 Clock NDR wire at top of via pillar not put on NDR track

CCMPR02180130 Timing gap between, before, and after the path regrouping

CCMPR02180072 Hang in addEndCap

CCMPR02180055 ecoChangeCell is unable to swap cells even with the similar functionalities

CCMPR02180043 Removing unnecessary trim cut

CCMPR02180019 900K DIAGs just before end of validation step

CCMPR02179990 ECF to support long path removal to avoid large pushouts

CCMPR02179953 setAddStripeMode -keep_pitch_after_snap false cannot be converted to common UI

CCMPR02179951 eco_split_flop is missing -full_split option whereas legacy ecoSplitFlop -fullSplit exists. Please support in CUI

CCMPR02179827 optPower improves power but degrades timing severely

CCMPR02179574 PG generation is leaving M3 cut spacing violations over macros

CCMPR02179482 Excessive TAT during "Start Fix Iteration …" step with eco route

CCMPR02179468 Support for 1801 find_object -regexp

CCMPR02179418 RefinePlace is moving the cells instead of coloring for DPT violations and causing QOR degradation

CCMPR02179351 More than 54 MASTERSLICE layers causes editPowerVia SEGV

CCMPR02179239 Cannot create stripe with width upper that design height when design is thin

CCMPR02179236 set_db design_third_party_compatible true triggers GLOBAL-100 and IMPDBTCL-321

CCMPR02179224 checkPlace reports false violations for RX layers

CCMPR02179106 Max fanout violation after optDesign -preCTS done

CCMPR02178883 Missing violation during trim color flipping

CCMPR02178846 Switching power degradation seen after global place

CCMPR02178837 report_scan_chain crash

CCMPR02178682 streamOut wrong mask number

CCMPR02178672 NR runtime too long

CCMPR02178365 Crash during ccopt_design -cts

CCMPR02178258 saveNetlist with -flattenBus option is erroring out for bit blasted netlist

CCMPR02178249 SEGV during post route opt

CCMPR02178155 Preferred layer effort on clock nets not honored during ccopt_design

CCMPR02178143 Placement blockages shifted with createPlaceBlockage -boxList

CCMPR02177803 QOR is degraded with enabling CRR in postRouteOpt

CCMPR02177678 ccopt target_max_trans property does not propagate to new created clock of flexHtree

CCMPR02177656 saveDesign crashes in dbsSaveDesignSymbolTable::getPGTermId after deleteInst of TAP cells

CCMPR02177515 Timing degrade when turn on some high performance cells in optDesign -postcts stage

CCMPR02177466 ecoRoute Scalability Statistics table is missing components

CCMPR02177350 route_secondary_pg_pins runtime degradation 18.14 vs 19.12

CCMPR02177302 Multi-Driver clock crash

CCMPR02177274 Refined state output UPF produces linter error when read into the common linter

CCMPR02177186 DIAG when place_opt_design with ECF

CCMPR02176589 routePGAsSignalRoute routed to lower layers after removing BottomRoutingLayer 4 and using preferred layer attribute

CCMPR02176537 Type fills routing blockage is not properly handled by 'verify_drc' and 'verifyGeomentry' commands

CCMPR02176369 Consistent crash of chip top hierarchical design partition command

CCMPR02176314 Mechine Learning got crash during routDesign stage

CCMPR02176259 nanoRoute and check_drc are reporting false spacing violations

CCMPR02176134 SEGV when doing create_module_model -type "flexilm" which has "ilm" child block

CCMPR02176025 signoffOptdesign -power crashes with SEGV

CCMPR02175576 add_well_taps_insert_cells not accounting for last well_tap to boundary check

CCMPR02175545 set_flowkit_write_db_args does not accept new write_db options

CCMPR02175212 Innovus 19.11 got crash at sroute

CCMPR02174968 write_multi_bit_flop_mapping_file needs to be able to direct output to a location

CCMPR02174964 The gui_bind_key command sourced through GUI Menu tab is causing ERROR IMPQTF-4044

CCMPR02174442 Innovus GUI is extremely slow

CCMPR02174410 clearGlobalNet hangs

CCMPR02174307 Tool not traversing hierarchy with set_scope

CCMPR02174278 sroute does not create followpin connection for powerNet defined as bus

CCMPR02174256 Routing QOR is much degraded in 18.1x as compared to 17.1x

CCMPR02174227 powerVia enclosure does not match stripe width

CCMPR02174134 Crash in Innovus during Place run

CCMPR02174026 synthesize_ccopt_flexible_htrees SEGV with -sinks existing sink pins

CCMPR02173892 optDesign leaving hold violations due to DRV degradation

CCMPR02173882 unflattenIlm crashed with 19.11 and 19.12

CCMPR02173861 Placeopt job is stuck while executing the place_opt_design command

CCMPR02173569 eGR correlation

CCMPR02173108 write_lef_library dumps out integer 0 for MINSPANLENGTH instead of 0.000

CCMPR02173067 M3 pins are not aligned with the tracks

CCMPR02172910 fcroute unable to route bumps outside rectilinear die area (using srouteFcDieAreaOffset)

CCMPR02172613 routeDesign leaving lot of M1 patches/trims and causing thousands of DRCs

CCMPR02172313 Many DIAG messages showed in placement related to spiPadSwapInstAreaTechSite

CCMPR02171927 Innovus cannot detect V0 spacing violation when cell is defined as OBS

CCMPR02171863 What is correct usage of setAddStripeMode -preventive_color_opt <true

CCMPR02171832 Feedthrough topology GUI is not working for feedthrough net with primary input port as the driver

CCMPR02171144 MBFF mapping dropping instances in 19.71-e084

CCMPR02171106 Data integrity check failures in detail route after rolling in third party ECO

CCMPR02170487 Same-Metal-Aligned-Cut violations with M2 pin extensions

CCMPR02170243 OptDesign coeSetupOptimizerIteration::executeSingleIteration crash in INVS during Genus iSpatial

CCMPR02170115 commit_power_intent is taking more time and consuming more memory

CCMPR02169987 Fatal ERROR message as SHDB flow, (IMPSE-110): cannot read "::Rda_CDTV::ilmDataInfo(ram_128x16_test,currTag)"

CCMPR02169634 Mixed Placer continues without necessary license error

CCMPR02169449 Innovus is hanging during place_opt_design

CCMPR02169420 Innovus 19.11 got crash with place_opt_design -opt

CCMPR02169292 addStripe got SEGV in 19.1

CCMPR02169028 delete_clock_tree_repeaters preserving hpin during our Htree flow

CCMPR02168919 postCTS hangs

CCMPR02168541 Innovus GUI shows issue with displaying backside via

CCMPR02168536 ECO rolling in takes huge run time

CCMPR02168514 Over 500K lines of "#Off-grid fixed wire is found" in "Merging special wires" for FlexH clock tree routing

CCMPR02168174 Hierarchical UPF file has wrong supply net association

CCMPR02167804 Std M3-pin is not aligned with the routing track

CCMPR02167755 Blocking issue for optDesign -trackOpt: tQuantus fails because of wrong auto mapping file while iQuantus runs fine

CCMPR02167674 ecoDesign does not appear to read previously saved metrics and hence not appending to previous metrics

CCMPR02167588 addFiller added instances in the wrong power domain

CCMPR02167551 Innovus error on power state group in

CCMPR02167209 setobjFPlanPolygon command to give warning/error message to improve usability

CCMPR02166974 Detours and bad qor on NDR nets

CCMPR02166959 tQuantus too optimistic (tcap by 2.3%, xcap by 6.2%)

CCMPR02166958 dbGet top.insts.name crashes with long instance name

CCMPR02166951 Innovus is getting crashed at route_opt stage on optDesign -postRoute -setup

CCMPR02166627 Mismatch between iQuantus and signoff Quantus

CCMPR02166596 create_power_domain -update creates incorrect ::MSV_UPF value

CCMPR02166583 Crash seen during place_opt_design

CCMPR02166582 Need a method in verify_drc to ignore or override cell density checks

CCMPR02166578 Scan reorder caused LP violations - Reorder ISO cells

CCMPR02166547 Enhancement request to provide new setting for "set_db route_design_process_node i5"

CCMPR02166420 M1 variant pin connection by EEQ function

CCMPR02166218 globalDetailRoute runtime is too high for top level

CCMPR02166149 addRepeaterByRule deletes wires when routing alongRoute from ports to std cell pins

CCMPR02166124 It takes a lot of time in routeDesign -trackOpt in Innovus 19.12_e040.

CCMPR02166067 Place opt design is auto pruning scenarios

CCMPR02166043 addRepeaterByRule to add odd inverter options

CCMPR02166009 Update to latest 1801 linter 19.10-d317

CCMPR02165933 routeDesign -viaPillarOpt deletes all the signal nets if preceded by ecoRoute -fix_drc

CCMPR02165892 Blocking issue for optDesign -trackOpt: tQuantus fails because of wrong auto mapping file while iQuantus runs fine

CCMPR02165805 Crash at CTS during via pillar insertion (versions: 18.16 and 19.12)

CCMPR02165634 ecoRoute -fix_drc crashed

CCMPR02165496 Run time increases in P3 compared to P2

CCMPR02165232 SEGV during addEndCap

CCMPR02164864 Error messages reported during place_opt_design and the design crashes later in the flow

CCMPR02164708 Delay calculation hangs in optDesign

CCMPR02164701 Auto via generation not generating optimal vias for NDR rule

CCMPR02164666 Support 80pitch triplet via rule

CCMPR02164631 set_ideal_net crashes with DPO list

CCMPR02164613 NDR rule being dropped in db reload

CCMPR02164064 pgInstTerm dropping connectivity on 19.71 but not 18.71

CCMPR02164016 defIn/defOut runtime and memory issue

CCMPR02163963 addFiller leaving 1X gaps next to BUFX1 cells

CCMPR02163872 Stack trace during clock_design

CCMPR02163369 MAXLENGTH on ENCLOSURETABLE is not detected by Innovus

CCMPR02163204 Write out text label for the pin to the center of polygon pin shape

CCMPR02163202 oasisOut properties missing in 19.1*

CCMPR02162802 Enclosure false violation

CCMPR02162757 S8 eGR fix with S8V2 switch making design un-routable

CCMPR02162561 Core ccopt_design leaving lot of DRVs. Looks like DRV is NOT being called after the Area reclaim step

CCMPR02161974 optDesign -postCTS -setup crash

CCMPR02161773 Out of memory during trackopt

CCMPR02161705 5% of difference between Tqrc and SignoffQRC

CCMPR02161466 unspecifyIlm SEGV

CCMPR02161322 Critical- Placement Run crashed even with high memory usage

CCMPR02161079 With -use_point2point_router true, addStripe switches layer to connect M7Z padpin with useless M6Z jogs

CCMPR02160753 signoffOptDesign is introducing double pattern violations

CCMPR02160646 SEGV during add_port_driver within ccopt_design

CCMPR02160638 Crash during placeopt_design during area reclaim optimization

CCMPR02160600 Enhancement to add_stripe behavior around trim blockages

CCMPR02160560 19.11/19.12 not inserting level shifters, UPF was working in 18.14/18.15

CCMPR02160518 Innovus 19.11 SEGV when I try to close a Kit menu

CCMPR02160256 Crash at optDesign -postRoute

CCMPR02160052 Sub optimal logic placement leading to high WNS during PLACE

CCMPR02159831 postCTS opt is erroring out during clock pin alignment in Innovus 19.42-e007

CCMPR02159426 saveNetlist -onlyLeafCell -includePowerGround crashes with SEGV

CCMPR02159270 Flattening connects wires of local power nets together

CCMPR02159244 routeAndBufferBusSinkGroup does not honor bus guide for bus (WAR NRCR-27) in 19.12 while it does in 18.14s088

CCMPR02159063 Tquantus does not take in account FILLWIREOPC shape

CCMPR02159006 Excessive IMPSP-2031 during CTS

CCMPR02158986 The routeDesign -viaOpt fails to change single-cut to Multi-cut via

CCMPR02158869 editPowerVia to avoid using stack via

CCMPR02158525 place_connected is taking long runtime (about 4Hr) with padding on all flops

CCMPR02158243 timing_enable_multi_threaded_reporting set at false by route_design

CCMPR02157774 findBestRoiImprovingMove - ResynthesizeIslandGenus CRR based crash during iSpatial

CCMPR02157708 editPowerVia -split_long_via is inconsistent in dropping PG vias in multiple rows

CCMPR02157331 Innovus did not keep terminals locations when creating a new logical Hierarchy

CCMPR02157005 Incremental ICG Alignment in postcts disrupts ICG placement

CCMPR02156978 route_opt_design improvement

CCMPR02156925 Enabling cell usage during skewClock

CCMPR02156882 Segmentation fault crash while exiting Innovus

CCMPR02156819 Add -jog_connect_layer option to move wire drop-down menu

CCMPR02156342 DPT pin shapes loosing mask after assemble design

CCMPR02155605 Nanoroute places NDR via at top of via pillar on non-NDR track

CCMPR02155555 ecoRoute with 19.71-e073 build failed in dirty-map dbsDASaved::checkInsts

CCMPR02155432 FloorPlan with setFPlanMode -rowSiteWidth odd do not adjust core box

CCMPR02154981 LEF58_SPACING - SAMENET ADJACENTCUTS reports false violation

CCMPR02154751 editPint -fixOverlap does not fix the overlap pin

CCMPR02154673 createSignalPin promoting floating pins of an RLM to pgTerms

CCMPR02153812 nanoRoute SEGV during antenna fixing iteration

CCMPR02153463 False VT violations reported by Innovus

CCMPR02152840 Dynamic pin cap cal report is different between ccopt and CTS

CCMPR02152500 Hold Fixing failing to fix nets because of internal reason: SuccessiveFailureLimit

CCMPR02152185 Enhance request of report_ccopt_clock_tree_structure

CCMPR02151928 ERROR out while fixing tCIC

CCMPR02151150 Design with 45-degree RDL routing elicits IMPEXT-7081 and hangs during extraction

CCMPR02150568 Bus Planning - addRepeaterByRule -busMode to support fanout greater than one

CCMPR02150427 fix_ufc not following the macro profile when cutting ROWS around a multi-linear macro

CCMPR02150367 Massive number of IMPSP-5225 messages causing terabytes of log even when message_limit is 20

CCMPR02149897 False parallel run length spacing in Innovus

CCMPR02149876 Difference in utilization when using actual value and dbGet density

CCMPR02149863 Specified via pillar order is reversed by the tool

CCMPR02149845 Native multi-driver flow not working

CCMPR02149068 routeDesign -viaPillarOpt changes existing via pillar to via that does not meet pitch rule

CCMPR02148711 report_ccopt_clock_trees -summary does not show the number of explicit ignore pins

CCMPR02148590 addPowerSwitch command runtime issue

CCMPR02148290 add_fillers corrupting y_flip_type

CCMPR02147778 editPowerVia long runtime

CCMPR02147686 fcroute length matching using the constraint file

CCMPR02147041 Missed skewing opportunities in skewClock

CCMPR02147011 Enable support for opt cell groups to restrict cell usage to specified limits in IPO

CCMPR02143189 Enhancement new command to support sizing up/down the bus bit

CCMPR02142212 Enhance add_stripe to stop stripes on trim grid shapes

CCMPR02141705 Qualcomm: Zigzag CTS routing

CCMPR02139984 Support 1801 set_retention_elements

CCMPR02139899 ENCLOSUREEDGE rule not seen by checkPlace/refinePlace

CCMPR02139269 add_io buffers takes long time to flip the inst to match row orientation

CCMPR02139222 No Qor improvement seen with LOADCAP cells compared to baseline in routeopt

CCMPR02139111 addFiller creating DPT violations

CCMPR02138735 NR leaves partially open net in 19.1/19.2 but routes cleanly in 18.1

CCMPR02138466 Scan reordering not preserving scan ports when reorder_scan_keep_hinst_port_name is set

CCMPR02138276 addStripe SEGV in 19.11

CCMPR02138218 fix_ufc should be able to fix the violation

CCMPR02137817 Create via form has incorrect cutclass

CCMPR02137721 addPowerSwitch option -offsetReferencePoint core not using core boundary as reference point

CCMPR02137711 Enhancement for selected default power domain

CCMPR02137359 Pruned view is not recovering timing at preCTS in ECF flow

CCMPR02136002 verify_drc reports false ENCLOSUREEDGE violations randomly

CCMPR02135123 -ignore_clock_latency does not consider input delay in in2reg path

CCMPR02135118 fanout of 1 timing path is detouring during placement

CCMPR02134855 pgFill to fix isolated via adds vias which cause Same Metal Aligned Cuts violations

CCMPR02134217 sroute does not connect VSS stripes to the nearest VSS pins

CCMPR02133061 ERROR: (IMPSYC-179): add_power_switches cannot create nets with special character

CCMPR02128832 Crash seen during delay calculation at clock_post_route_repair step on routed DB

CCMPR02128501 ECF place_opt_design incremental placement SEGV

CCMPR02127382 cleanup_floorplan_for_macro_place dumping thousands of "dbshape" commands to logfile

CCMPR02125868 Innovus (NR) not fixing Via enclosure rule "VIAya.EN.16.10" but violates

CCMPR02124529 CTS routes excessively on lower DPT layers and leaves M1 DRCs

CCMPR02124501 editPowerVia added vias in spite of *any angle* Pump OBS on RV via layer

CCMPR02123725 Require a filler flow compatible with X1 Cut requirements

CCMPR02123029 Placement issue with MCP

CCMPR02122525 PostRoute timeDesign crash

CCMPR02122322 Multi Bit Splitting not happening during Placement

CCMPR02120446 eGR to support complex via rule handling with a user option

CCMPR02118388 Pin guide in guide gives IMPPTN-499 errors despite plenty of room in guides

CCMPR02118362 Replace via form should show the via currently selected

CCMPR02116222 routeDesign error out with NRDR-5 message

CCMPR02115337 Power reclaim degrades hold TNS at postroute

CCMPR02114111 replaceBlock command to correctly reflect db with macro lef pins changes

CCMPR02113118 Innovus import design

CCMPR02112162 Tool flagging false C4 WidthTable violations

CCMPR02111595 optDesign -postRoute adding redundant buffers and not upsizing short cells

CCMPR02110293 ccopt_design -cts routes in unusual zigzag pattern

CCMPR02109468 Command place_clones reports incorrect reason for clonePlace failed

CCMPR02108597 SDP place creates unwanted auto_sdp groups and degrades QOR

CCMPR02107523 Enhancement request to specify NSWidth targets during placement/optimization

CCMPR02106710 false violations on PARALLELRUNLENGTH/TWOWIDTH spacing table

CCMPR02101433 Clock constraint getting dropped at very next pin where it is defined

CCMPR02098856 read_physical is missing -incremental option for reading OA libs

CCMPR02097739 QoR degradation

CCMPR02096143 False checkPlace pin access violations

CCMPR02095696 TNS improvement seen during scanReorder is not retained after scanReorder

CCMPR02090335 TDGR layer promotion review

CCMPR02084630 Unwanted layer demotion to DPT layer near source, causing EM violations

CCMPR02080807 streamOut generate wrong GDS

CCMPR02079971 QoR changes in CCOPT with VP rule LEF due to different NRDR clock nets routing results

CCMPR02079855 How optimal is buffering

CCMPR02078813 Support 1801 refined state

CCMPR02064322 NR is unable to route design clean though congestion is low

CCMPR02063346 181/191: Change **WARN: (IMPILM-349): set_db ilm_keep_async false … to *Info : set_db ilm_keep_async fa

CCMPR02062115 Significantly high MBFF flop merging runtime on pd_msr_sys

CCMPR02054434 Innovus ERRORs out while executing command eco_add_repeater. Msg: **ERROR: (IMPOPT-7222):

CCMPR02053644 Clock route jogging on preferred routing layers

CCMPR02048019 trimMetalFillNearNet -createFillBlockage does not take care of the via

CCMPR02039421 Enhancement for verify_drc report with separate NDR categories

CCMPR02032793 User variable changes value after save_design

CCMPR02025711 Improve the congestion and DRCs at the corner of macro

CCMPR02021035 Enhancement for command read_timing_debug_report

CCMPR02018238 Fishbone clock routing required to minimize/balance ICG connectivity

CCMPR02010528 addStripe -over_power_domain 1 does not generate stripes on the domain boundary

CCMPR01979491 fixACLimitViolation not fixing simple violations

CCMPR01973883 assembleDesign causes pWires to teleport to negative x-space

CCMPR01968419 Controlled RCs for skewing

CCMPR01948826 ctd_trace is way too slow

CCMPR01906406 Native commands should accept get_db "location" output without requiring additional user processing

CCMPR02196045 Tool is crashing during track assignment while running globalDetailRoute

CCMPR02195873 create_stack_via_rules writes association file in the legacy format which errors out while reading in CUI flow

CCMPR02195468 optDesign crash (in Reclaim via pillar)

CCMPR02195446 RX diffusion max-length rule leaves fillGap violations

CCMPR02195250 ecoAddRepeater issue: ERROR: (IMPOPT-7222): Cannot insert buffer legally in hierarchy

CCMPR02194449 Many X1 trim spacing violation after viaOpt

CCMPR02194150 dbQuery is 25x slower in 19.71-e102 compared to 19.71-e060

CCMPR02194079 Innovus crashes while doing defIn

CCMPR02193113 read_physical -add_oa_ref_libs is exiting Innovus shell abruptly when trying to read libs incrementally

CCMPR02192903 Need to solve trim to trim violation by trim color flipping

CCMPR02192195 SEGV observed during synthesize_ccopt_flexible_htrees

CCMPR02192020 SEGV during clock detail routing with 19.11

CCMPR02191827 SEGV when compressed PGDB

CCMPR02190492 Many IMPSP-2031 in high utilization:- From PA Checking

CCMPR02189417 Block becomes off placement grid when assembled

CCMPR02189378 push_down_network crashes when switch cell SLEEP pin is tied low

CCMPR02189343 Secondary PG via coloring issue when num_cpu > 1

CCMPR02188847 saveDesign crashed after ecoDeleteRepeater

CCMPR02188787 SEGV in CTE API during route

CCMPR02187901 Crash in checkPlace

CCMPR02187892 place_opt_design crashes

CCMPR02187757 SEGV in CCOpt without stack trace

CCMPR02187577 refine_macro_place hangs with set_macro_place_constraint -same_length_site 10

CCMPR02187355 place_opt_design long runtime when enabling pin-based uncertainty (divergence Modeling)

CCMPR02187183 Innovus crashes (SEGV) with reading AOCV tables

CCMPR02187143 Top category CTS nets are using lower layers other than rule specified

CCMPR02186365 addRepeaterByRule hangs

CCMPR02185913 Genus ispatial SEGV error @set_trim_grid_group()

CCMPR02185337 saveDesign crashing in 18.16-e018_1

CCMPR02185192 reportPinDensityMap hanging

CCMPR02185143 CCOPT SEGV

CCMPR02184857 ERROR (IMPSYUTIL-96): Cannot open (for read) symbol table file. The reason is “No such file or directory”

CCMPR02184668 Crash while running build_db target

CCMPR02184610 report_ccopt_cell_halo_violations does not use real shape of rectilinear blocks

CCMPR02184595 Need to fix V0 enclosure with OBS patching having length limitation

CCMPR02184580 NRHF routes bus nets shorting PG vias and pins

CCMPR02184469 Crash during saveDesign after ECOs

CCMPR02184055 Crash during delay calculation within prects optimization

CCMPR02183516 NanoRoute flags false Nut Wire violations on M11-M12 vias

CCMPR02183285 Tempus ECO time_design_signoff errors out during LEF reading

CCMPR02183184 Crash reported in saveDesign at the ECO stage

CCMPR02183057 signoffOptDesign -setup core dump crash

CCMPR02183011 QRC random fail when it was called in specific Innovus version with the setDistributeHost setting

CCMPR02182813 Non-colored trim cut connected by OBS shape

CCMPR02182330 eGR congestion map cannot reflect NR real situation on PSH cells

CCMPR02182200 DB crash

CCMPR02182141 Missing violation X2 trim to trim spacing

CCMPR02182110 ILM pin connectivity is not displayed in the Design Browser

CCMPR02182076 Via Pillar leaves avoidable EndofLine SameMask spacing violations in-between

CCMPR02181948 Seen crash during postRoute Hold Opt

CCMPR02181464 ccopt_design SEGV for design w/ dont_touch on clock gates

CCMPR02181448 19.71 to issue WARN for hardmacro-only PD and should not stop the flow with error

CCMPR02181354 Loading a DB aborts if the user does not have access to QRC file

CCMPR02181038 CTS routing stuck due to Memory Corrupted error

CCMPR02181007 ESD results GUI missing in Innovus 19.11

CCMPR02180609 Mismatch connectivity between hierarchical and flat verilog netlist

CCMPR02180598 add_stripes causes DRCs by choosing the wrong VIA model

CCMPR02180538 Tool exiting with segmentation fault error

CCMPR02180502 Divider flop D pin balancing in CTS

CCMPR02180248 place_opt_design crash in timing calculation

CCMPR02180147 Clock NDR wire at top of via pillar not put on NDR track

CCMPR02180130 Timing gap between, before, and after the path regrouping

CCMPR02180072 Hang in addEndCap

CCMPR02180055 ecoChangeCell is unable to swap cells even with the similar functionalities

CCMPR02180043 Removing unnecessary trim cut

CCMPR02180019 900K DIAGs just before end of validation step

CCMPR02179990 ECF to support long path removal to avoid large pushouts

CCMPR02179953 setAddStripeMode -keep_pitch_after_snap false cannot be converted to common UI

CCMPR02179951 eco_split_flop is missing -full_split option whereas legacy ecoSplitFlop -fullSplit exists. Please support in CUI

CCMPR02179827 optPower improves power but degrades timing severely

CCMPR02179574 PG generation is leaving M3 cut spacing violations over macros

CCMPR02179482 Excessive TAT during "Start Fix Iteration …" step with eco route

CCMPR02179468 Support for 1801 find_object -regexp

CCMPR02179418 RefinePlace is moving the cells instead of coloring for DPT violations and causing QOR degradation

CCMPR02179351 More than 54 MASTERSLICE layers causes editPowerVia SEGV

CCMPR02179239 Cannot create stripe with width upper that design height when design is thin

CCMPR02179236 set_db design_third_party_compatible true triggers GLOBAL-100 and IMPDBTCL-321

CCMPR02179224 checkPlace reports false violations for RX layers

CCMPR02179106 Max fanout violation after optDesign -preCTS done

CCMPR02178883 Missing violation during trim color flipping

CCMPR02178846 Switching power degradation seen after global place

CCMPR02178837 report_scan_chain crash

CCMPR02178682 streamOut wrong mask number

CCMPR02178672 NR runtime too long

CCMPR02178365 Crash during ccopt_design -cts

CCMPR02178258 saveNetlist with -flattenBus option is erroring out for bit blasted netlist

CCMPR02178249 SEGV during post route opt

CCMPR02178155 Preferred layer effort on clock nets not honored during ccopt_design

CCMPR02178143 Placement blockages shifted with createPlaceBlockage -boxList

CCMPR02177803 QOR is degraded with enabling CRR in postRouteOpt

CCMPR02177678 ccopt target_max_trans property does not propagate to new created clock of flexHtree

CCMPR02177656 saveDesign crashes in dbsSaveDesignSymbolTable::getPGTermId after deleteInst of TAP cells

CCMPR02177515 Timing degrade when turn on some high performance cells in optDesign -postcts stage

CCMPR02177466 ecoRoute Scalability Statistics table is missing components

CCMPR02177350 route_secondary_pg_pins runtime degradation 18.14 vs 19.12

CCMPR02177302 Multi-Driver clock crash

CCMPR02177274 Refined state output UPF produces linter error when read into the common linter

CCMPR02177186 DIAG when place_opt_design with ECF

CCMPR02176589 routePGAsSignalRoute routed to lower layers after removing BottomRoutingLayer 4 and using preferred layer attribute

CCMPR02176537 Type fills routing blockage is not properly handled by 'verify_drc' and 'verifyGeomentry' commands

CCMPR02176369 Consistent crash of chip top hierarchical design partition command

CCMPR02176314 Mechine Learning got crash during routDesign stage

CCMPR02176259 nanoRoute and check_drc are reporting false spacing violations

CCMPR02176134 SEGV when doing create_module_model -type "flexilm" which has "ilm" child block

CCMPR02176025 signoffOptdesign -power crashes with SEGV

CCMPR02175576 add_well_taps_insert_cells not accounting for last well_tap to boundary check

CCMPR02175545 set_flowkit_write_db_args does not accept new write_db options

CCMPR02175212 Innovus 19.11 got crash at sroute

CCMPR02174968 write_multi_bit_flop_mapping_file needs to be able to direct output to a location

CCMPR02174964 The gui_bind_key command sourced through GUI Menu tab is causing ERROR IMPQTF-4044

CCMPR02174442 Innovus GUI is extremely slow

CCMPR02174410 clearGlobalNet hangs

CCMPR02174307 Tool not traversing hierarchy with set_scope

CCMPR02174278 sroute does not create followpin connection for powerNet defined as bus

CCMPR02174256 Routing QOR is much degraded in 18.1x as compared to 17.1x

CCMPR02174227 powerVia enclosure does not match stripe width

CCMPR02174134 Crash in Innovus during Place run

CCMPR02174026 synthesize_ccopt_flexible_htrees SEGV with -sinks existing sink pins

CCMPR02173892 optDesign leaving hold violations due to DRV degradation

CCMPR02173882 unflattenIlm crashed with 19.11 and 19.12

CCMPR02173861 Placeopt job is stuck while executing the place_opt_design command

CCMPR02173569 eGR correlation

CCMPR02173108 write_lef_library dumps out integer 0 for MINSPANLENGTH instead of 0.000

CCMPR02173067 M3 pins are not aligned with the tracks

CCMPR02172910 fcroute unable to route bumps outside rectilinear die area (using srouteFcDieAreaOffset)

CCMPR02172613 routeDesign leaving lot of M1 patches/trims and causing thousands of DRCs

CCMPR02172313 Many DIAG messages showed in placement related to spiPadSwapInstAreaTechSite

CCMPR02171927 Innovus cannot detect V0 spacing violation when cell is defined as OBS

CCMPR02171863 What is correct usage of setAddStripeMode -preventive_color_opt <true

CCMPR02171832 Feedthrough topology GUI is not working for feedthrough net with primary input port as the driver

CCMPR02171144 MBFF mapping dropping instances in 19.71-e084

CCMPR02171106 Data integrity check failures in detail route after rolling in third party ECO

CCMPR02170487 Same-Metal-Aligned-Cut violations with M2 pin extensions

CCMPR02170243 OptDesign coeSetupOptimizerIteration::executeSingleIteration crash in INVS during Genus iSpatial

CCMPR02170115 commit_power_intent is taking more time and consuming more memory

CCMPR02169987 Fatal ERROR message as SHDB flow, (IMPSE-110): cannot read "::Rda_CDTV::ilmDataInfo(ram_128x16_test,currTag)"

CCMPR02169634 Mixed Placer continues without necessary license error

CCMPR02169449 Innovus is hanging during place_opt_design

CCMPR02169420 Innovus 19.11 got crash with place_opt_design -opt

CCMPR02169292 addStripe got SEGV in 19.1

CCMPR02169028 delete_clock_tree_repeaters preserving hpin during our Htree flow

CCMPR02168919 postCTS hangs

CCMPR02168541 Innovus GUI shows issue with displaying backside via

CCMPR02168536 ECO rolling in takes huge run time

CCMPR02168514 Over 500K lines of "#Off-grid fixed wire is found" in "Merging special wires" for FlexH clock tree routing

CCMPR02168174 Hierarchical UPF file has wrong supply net association

CCMPR02167804 Std M3-pin is not aligned with the routing track

CCMPR02167755 Blocking issue for optDesign -trackOpt: tQuantus fails because of wrong auto mapping file while iQuantus runs fine

CCMPR02167674 ecoDesign does not appear to read previously saved metrics and hence not appending to previous metrics

CCMPR02167588 addFiller added instances in the wrong power domain

CCMPR02167551 Innovus error on power state group in

CCMPR02167209 setobjFPlanPolygon command to give warning/error message to improve usability

CCMPR02166974 Detours and bad qor on NDR nets

CCMPR02166959 tQuantus too optimistic (tcap by 2.3%, xcap by 6.2%)

CCMPR02166958 dbGet top.insts.name crashes with long instance name

CCMPR02166951 Innovus is getting crashed at route_opt stage on optDesign -postRoute -setup

CCMPR02166627 Mismatch between iQuantus and signoff Quantus

CCMPR02166596 create_power_domain -update creates incorrect ::MSV_UPF value

CCMPR02166583 Crash seen during place_opt_design

CCMPR02166582 Need a method in verify_drc to ignore or override cell density checks

CCMPR02166578 Scan reorder caused LP violations - Reorder ISO cells

CCMPR02166547 Enhancement request to provide new setting for "set_db route_design_process_node i5"

CCMPR02166420 M1 variant pin connection by EEQ function

CCMPR02166218 globalDetailRoute runtime is too high for top level

CCMPR02166149 addRepeaterByRule deletes wires when routing alongRoute from ports to std cell pins

CCMPR02166124 It takes a lot of time in routeDesign -trackOpt in Innovus 19.12_e040.

CCMPR02166067 Place opt design is auto pruning scenarios

CCMPR02166043 addRepeaterByRule to add odd inverter options

CCMPR02166009 Update to latest 1801 linter 19.10-d317

CCMPR02165933 routeDesign -viaPillarOpt deletes all the signal nets if preceded by ecoRoute -fix_drc

CCMPR02165892 Blocking issue for optDesign -trackOpt: tQuantus fails because of wrong auto mapping file while iQuantus runs fine

CCMPR02165805 Crash at CTS during via pillar insertion (versions: 18.16 and 19.12)

CCMPR02165634 ecoRoute -fix_drc crashed

CCMPR02165496 Run time increases in P3 compared to P2

CCMPR02165232 SEGV during addEndCap

CCMPR02164864 Error messages reported during place_opt_design and the design crashes later in the flow

CCMPR02164708 Delay calculation hangs in optDesign

CCMPR02164701 Auto via generation not generating optimal vias for NDR rule

CCMPR02164666 Support 80pitch triplet via rule

CCMPR02164631 set_ideal_net crashes with DPO list

CCMPR02164613 NDR rule being dropped in db reload

CCMPR02164064 pgInstTerm dropping connectivity on 19.71 but not 18.71

CCMPR02164016 defIn/defOut runtime and memory issue

CCMPR02163963 addFiller leaving 1X gaps next to BUFX1 cells

CCMPR02163872 Stack trace during clock_design

CCMPR02163369 MAXLENGTH on ENCLOSURETABLE is not detected by Innovus

CCMPR02163204 Write out text label for the pin to the center of polygon pin shape

CCMPR02163202 oasisOut properties missing in 19.1*

CCMPR02162802 Enclosure false violation

CCMPR02162757 S8 eGR fix with S8V2 switch making design un-routable

CCMPR02162561 Core ccopt_design leaving lot of DRVs. Looks like DRV is NOT being called after the Area reclaim step

CCMPR02161974 optDesign -postCTS -setup crash

CCMPR02161773 Out of memory during trackopt

CCMPR02161705 5% of difference between Tqrc and SignoffQRC

CCMPR02161466 unspecifyIlm SEGV

CCMPR02161322 Critical- Placement Run crashed even with high memory usage

CCMPR02161079 With -use_point2point_router true, addStripe switches layer to connect M7Z padpin with useless M6Z jogs

CCMPR02160753 signoffOptDesign is introducing double pattern violations

CCMPR02160646 SEGV during add_port_driver within ccopt_design

CCMPR02160638 Crash during placeopt_design during area reclaim optimization

CCMPR02160600 Enhancement to add_stripe behavior around trim blockages

CCMPR02160560 19.11/19.12 not inserting level shifters, UPF was working in 18.14/18.15

CCMPR02160518 Innovus 19.11 SEGV when I try to close a Kit menu

CCMPR02160256 Crash at optDesign -postRoute

CCMPR02160052 Sub optimal logic placement leading to high WNS during PLACE

CCMPR02159831 postCTS opt is erroring out during clock pin alignment in Innovus 19.42-e007

CCMPR02159426 saveNetlist -onlyLeafCell -includePowerGround crashes with SEGV

CCMPR02159270 Flattening connects wires of local power nets together

CCMPR02159244 routeAndBufferBusSinkGroup does not honor bus guide for bus (WAR NRCR-27) in 19.12 while it does in 18.14s088

CCMPR02159063 Tquantus does not take in account FILLWIREOPC shape

CCMPR02159006 Excessive IMPSP-2031 during CTS

CCMPR02158986 The routeDesign -viaOpt fails to change single-cut to Multi-cut via

CCMPR02158869 editPowerVia to avoid using stack via

CCMPR02158525 place_connected is taking long runtime (about 4Hr) with padding on all flops

CCMPR02158243 timing_enable_multi_threaded_reporting set at false by route_design

CCMPR02157774 findBestRoiImprovingMove - ResynthesizeIslandGenus CRR based crash during iSpatial

CCMPR02157708 editPowerVia -split_long_via is inconsistent in dropping PG vias in multiple rows

CCMPR02157331 Innovus did not keep terminals locations when creating a new logical Hierarchy

CCMPR02157005 Incremental ICG Alignment in postcts disrupts ICG placement

CCMPR02156978 route_opt_design improvement

CCMPR02156925 Enabling cell usage during skewClock

CCMPR02156882 Segmentation fault crash while exiting Innovus

CCMPR02156819 Add -jog_connect_layer option to move wire drop-down menu

CCMPR02156342 DPT pin shapes loosing mask after assemble design

CCMPR02155605 Nanoroute places NDR via at top of via pillar on non-NDR track

CCMPR02155555 ecoRoute with 19.71-e073 build failed in dirty-map dbsDASaved::checkInsts

CCMPR02155432 FloorPlan with setFPlanMode -rowSiteWidth odd do not adjust core box

CCMPR02154981 LEF58_SPACING - SAMENET ADJACENTCUTS reports false violation

CCMPR02154751 editPint -fixOverlap does not fix the overlap pin

CCMPR02154673 createSignalPin promoting floating pins of an RLM to pgTerms

CCMPR02153812 nanoRoute SEGV during antenna fixing iteration

CCMPR02153463 False VT violations reported by Innovus

CCMPR02152840 Dynamic pin cap cal report is different between ccopt and CTS

CCMPR02152500 Hold Fixing failing to fix nets because of internal reason: SuccessiveFailureLimit

CCMPR02152185 Enhance request of report_ccopt_clock_tree_structure

CCMPR02151928 ERROR out while fixing tCIC

CCMPR02151150 Design with 45-degree RDL routing elicits IMPEXT-7081 and hangs during extraction

CCMPR02150568 Bus Planning - addRepeaterByRule -busMode to support fanout greater than one

CCMPR02150427 fix_ufc not following the macro profile when cutting ROWS around a multi-linear macro

CCMPR02150367 Massive number of IMPSP-5225 messages causing terabytes of log even when message_limit is 20

CCMPR02149897 False parallel run length spacing in Innovus

CCMPR02149876 Difference in utilization when using actual value and dbGet density

CCMPR02149863 Specified via pillar order is reversed by the tool

CCMPR02149845 Native multi-driver flow not working

CCMPR02149068 routeDesign -viaPillarOpt changes existing via pillar to via that does not meet pitch rule

CCMPR02148711 report_ccopt_clock_trees -summary does not show the number of explicit ignore pins

CCMPR02148590 addPowerSwitch command runtime issue

CCMPR02148290 add_fillers corrupting y_flip_type

CCMPR02147778 editPowerVia long runtime

CCMPR02147686 fcroute length matching using the constraint file

CCMPR02147041 Missed skewing opportunities in skewClock

CCMPR02147011 Enable support for opt cell groups to restrict cell usage to specified limits in IPO

CCMPR02143189 Enhancement new command to support sizing up/down the bus bit

CCMPR02142212 Enhance add_stripe to stop stripes on trim grid shapes

CCMPR02141705 Qualcomm: Zigzag CTS routing

CCMPR02139984 Support 1801 set_retention_elements

CCMPR02139899 ENCLOSUREEDGE rule not seen by checkPlace/refinePlace

CCMPR02139269 add_io buffers takes long time to flip the inst to match row orientation

CCMPR02139222 No Qor improvement seen with LOADCAP cells compared to baseline in routeopt

CCMPR02139111 addFiller creating DPT violations

CCMPR02138735 NR leaves partially open net in 19.1/19.2 but routes cleanly in 18.1

CCMPR02138466 Scan reordering not preserving scan ports when reorder_scan_keep_hinst_port_name is set

CCMPR02138276 addStripe SEGV in 19.11

CCMPR02138218 fix_ufc should be able to fix the violation

CCMPR02137817 Create via form has incorrect cutclass

CCMPR02137721 addPowerSwitch option -offsetReferencePoint core not using core boundary as reference point

CCMPR02137711 Enhancement for selected default power domain

CCMPR02137359 Pruned view is not recovering timing at preCTS in ECF flow

CCMPR02136002 verify_drc reports false ENCLOSUREEDGE violations randomly

CCMPR02135123 -ignore_clock_latency does not consider input delay in in2reg path

CCMPR02135118 fanout of 1 timing path is detouring during placement

CCMPR02134855 pgFill to fix isolated via adds vias which cause Same Metal Aligned Cuts violations

CCMPR02134217 sroute does not connect VSS stripes to the nearest VSS pins

CCMPR02133061 ERROR: (IMPSYC-179): add_power_switches cannot create nets with special character

CCMPR02128832 Crash seen during delay calculation at clock_post_route_repair step on routed DB

CCMPR02128501 ECF place_opt_design incremental placement SEGV

CCMPR02127382 cleanup_floorplan_for_macro_place dumping thousands of "dbshape" commands to logfile

CCMPR02125868 Innovus (NR) not fixing Via enclosure rule "VIAya.EN.16.10" but violates

CCMPR02124529 CTS routes excessively on lower DPT layers and leaves M1 DRCs

CCMPR02124501 editPowerVia added vias in spite of *any angle* Pump OBS on RV via layer

CCMPR02123725 Require a filler flow compatible with X1 Cut requirements

CCMPR02123029 Placement issue with MCP

CCMPR02122525 PostRoute timeDesign crash

CCMPR02122322 Multi Bit Splitting not happening during Placement

CCMPR02120446 eGR to support complex via rule handling with a user option

CCMPR02118388 Pin guide in guide gives IMPPTN-499 errors despite plenty of room in guides

CCMPR02118362 Replace via form should show the via currently selected

CCMPR02116222 routeDesign error out with NRDR-5 message

CCMPR02115337 Power reclaim degrades hold TNS at postroute

CCMPR02114111 replaceBlock command to correctly reflect db with macro lef pins changes

CCMPR02113118 Innovus import design

CCMPR02112162 Tool flagging false C4 WidthTable violations

CCMPR02111595 optDesign -postRoute adding redundant buffers and not upsizing short cells

CCMPR02110293 ccopt_design -cts routes in unusual zigzag pattern

CCMPR02109468 Command place_clones reports incorrect reason for clonePlace failed

CCMPR02108597 SDP place creates unwanted auto_sdp groups and degrades QOR

CCMPR02107523 Enhancement request to specify NSWidth targets during placement/optimization

CCMPR02106710 false violations on PARALLELRUNLENGTH/TWOWIDTH spacing table

CCMPR02101433 Clock constraint getting dropped at very next pin where it is defined

CCMPR02098856 read_physical is missing -incremental option for reading OA libs

CCMPR02097739 QoR degradation

CCMPR02096143 False checkPlace pin access violations

CCMPR02095696 TNS improvement seen during scanReorder is not retained after scanReorder

CCMPR02090335 TDGR layer promotion review

CCMPR02084630 Unwanted layer demotion to DPT layer near source, causing EM violations

CCMPR02080807 streamOut generate wrong GDS

CCMPR02079971 QoR changes in CCOPT with VP rule LEF due to different NRDR clock nets routing results

CCMPR02079855 How optimal is buffering

CCMPR02078813 Support 1801 refined state

CCMPR02064322 NR is unable to route design clean though congestion is low

CCMPR02063346 181/191: Change **WARN: (IMPILM-349): set_db ilm_keep_async false … to *Info : set_db ilm_keep_async fa

CCMPR02062115 Significantly high MBFF flop merging runtime on pd_msr_sys

CCMPR02054434 Innovus ERRORs out while executing command eco_add_repeater. Msg: **ERROR: (IMPOPT-7222):

CCMPR02053644 Clock route jogging on preferred routing layers

CCMPR02048019 trimMetalFillNearNet -createFillBlockage does not take care of the via

CCMPR02039421 Enhancement for verify_drc report with separate NDR categories

CCMPR02032793 User variable changes value after save_design

CCMPR02025711 Improve the congestion and DRCs at the corner of macro

CCMPR02021035 Enhancement for command read_timing_debug_report

CCMPR02018238 Fishbone clock routing required to minimize/balance ICG connectivity

CCMPR02010528 addStripe -over_power_domain 1 does not generate stripes on the domain boundary

CCMPR01979491 fixACLimitViolation not fixing simple violations

CCMPR01973883 assembleDesign causes pWires to teleport to negative x-space

CCMPR01968419 Controlled RCs for skewing

CCMPR01948826 ctd_trace is way too slow

CCMPR01906406 Native commands should accept get_db "location" output without requiring additional user processing

The Cadence Innovus Implementation System is optimized for the most challenging designs, as well as the latest FinFET 16nm, 14nm, 7nm, and 5nm processes, helping you get an earlier design start with a faster ramp-up. With unique new capabilities in placement, optimization, routing, and clocking, the Innovus system features an architecture that accounts for upstream and downstream steps and effects in the design flow. This architecture minimizes design iterations and provides the runtime boost you’ll need to get to market faster. Using the Innovus system, you’ll be equipped to build integrated, differentiated systems with less risk.

The Innovus system features a variety of key capabilities. Its massively parallel architecture can handle large designs and take advantage of multi-threading on multi-core workstations, as well as distributed processing over networks of computers.

Based on the well-established NanoRoute engine, next-generation slack and power-driven routing with track-aware timing optimization addresses signal integrity early on and improves post-route correlation. The Innovus system includes full-flow multi-objective technology, which makes concurrent electrical and physical optimization possible. It also shares a customizable flow via a common UI and user commands with synthesis and signoff tools. As a result, you can take advantage of robust reporting and visualization, improving your design efficiency and productivity across the whole digital flow.

With block sizes growing in both cell count and complexity, the number of macros that need to be positioned in the floorplan is exploding. The Innovus system offers mixed-macro and standard-cell placement, which enables macro locations to be automatically generated, reducing the time to create an optimal floorplan from days to hours.

The latest advances in machine learning computer science are very relevant for digital implementation flows. The Innovus system incorporates machine learning technology to deliver the best PPA for the most challenging, high-performance blocks. The designer has complete control over the machine learning training, to ensure it is customized for their specific design requirements.

Cadence’s Genus Synthesis Solution is tightly integrated with the Innovus system, which enables a seamless move from RTL synthesis to implementation. With shared placement and optimization technology from the GigaPlace and GigaOpt engines for Genus physical synthesis, this offers a big benefit for advanced-node design convergence.

As voltage decreases in the latest FinFET process nodes, IR and EM constraints become increasingly important. The Innovus system includes comprehensive power integrity-aware placement, optimization, clock tree, and routing features to ensure IR and EM violations are addressed during implementation without impacting final PPA.

Cadence’s Tempus Timing Signoff Solution, Quantus Extraction Solution, and Voltus IC Power Integrity Solution are integrated with the Innovus system. With this integration, you can accurately model parasitics, timing, signal, and power integrity effects at the early stage of physical implementation, and achieve faster convergence on these electrical metrics, resulting in more efficient design closure.

Place and Route in Cadence Innovus

Complete flow of innovus tool has been demonstrated in this video. Both command line and GUI mode have been covered in the same video. Important input files for this flow has also been discussed and how to create them has been explained.

Cadence enables global electronic design innovation and plays an essential role in the creation of today’s integrated circuits and electronics. Customers use Cadence software, hardware, IP and services to design and verify advanced semiconductors, consumer electronics, networking and telecommunications equipment, and computer systems. The company is headquartered in San Jose, Calif., with sales offices, design centers and research facilities around the world to serve the global electronics industry.

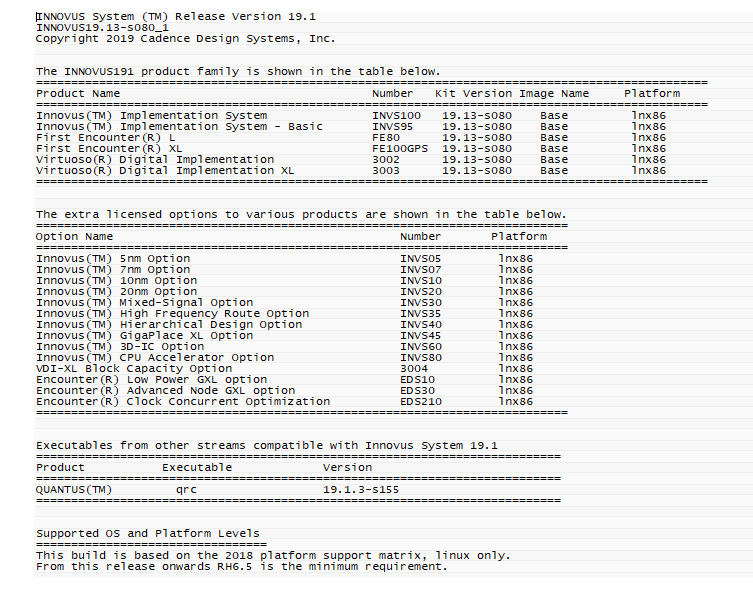

Product: Cadence INNOVUS

Version: 19.13.000 (ISR3) **

Supported Architectures: x86

Website Home Page : www.cadence.com

Languages Supported: english

System Requirements: RHEL 6.5 (lnx86) *

Size: 4.8 Gb

* This build is based on the 2018 platform support matrix, linux only. From this release onwards RH6.5 is the minimum requirement.

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please