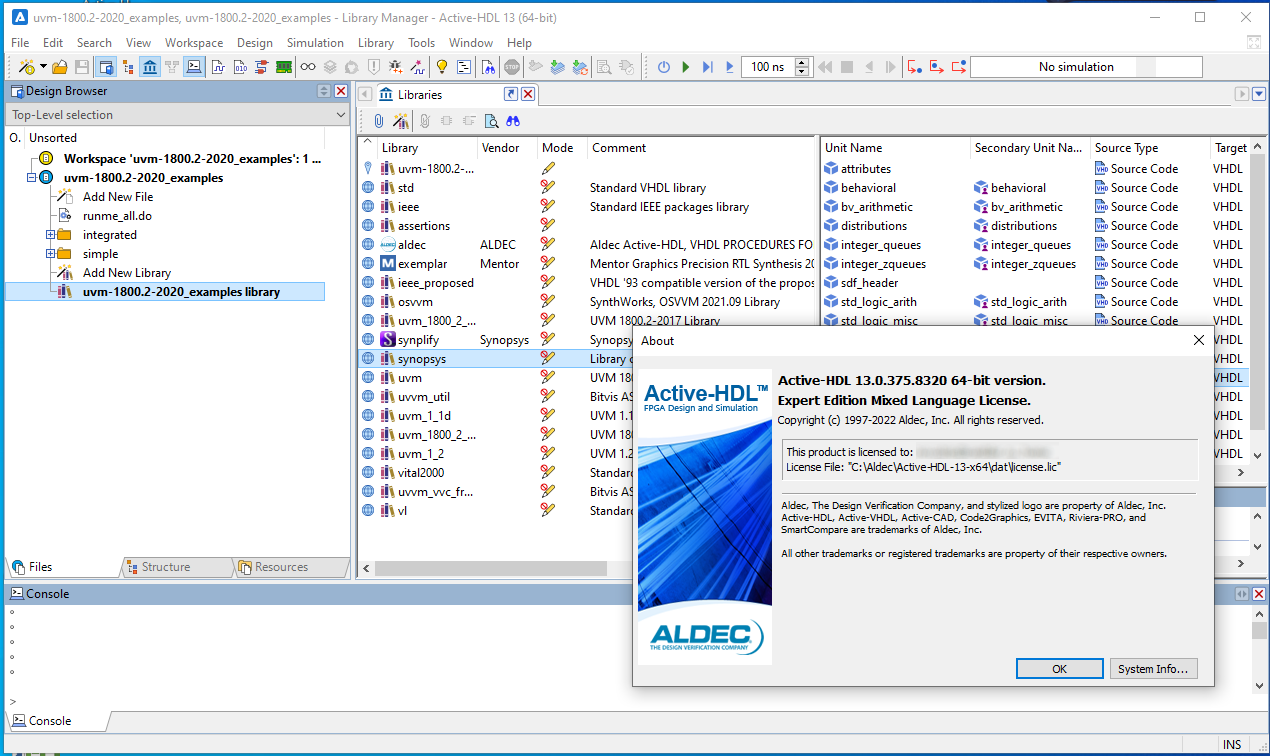

Aldec Active-HDL 13.0.375.8320 | 577.5 mb

Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification for FPGA and ASIC designs, advances VHDL’s verification capabilities with Active-HDL, version 13.0. This latest release introduces support for VHDL-2019 protected types with generics, composites of protected types, pointers to objects of protected types and composition with protected types.

Protected types were introduced in VHDL-2000 to allow the creation of class-like objects (similar to classes in C++), which then later became required for shared variables in VHDL-2002. In VHDL-2019, the capabilities of protected types have been significantly improved to address new use models essential for the creation of complex testbenches that require advanced data structures.

Protected types are a powerful mechanism for creating functional coverage, random test generation, messaging, unified error reporting and verification data structures such as memory models, FIFOs and scoreboards.

Engineers can also use protected types on an entity interface for sharing a single memory among multiple AXI4 memory-mapped external peripherals, ideal for verifying SoC FPGAs used for multi-sensor data aggregation.

The following is a brief overview of new features and changes introduced to Active-HDL 13 (BUILD 375.8320, 3/18/2022).

Performance Improvements

- The randomization performance has been enhanced for specific cases of random constraints.

- Opening and closing time of Active-HDL projects containing a large number of objects has been significantly reduced.

- The time required to change an active library in a design containing a large number of files has been significantly reduced.

- Performance of updating the design contents by using the Refresh contents dialog box has been significantly improved.

- The compilation time of logical and arithmetic constructs utilizing a number of operands has been reduced.

- The time of compilation of VHDL source files in the batch mode (VSimSA) has been significantly decreased.

Compiler and Simulator

NOTE: Due to internal changes in the compiler and simulator as well as updates in third-party tool libraries, all user-defined libraries should be re-compiled after the installation of Active-HDL 13. The installation program of the current version delivers and installs only the updated system and vendor-specific libraries that do not require re-compilation after Active-HDL is installed. All existing designs will not have any problems associated with re-compiling the libraries. If you update Active-HDL to version 13 and do not re-compile your design libraries, the following error message will be displayed in the Console window:

# ELBREAD: Warning: Files created by the old version of the compiler found.

# ELBREAD: Error: Library '<library_name>' has incompatible format. Recompile all library units.

VHDL Compilation and Simulation

- Starting from Active-HDL 13, compilation of constructs specific to the IEEE Std 1076-1987 standard is allowed only in the compiler modes compliant with IEEE Std 1076-1993 and IEEE Std 1076-2002. If required, it can be turned off by passing the -disable87 argument of the acom command. In the remaining compiler modes, that is, VHDL 2008 and VHDL 2019, the compiler does not accept the constructs of IEEE Std 1076-1987 and reports an error. Note also that the corresponding changes are implemented in the graphical user interface. For more information on these changes, refer to the User Interface section. (SPT80277)

- The COMP96_0283 error message provides information about the type of an object triggering the message and incorrect number of indices specified by the user. (SPT80653)

The following features introduced by IEEE Std 1076-2019 standard have been implemented to the current version of the compiler and simulator. In order to use them, if not stated otherwise, they must be enabled with the Standard version option in the Compilation | VHDL category of the Design Settings dialog box or by using the -2019 argument of the acom command:

- VHDL 2019 lowers the precedence of the ** exponentiation operator below the abs and not unary operators. In the previous standard revision, all these operators had the equal precedence.

- The arrays and records of the file type are supported. All elements of such composite types must be of the file type or the composite type consisting only of subelements of the file types.

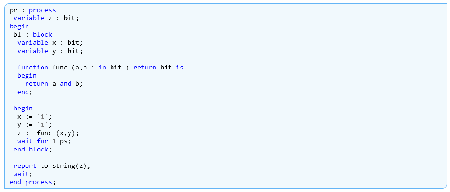

- The sequential block statements have been introduced. They allow grouping sequential statements in the same way as concurrent statements are grouped by the regular block statements. A sequential block statement can contain any sequential statement. In particular, other sequential block statements can be used there. The statements within a block can be preceded by declarations of objects which are local to the block. They are not visible outside of it and are removed from memory after the block execution is completed:

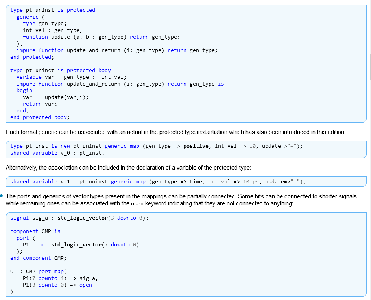

- The STD library has been enhanced with the REFLECTION package. The package provides the user with the protected types which can be used for collecting information on VHDL types and objects. The protected type instances are called mirrors and store the internal data associated with the examined VHDL objects. Each VHDL object has two dedicated mirrors: the value and subtype mirror. The value mirror stores the copy of the value of the inspected object and provides the access to that copy through a dedicated method. It also supplies a method for accessing its subtype and a set of methods performing some check operations that are also available via object attributes. The subtype mirror represents the meta data of the mirrored type or subtype and provide a set of methods performing some checks that are available via type or subtype attributes.

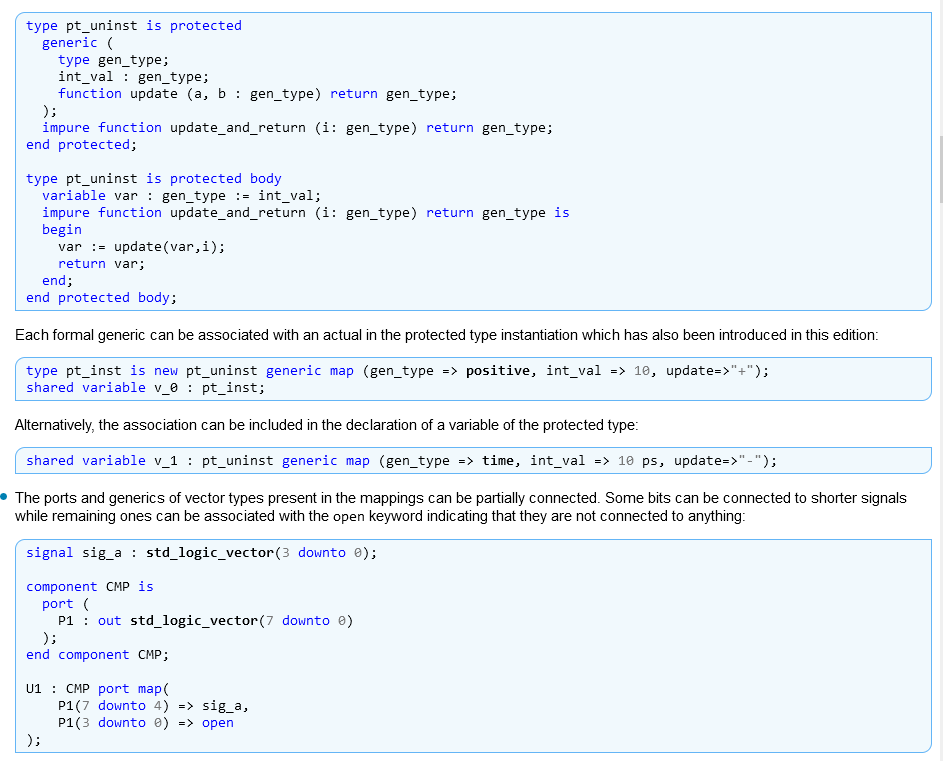

- The declaration of a protected type can contain the generic clause allowing the user to parameterize the protected type with a constant, type, package, or subprogram declaration:

-The arrays and records of protected types are supported. All elements of such composite types must be of protected types or composite types consisting only of subelements of protected types.

-The support for the access types designating protected types and composite types of protected types has been introduced.

-A configuration and the associated entities can reside in different libraries.

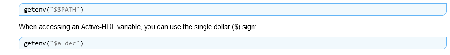

-The system environment variables and variables defined in Active-HDL can be accessed from VHDL code by calling one of two overloaded getenv functions. Both functions take the name of the variable as a parameter and return the variable value. The first one returns a string and the other returns the value of the line type. When accessing the system environment variable, the variable name can be preceded with the $$ double dollar sign to avoid ambiguous function calls:

Notice that both functions are case-insensitive and the dollar signs preceding variable names are optional and can be omitted.

- A preliminarily support for the array interface type declaration has been introduced. This functionality allows the user to declare generics of array types in which the element and index type can be specified during generic mapping. (SPT80292, SPT80788, SPT80789, SPT80792)

SystemVerilog Compilation and Simulation

- The if-generate conditional generate construct can be used in programs, modules, and interfaces that are parameterized with a type.

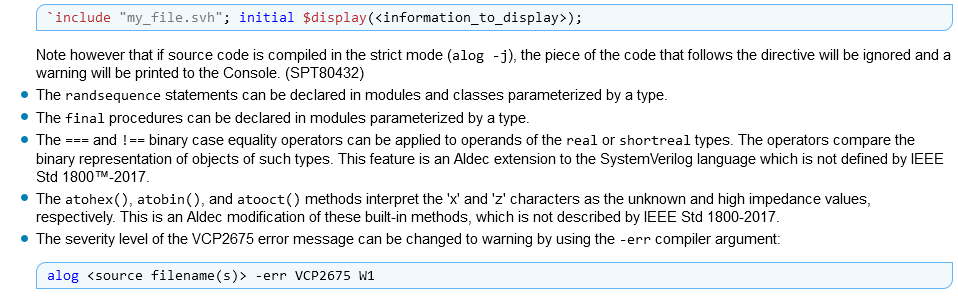

- An extension to the `include directive has been implemented. Now, a portion of source code (e.g. a statement) may appear on the same line as the file inclusion directive, not just a white space or a comment. The sample source code is presented below:

- The support for the user-defined nettypes has been extended on the 4-state integral packed unions, 2-state integral packed vectors, arrays, structures and unions, the real and shortreal types, and fixed-size unpacked vectors, structures and unions. As a result, all types mentioned in the § 6.6.7 section of IEEE Std 1800™-2012 are supported except for fixed-size unpacked arrays. The resolution functions can be defined for nettypes of all supported types other than packed unions.

- The data type of a user-defined nettype can be specified with a type parameter.

- Transition bins are supported in classes parameterized with a type.

- The distribute_first covergroup type option is supported.

- The predefined rc_optimize_threshold and rc_optimize_verbose variables are no longer supported.

SystemVerilog Assertions

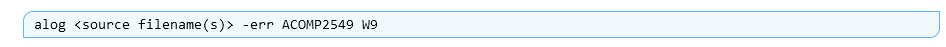

- The ACOMP2548 warning message can be turned off by decreasing its severity to the lowest possible level with the -err compiler argument:

OVA Assertions

- Active-HDL 13 discontinues the support for the OpenVera verification language (OVA). Starting with this version, the assertions described in the OpenVera LRM will not be recognized and cannot be compiled. All the related compiler and simulator features, scripter commands, OVA-related command arguments, GUI options as well as the documentation are no longer available.

C/C++/SystemC Compilation and Simulation

- The -Werror=return-type option is now added when the ccomp command calls the gcc compiler to avoid potential issues with reading unspecified values. Currently, compilation of a non-void function without the return statement will report an error instead of a warning. Users can either modify their source code or pass the new -Wno-error=return-type argument to the syntax of the ccomp command to achieve the previous behavior.

- The support for several older versions of Microsoft Visual Studio has been discontinued. The GUI options that enable the support for Visual C++ ver. 6.0 to 9.0 have been removed from the compiler settings available in the C/C++ Configuration and VHPI/PLI/VPI/DPI-C Wizard dialog boxes. Additionally, the syntax of the ccomp command has been updated. For more information, refer to the Scripts section.

Design Coverage

- The new coverage pragmas are supported by the Verilog compiler. The coverage off/on and translate_off/on pragmas can be used alternatively to the existing verilog_cover_off/on pragmas.

Path Coverage

- The limit of detailed paths within pathgroups listed in a generated report was removed. Previously, the details were omitted when there were more than 100 paths. (SPT80180)

Design Management

- The behavior of the stimulus active set can be modified with the Keep stimuli set active when simulation is initialized or restarted check box available in the Simulation category of the Preferences dialog box. If this option is selected, the current active set remains active after simulation restart or initialization. Otherwise, it is deactivated. For more information, refer to the Stimuli Window topic of the User's Guide.

Libraries

The following updates have been introduced to the system and vendor-specific libraries:

New or Updated Libraries

- Verification Libraries

1. OSVVM 2021.09

2. The default UVM library (uvm) has been changed from version 1.1d to 1800.2-2017. The installation program provides the 2017-1.1 implementation of this library.

3. The new uvm_1800_2_2020 library is installed in the current version. The 2020-1.1 implementation of this library is delivered.

4. The UVVM Utility (uvvm_util) and VHDL Verification Component Framework (uvvm_vvc_framework) libraries have been updated to version v2021.05.26.

- Implementation

1. Intel Quartus Prime Standard 21.1

2. Intel Quartus Prime Pro 21.4. New libraries: FOURTEENNM_HSSI_ALL, TENNM, TENNM_HSSI_ALL, FOURTEENNM_HSSI_ALL_VER, TENNM_HSSI_ALL_VER, TENNM_VER

3. Lattice ispLEVER Classic 2.1. New libraries: POWR, OVI_POWR

4. Lattice Diamond 3.12 SP1. New libraries: LFMNX, MACHXO3LFP, OVI_LFMNX, OVI_MACHXO3LFP.

5. Lattice Propel 2.0

6. Lattice Radiant 3.0. New libraries: LFCPNX, OVI_LFCPNX

7. Microsemi Libero SoC 2021.3

8. Xilinx Vivado 2021.2

Discontinued Libraries

- Implementation

1. Intel Quartus Prime Pro 21.1. Removed libraries: TENNM_CT1, FOURTEENNM_CT1, TENNM_CT1_VER, FOURTEENNM_CT1_VER

2. Lattice Radiant 3.0. Removed libraries: OVI_ICE40UP_TIMING, OVI_LIFCL_TIMING

Design Flow Manager

New Flowcharts

- HDL Synthesis

1. Aldec HES-SyntHESer 2021.07

2. Intel Quartus Prime Standard Synthesis & Implementation 21.1

3. Intel Quartus Prime Pro Synthesis & Implementation 20.4

4. Intel Quartus Prime Pro Synthesis & Implementation 21.1

5. Intel Quartus Prime Pro Synthesis & Implementation 21.2

6. Intel Quartus Prime Pro Synthesis & Implementation 21.3

7. Intel Quartus Prime Pro Synthesis & Implementation 21.4

8. Lattice Diamond LSE 3.12 (supports Diamond LSE 3.12 SP1)

9. Lattice Synthesis & Implementation in Diamond 3.12 (supports Diamond 3.12 SP1)

10. Lattice Radiant Software LSE 3.0

11. Lattice Synthesis & Implementation in Radiant Software 3.0

12. Synopsys Synplicity Synplify Pro R-2020.09 for Actel/Microsemi (supports Synplify Pro R-2020.09M-SP1-1)

13. Synopsys Synplicity Synplify Pro R-2021.03 for Actel/Microsemi (supports Synplify Pro R-2021.03M)

14. Synopsys Synplicity Synplify Pro R-2020.09 for Lattice (supports Synplify Pro R-2020.09LR-SP1)

15. Synopsys Synplicity Synplify Pro R-2021.03 for Lattice (supports Synplify Pro R-2021.03L-SP1)

16. Xilinx Vivado 2020.3 Synthesis

17. Xilinx Vivado 2021.1 Synthesis

18. Xilinx Vivado 2021.2 Synthesis

19. Xilinx Vivado 2020.3 Synthesis & Implementation

20. Xilinx Vivado 2021.1 Synthesis & Implementation

21. Xilinx Vivado 2021.2 Synthesis & Implementation

- Implementation

1. Intel Quartus Prime Standard Implementation 21.1

2. Intel Quartus Prime Pro Implementation 20.4

3. Intel Quartus Prime Pro Implementation 21.1

4. Intel Quartus Prime Pro Implementation 21.2

5. Intel Quartus Prime Pro Implementation 21.3

6. Intel Quartus Prime Pro Implementation 21.4

7. Lattice Diamond 3.12 (supports Diamond 3.12 SP1)

8. Lattice Radiant Software 3.0

9. Microsemi Libero SoC 12.6

10. Microsemi Libero SoC 2021.1

11. Microsemi Libero SoC 2021.2

12. Xilinx Vivado 2020.3 Implementation

13. Xilinx Vivado 2021.1 Implementation

14. Xilinx Vivado 2021.2 Implementation

Updated Flowcharts

- HDL Synthesis

1. Lattice ispLEVER Classic LSE (supports ispLEVER Classic LSE 2.1)

2. Lattice Radiant Software LSE 2.2 (supports Radiant Software LSE 2.2.1)

3. Lattice Synthesis & Implementation in Radiant Software 2.2 (supports Radiant Software 2.2.1)

4. Synopsys Synplicity Synplify Pro P-2019.03 for Actel/Microsemi (supports Synplify Pro P-2019.03A-SP1)

5. Synopsys Synplicity Synplify Pro Q-2020.03 for Actel/Microsemi (supports Synplify Pro Q-2020.03M-SP1)

6. Synopsys Synplicity Synplify Pro Q-2020.03 for Lattice (supports Synplify Pro Q-2020.03L-SP1 and Synplify-PRO Q-2020.03LR-SP1-1)

- Implementation

1. Lattice ispLEVER Classic (supports ispLEVER Classic 2.1)

2. Lattice Radiant Software 2.2 (supports Radiant Software 2.2.1)

3. Actel/Microsemi Designer 9.2 (supports Microsemi Libero IDE 9.2 SP4)

Flowchart Changes and Improvements

- The use of the controls such as tabs, combo boxes, and spin boxes located in the Design Flow Manager dialog boxes has been improved. Now, the settings in these controls can be changed by using the mouse wheel. The change is available for the latest versions of the vendor flowcharts.

- The temperature and static power parameters have been extracted from the Speed Grade option in the Xilinx Vivado 2020.x flowcharts. The options for controlling these parameters are available for certain devices in the General tab of the Synthesis Options dialog box and the Main tab of the Implementation Options dialog box. If an UltraScale, UltraScale+, or Versal family is selected, the temperature parameter is controlled with the Temperature option. If a Versal family is selected, there is also the Static Power option available that controls the static power parameter.

- The Reserve Probe option has been enabled for all device families in the Microsemi Libero SoC 12.5 and newer flowcharts. (SPT81126)

Discontinued Flowcharts

- HDL Synthesis

1. Synopsys FPGA Compiler II

2. Synopsys FPGA Express

3. Synopsys FPGA Express (Innoveda OEM)

4. Synopsys FPGA Express (Viewlogic OEM)

5. Synopsys FPGA Express (Xilinx OEM)

- Physical Synthesis

1. Magma PALACE 1.2, 2.0, 3.0, 3.1, 3.2, 3.3 for Actel/Microsemi

2. Magma PALACE 2.4, 2.5 for Altera and Xilinx

Block Diagram Editor

- The order of ports, generics, and parameters in generated code can be changed with the Sorting Order option accessible from the Generation | Declaration of Ports category of the Preferences dialog box. If Declaration is selected, the order is compliant with the sequence in which the objects were added to the diagram. If Legacy is selected, the items are grouped by their modes and items in each group are listed in the alphabetical order. The order can be also changed with the generationsortingorder macro command. See the Scripts section for details. (SPT80109, SPT80162)

- The Port Mapping tabs of the Symbol Instance Properties and Fub Instance Properties dialog boxes have been rearranged. The Port Mapping Details window invoked with the Details button and the Details button itself are no longer available. The content of that window is presented directly in the Port Mapping tab as new columns in the table and can be enabled with the Details check box.

- The behavior of the Format Diagram Items toolbar has been changed. Now, modification of object properties is possible for selected block diagram items and it does not influence the global editor settings specified in the Appearance category of the Preferences dialog box.

State Diagram Editor

- The order of ports, generics, and parameters in generated code can be changed with the Sorting Order option accessible from the Generation | Declaration of Ports category of the Preferences dialog box. If Declaration is selected, the order is compliant with the sequence in which the objects were added to the diagram. If Legacy is selected, the items are grouped by their modes and items in each group are listed in the alphabetical order. The order can be also changed with the generationsortingorder macro command. See the Scripts section for details. (SPT80109, SPT80162)

Stimuli Window

- The Sequences dialog box has been introduced. The window allows creating keyboard shortcuts activating sequences of actions controlling stimuli. To open the Sequences dialog box, pick the Sequences option from the Tools menu. Notice that the dialog box provides the functionality that was previously available in the Hotkeys tab of the Stimulators dialog box (which was removed from the current edition). For more information, refer to the Dialog Box Reference chapter of the User's Guide.

- The Set Stimulus option has been added to the context menu of signals presented in the Watch and Advanced Dataflow windows. The option allows associating the signals with stimuli defined by using the Stimuli window or the force macro command.

- The Stimulators dialog box has been removed from the Active-HDL environment. The window was a tool for creating stimuli included in the Waveform Viewer. Currently, it is replaced by the standalone Stimuli window, the Stimulus Properties dialog box, and the Sequences dialog box which has been introduced in this version. All the actions that were possible to execute in the Stimulators dialog box can now be accomplished in these windows. The stimuli created with the Stimulators dialog box and saved to a file in previous editions can be imported. Refer to the Scripts section for details.

- The Stimulators option was removed from the context menus of signals presented in the Signal Grid pane of the Waveform Viewer window and the Structure tab of the Design Browser window (i.e. the Hierarchy Viewer). The option opened the Stimulators dialog box which was removed in the current edition. In the Assertion Viewer window, the option was replaced with the Set Stimulus option providing access to stimuli created in the Stimuli window.

- The Assign as Stimulator option assigning an editable signal as a stimulus to its original version that was working independently of the Stimuli window and was accessible from the context menu of the Signal Grid pane of the Waveform Viewer has been removed. Notice that the Assign as Stimulus option executing equivalent action in the Stimuli window is available in the context menu.

Scripts

The following changes have been introduced to the Active-HDL macro commands:

- The -aserror argument has been added to the syntax of the acom command. The argument allows raising severity of any warning message printed by the VHDL compiler to the error level.

- The -input_ports argument has been added to the syntax of the alog command. The new argument allows specifying the default kind for an input port declared with a type reg but without the use of the var keyword.

- The filepsloptions command has been implemented. The new command allows applying the global -auts argument of the acom or alog command to the specified PSL source files. The command is the equivalent of the Change the evaluation of asynchronous assertions into continuous mode option available in the Compile tab of the File Properties dialog box of a PSL source file attached to the design tree.

- The -atck argument of the alog command is no longer supported and it has been removed from the command syntax. The -assert_clock_count argument is a successor of the obsolete argument. The new argument allows enabling or disabling the clock tick counts and displaying them in a assertion/cover report. This argument has been also added to the syntax of the acom command.

- The new 1800.2-2020 parameter of the -uvmver argument has been added to the syntax of the alog command.

- The -vhdl_strict_range_check argument has been added to the syntax of the asim command. The new argument disables optimizations that can prevent the simulator from checking whether a signal value falls within the specified value range.

- The filter command and the -filter argument of the asim command support the ELBREAD_0049, RUNTIME_0155, RUNTIME_0177, RUNTIME_0222, RUNTIME_0230, and RUNTIME_0375 simulator messages. (SPT79842)

- The -vc6, -vc7, -vc8, and -vc9 arguments have been removed from the syntax of the ccomp command and they are no longer supported. The support for Microsoft Visual C++ compiler ver. 6.0-9.0 has been discontinued.

- The execution of the force command creates a new stimuli in the current active set of stimuli presented in the Stimuli window.

- The stimuli created with the force command or the Stimuli window are not applied to signals if they were set before the restart or initialization of the simulation session. The reason is that these operations deactivate the current active set presented in the Stimuli window. To make sure the user is informed about this situation, the warning message: The stimuli set <name> has been made inactive is displayed in the Console window. To apply stimuli to signals, mark the <name> set as active in the Stimuli window. Notice that this behavior can be changed in the Preferences dialog box. Refer to the Design Management section for details.

- The generationsortingorder command, which has been introduced in this edition, allows the user to choose the order of ports and generics/parameters in code generated from BDE and FSM diagrams. The command can be invoked with the declaration or legacy arguments that are equivalent to the Declaration and Legacy values of the Sorting Order option from the Active-HDL preferences, respectively. Refer to the Block Diagram Editor or State Diagram Editor sections for details.

- The importqsys and importplatformdesigner commands are no longer supported.

- The -hde argument has been removed from the syntax of the open, opendocument, and addfile commands.

- The -hideprocesses and -showprocesses arguments of the structure command are deprecated. It is recommended to use the -filter concurrent argument with the off and on parameters instead, respectively. (SPT79367)

- The stimuli created with the Stimulators dialog box or the force macro command and saved to a file in previous editions can be imported by using the force argument of the write macro command and then by executing the macro produced by this command. The exception are the legacy stimuli of the Hotkey and Predefined types which cannot be imported. For details, refer to the description of the force argument of the write command in the Macro Command Reference chapter.

- The stimulators argument of the write command exporting the legacy stimuli created in the previous editions has been replaced with the stimuli argument exporting the new stimuli created with the Stimuli window or the force macro command. The exported stimuli are written to the XML file format.

The following changes have been introduced to the predefined Active-HDL variables:

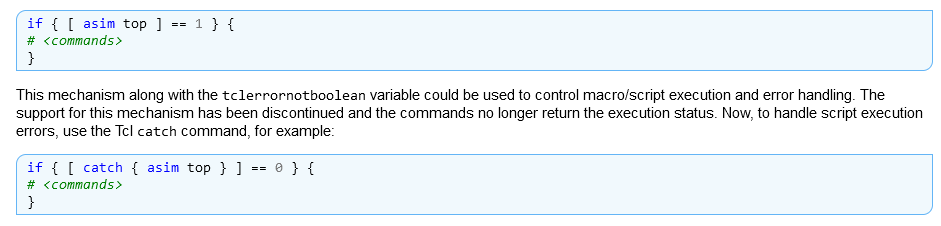

- The tclerrornotboolean variable is no longer supported.

- In previous versions, the acom, alog, asim, buildc, and edfcomp macro commands returned the execution status (0 when failed and 1 if succeeded) when they were used in Tcl scripts or DO macros executed in the Tcl/Compatibility mode, for example:

- The resume_on_error variable has been implemented. The new variable allows resuming the execution of Tcl scripts or DO macro commands run in the Tcl/Compatibility mode after they have been terminated by an error. When the variable is set to 0 or if it is not set, the error will break macro execution. Otherwise, if the variable is set to 1, a macro/script interrupted by an error will be resumed. In order to use the variable, it must be set in the DO mode.

User Interface

- The autocomplete mechanism available in the HDL Editor and the Console window has been improved. Now, autocompletion of the folder and file names also works for all the supported native Tcl commands and for the user-defined commands created by using the Tcl proc command. (SPT79963)

- The behavior of the Disable VHDL 1076-1987 syntax option available in the Preferences (Compilation|VHDL Compiler), Design Settings (Compilation|VHDL), and File Properties (Compile) dialog boxes has changed. Now, the option is only available when the Standard version option is set to either the VHDL 1076-1993 or VHDL 1076-2002 value. If any remaining value is selected, the Disable VHDL 1076-1987 syntax option is disabled.

- The Resources tab of the Design Browser window displays by default four new resource folders that allow filtering the additional design files of the following extensions:

. Coverage Databases (filters the files with the *.acdb extension)

. Matlab/Simulink Files (shows the files with the *.m, *.mdl, and *.slx extensions).

. Profiler Databases (displays the files with the *.tbp extension)

. Script Files (presents the files with the *.do, *.tcl, and *.pl extensions).

- Due to the discontinued import of simulation scripts generated by Intel's Qsys and Platform Designer system integration tools, the Altera/Intel Qsys Simulation Script and Intel Platform Designer Simulation Script options have been removed from the File | Import menu.

- The HDL Code Statistics option is no longer available from the Tools menu. To start the tool that analyzes design source files, execute the $aldec\bin\clocGui.exe program. Note also that in the future releases of Active-HDL, HDL Code Statistics will be delivered as a command-line tool only.

- The new color themes are available. Starting from this version of Active-HDL, the dark and dark high contrast themes are provided. Additionally, the new Appearance Files (*.app) are provided for the most frequently used Active-HDL windows such as HDL Editor, Block Diagram Editor, Waveform Viewer, Memory Viewer, Console window, Advanced Dataflow window, and debugging tool windows. The new theme files are grouped and stored in separate subfolders of the $aldec\preferences\color_theme directory. Note also that the previous predefined Appearance Files for the Waveform Viewer (asdb_wave_black_background.app, asdb_wave_lightgrey_background.app, and asdb_wave_white_background.app) installed to the $aldec\dat subfolder are no longer available. (SPT80254)

Installation

– The installation program of Active-HDL has been upgraded to InstallShield ver. 2021 R2.

Active-HDL Interfaces and Wizards

The following changes and improvements have been made to the built-in third-party interfaces:

- Spec-TRACER Requirements Lifecycle Management System

. The previously offered interface to Spec-TRACER Requirements Lifecycle Management System has been replaced by a new version of the Spec-TRACER tool. Active-HDL 13 includes the preliminary version of the tool. Contact Aldec Support for more information.

The following changes and improvements have been made to the import of third-party projects:

- Active-CAD Import

. The support for the import of the Active-CAD projects will be discontinued in the future editions of Active-HDL.

- Altera/Intel Import

. The import of simulation scripts coming from Altera/Intel Qsys system integration tool has been discontinued. Due to this change, the corresponding GUI options as well as dedicated Do macros and Tcl commands are no longer available. Refer to the Scripts and User Interface sections for more information.

. The import of simulation scripts coming from Intel Platform Designer is no longer supported. Due to this change, the corresponding GUI options, dedicated Do macros, and Tcl commands are no longer available. For the detailed information on using Platform Designer simulation scripts in the current version of Active-HDL, see the Performing Functional Simulation of the system created with Platform Designer in Active-HDL application note on the Aldec website. For further information about related changes of the import feature, refer to the Scripts and User Interface sections in this document.

Performance Improvements

- The randomization performance has been enhanced for specific cases of random constraints.

- Opening and closing time of Active-HDL projects containing a large number of objects has been significantly reduced.

- The time required to change an active library in a design containing a large number of files has been significantly reduced.

- Performance of updating the design contents by using the Refresh contents dialog box has been significantly improved.

- The compilation time of logical and arithmetic constructs utilizing a number of operands has been reduced.

- The time of compilation of VHDL source files in the batch mode (VSimSA) has been significantly decreased.

Compiler and Simulator

NOTE: Due to internal changes in the compiler and simulator as well as updates in third-party tool libraries, all user-defined libraries should be re-compiled after the installation of Active-HDL 13. The installation program of the current version delivers and installs only the updated system and vendor-specific libraries that do not require re-compilation after Active-HDL is installed. All existing designs will not have any problems associated with re-compiling the libraries. If you update Active-HDL to version 13 and do not re-compile your design libraries, the following error message will be displayed in the Console window:

# ELBREAD: Warning: Files created by the old version of the compiler found.

# ELBREAD: Error: Library '<library_name>' has incompatible format. Recompile all library units.

VHDL Compilation and Simulation

- Starting from Active-HDL 13, compilation of constructs specific to the IEEE Std 1076-1987 standard is allowed only in the compiler modes compliant with IEEE Std 1076-1993 and IEEE Std 1076-2002. If required, it can be turned off by passing the -disable87 argument of the acom command. In the remaining compiler modes, that is, VHDL 2008 and VHDL 2019, the compiler does not accept the constructs of IEEE Std 1076-1987 and reports an error. Note also that the corresponding changes are implemented in the graphical user interface. For more information on these changes, refer to the User Interface section. (SPT80277)

- The COMP96_0283 error message provides information about the type of an object triggering the message and incorrect number of indices specified by the user. (SPT80653)

The following features introduced by IEEE Std 1076-2019 standard have been implemented to the current version of the compiler and simulator. In order to use them, if not stated otherwise, they must be enabled with the Standard version option in the Compilation | VHDL category of the Design Settings dialog box or by using the -2019 argument of the acom command:

- VHDL 2019 lowers the precedence of the ** exponentiation operator below the abs and not unary operators. In the previous standard revision, all these operators had the equal precedence.

- The arrays and records of the file type are supported. All elements of such composite types must be of the file type or the composite type consisting only of subelements of the file types.

- The sequential block statements have been introduced. They allow grouping sequential statements in the same way as concurrent statements are grouped by the regular block statements. A sequential block statement can contain any sequential statement. In particular, other sequential block statements can be used there. The statements within a block can be preceded by declarations of objects which are local to the block. They are not visible outside of it and are removed from memory after the block execution is completed:

- The STD library has been enhanced with the REFLECTION package. The package provides the user with the protected types which can be used for collecting information on VHDL types and objects. The protected type instances are called mirrors and store the internal data associated with the examined VHDL objects. Each VHDL object has two dedicated mirrors: the value and subtype mirror. The value mirror stores the copy of the value of the inspected object and provides the access to that copy through a dedicated method. It also supplies a method for accessing its subtype and a set of methods performing some check operations that are also available via object attributes. The subtype mirror represents the meta data of the mirrored type or subtype and provide a set of methods performing some checks that are available via type or subtype attributes.

- The declaration of a protected type can contain the generic clause allowing the user to parameterize the protected type with a constant, type, package, or subprogram declaration:

-The arrays and records of protected types are supported. All elements of such composite types must be of protected types or composite types consisting only of subelements of protected types.

-The support for the access types designating protected types and composite types of protected types has been introduced.

-A configuration and the associated entities can reside in different libraries.

-The system environment variables and variables defined in Active-HDL can be accessed from VHDL code by calling one of two overloaded getenv functions. Both functions take the name of the variable as a parameter and return the variable value. The first one returns a string and the other returns the value of the line type. When accessing the system environment variable, the variable name can be preceded with the $$ double dollar sign to avoid ambiguous function calls:

Notice that both functions are case-insensitive and the dollar signs preceding variable names are optional and can be omitted.

- A preliminarily support for the array interface type declaration has been introduced. This functionality allows the user to declare generics of array types in which the element and index type can be specified during generic mapping. (SPT80292, SPT80788, SPT80789, SPT80792)

SystemVerilog Compilation and Simulation

- The if-generate conditional generate construct can be used in programs, modules, and interfaces that are parameterized with a type.

- An extension to the `include directive has been implemented. Now, a portion of source code (e.g. a statement) may appear on the same line as the file inclusion directive, not just a white space or a comment. The sample source code is presented below:

- The support for the user-defined nettypes has been extended on the 4-state integral packed unions, 2-state integral packed vectors, arrays, structures and unions, the real and shortreal types, and fixed-size unpacked vectors, structures and unions. As a result, all types mentioned in the § 6.6.7 section of IEEE Std 1800™-2012 are supported except for fixed-size unpacked arrays. The resolution functions can be defined for nettypes of all supported types other than packed unions.

- The data type of a user-defined nettype can be specified with a type parameter.

- Transition bins are supported in classes parameterized with a type.

- The distribute_first covergroup type option is supported.

- The predefined rc_optimize_threshold and rc_optimize_verbose variables are no longer supported.

SystemVerilog Assertions

- The ACOMP2548 warning message can be turned off by decreasing its severity to the lowest possible level with the -err compiler argument:

OVA Assertions

- Active-HDL 13 discontinues the support for the OpenVera verification language (OVA). Starting with this version, the assertions described in the OpenVera LRM will not be recognized and cannot be compiled. All the related compiler and simulator features, scripter commands, OVA-related command arguments, GUI options as well as the documentation are no longer available.

C/C++/SystemC Compilation and Simulation

- The -Werror=return-type option is now added when the ccomp command calls the gcc compiler to avoid potential issues with reading unspecified values. Currently, compilation of a non-void function without the return statement will report an error instead of a warning. Users can either modify their source code or pass the new -Wno-error=return-type argument to the syntax of the ccomp command to achieve the previous behavior.

- The support for several older versions of Microsoft Visual Studio has been discontinued. The GUI options that enable the support for Visual C++ ver. 6.0 to 9.0 have been removed from the compiler settings available in the C/C++ Configuration and VHPI/PLI/VPI/DPI-C Wizard dialog boxes. Additionally, the syntax of the ccomp command has been updated. For more information, refer to the Scripts section.

Design Coverage

- The new coverage pragmas are supported by the Verilog compiler. The coverage off/on and translate_off/on pragmas can be used alternatively to the existing verilog_cover_off/on pragmas.

Path Coverage

- The limit of detailed paths within pathgroups listed in a generated report was removed. Previously, the details were omitted when there were more than 100 paths. (SPT80180)

Design Management

- The behavior of the stimulus active set can be modified with the Keep stimuli set active when simulation is initialized or restarted check box available in the Simulation category of the Preferences dialog box. If this option is selected, the current active set remains active after simulation restart or initialization. Otherwise, it is deactivated. For more information, refer to the Stimuli Window topic of the User's Guide.

Libraries

The following updates have been introduced to the system and vendor-specific libraries:

New or Updated Libraries

- Verification Libraries

1. OSVVM 2021.09

2. The default UVM library (uvm) has been changed from version 1.1d to 1800.2-2017. The installation program provides the 2017-1.1 implementation of this library.

3. The new uvm_1800_2_2020 library is installed in the current version. The 2020-1.1 implementation of this library is delivered.

4. The UVVM Utility (uvvm_util) and VHDL Verification Component Framework (uvvm_vvc_framework) libraries have been updated to version v2021.05.26.

- Implementation

1. Intel Quartus Prime Standard 21.1

2. Intel Quartus Prime Pro 21.4. New libraries: FOURTEENNM_HSSI_ALL, TENNM, TENNM_HSSI_ALL, FOURTEENNM_HSSI_ALL_VER, TENNM_HSSI_ALL_VER, TENNM_VER

3. Lattice ispLEVER Classic 2.1. New libraries: POWR, OVI_POWR

4. Lattice Diamond 3.12 SP1. New libraries: LFMNX, MACHXO3LFP, OVI_LFMNX, OVI_MACHXO3LFP.

5. Lattice Propel 2.0

6. Lattice Radiant 3.0. New libraries: LFCPNX, OVI_LFCPNX

7. Microsemi Libero SoC 2021.3

8. Xilinx Vivado 2021.2

Discontinued Libraries

- Implementation

1. Intel Quartus Prime Pro 21.1. Removed libraries: TENNM_CT1, FOURTEENNM_CT1, TENNM_CT1_VER, FOURTEENNM_CT1_VER

2. Lattice Radiant 3.0. Removed libraries: OVI_ICE40UP_TIMING, OVI_LIFCL_TIMING

Design Flow Manager

New Flowcharts

- HDL Synthesis

1. Aldec HES-SyntHESer 2021.07

2. Intel Quartus Prime Standard Synthesis & Implementation 21.1

3. Intel Quartus Prime Pro Synthesis & Implementation 20.4

4. Intel Quartus Prime Pro Synthesis & Implementation 21.1

5. Intel Quartus Prime Pro Synthesis & Implementation 21.2

6. Intel Quartus Prime Pro Synthesis & Implementation 21.3

7. Intel Quartus Prime Pro Synthesis & Implementation 21.4

8. Lattice Diamond LSE 3.12 (supports Diamond LSE 3.12 SP1)

9. Lattice Synthesis & Implementation in Diamond 3.12 (supports Diamond 3.12 SP1)

10. Lattice Radiant Software LSE 3.0

11. Lattice Synthesis & Implementation in Radiant Software 3.0

12. Synopsys Synplicity Synplify Pro R-2020.09 for Actel/Microsemi (supports Synplify Pro R-2020.09M-SP1-1)

13. Synopsys Synplicity Synplify Pro R-2021.03 for Actel/Microsemi (supports Synplify Pro R-2021.03M)

14. Synopsys Synplicity Synplify Pro R-2020.09 for Lattice (supports Synplify Pro R-2020.09LR-SP1)

15. Synopsys Synplicity Synplify Pro R-2021.03 for Lattice (supports Synplify Pro R-2021.03L-SP1)

16. Xilinx Vivado 2020.3 Synthesis

17. Xilinx Vivado 2021.1 Synthesis

18. Xilinx Vivado 2021.2 Synthesis

19. Xilinx Vivado 2020.3 Synthesis & Implementation

20. Xilinx Vivado 2021.1 Synthesis & Implementation

21. Xilinx Vivado 2021.2 Synthesis & Implementation

- Implementation

1. Intel Quartus Prime Standard Implementation 21.1

2. Intel Quartus Prime Pro Implementation 20.4

3. Intel Quartus Prime Pro Implementation 21.1

4. Intel Quartus Prime Pro Implementation 21.2

5. Intel Quartus Prime Pro Implementation 21.3

6. Intel Quartus Prime Pro Implementation 21.4

7. Lattice Diamond 3.12 (supports Diamond 3.12 SP1)

8. Lattice Radiant Software 3.0

9. Microsemi Libero SoC 12.6

10. Microsemi Libero SoC 2021.1

11. Microsemi Libero SoC 2021.2

12. Xilinx Vivado 2020.3 Implementation

13. Xilinx Vivado 2021.1 Implementation

14. Xilinx Vivado 2021.2 Implementation

Updated Flowcharts

- HDL Synthesis

1. Lattice ispLEVER Classic LSE (supports ispLEVER Classic LSE 2.1)

2. Lattice Radiant Software LSE 2.2 (supports Radiant Software LSE 2.2.1)

3. Lattice Synthesis & Implementation in Radiant Software 2.2 (supports Radiant Software 2.2.1)

4. Synopsys Synplicity Synplify Pro P-2019.03 for Actel/Microsemi (supports Synplify Pro P-2019.03A-SP1)

5. Synopsys Synplicity Synplify Pro Q-2020.03 for Actel/Microsemi (supports Synplify Pro Q-2020.03M-SP1)

6. Synopsys Synplicity Synplify Pro Q-2020.03 for Lattice (supports Synplify Pro Q-2020.03L-SP1 and Synplify-PRO Q-2020.03LR-SP1-1)

- Implementation

1. Lattice ispLEVER Classic (supports ispLEVER Classic 2.1)

2. Lattice Radiant Software 2.2 (supports Radiant Software 2.2.1)

3. Actel/Microsemi Designer 9.2 (supports Microsemi Libero IDE 9.2 SP4)

Flowchart Changes and Improvements

- The use of the controls such as tabs, combo boxes, and spin boxes located in the Design Flow Manager dialog boxes has been improved. Now, the settings in these controls can be changed by using the mouse wheel. The change is available for the latest versions of the vendor flowcharts.

- The temperature and static power parameters have been extracted from the Speed Grade option in the Xilinx Vivado 2020.x flowcharts. The options for controlling these parameters are available for certain devices in the General tab of the Synthesis Options dialog box and the Main tab of the Implementation Options dialog box. If an UltraScale, UltraScale+, or Versal family is selected, the temperature parameter is controlled with the Temperature option. If a Versal family is selected, there is also the Static Power option available that controls the static power parameter.

- The Reserve Probe option has been enabled for all device families in the Microsemi Libero SoC 12.5 and newer flowcharts. (SPT81126)

Discontinued Flowcharts

- HDL Synthesis

1. Synopsys FPGA Compiler II

2. Synopsys FPGA Express

3. Synopsys FPGA Express (Innoveda OEM)

4. Synopsys FPGA Express (Viewlogic OEM)

5. Synopsys FPGA Express (Xilinx OEM)

- Physical Synthesis

1. Magma PALACE 1.2, 2.0, 3.0, 3.1, 3.2, 3.3 for Actel/Microsemi

2. Magma PALACE 2.4, 2.5 for Altera and Xilinx

Block Diagram Editor

- The order of ports, generics, and parameters in generated code can be changed with the Sorting Order option accessible from the Generation | Declaration of Ports category of the Preferences dialog box. If Declaration is selected, the order is compliant with the sequence in which the objects were added to the diagram. If Legacy is selected, the items are grouped by their modes and items in each group are listed in the alphabetical order. The order can be also changed with the generationsortingorder macro command. See the Scripts section for details. (SPT80109, SPT80162)

- The Port Mapping tabs of the Symbol Instance Properties and Fub Instance Properties dialog boxes have been rearranged. The Port Mapping Details window invoked with the Details button and the Details button itself are no longer available. The content of that window is presented directly in the Port Mapping tab as new columns in the table and can be enabled with the Details check box.

- The behavior of the Format Diagram Items toolbar has been changed. Now, modification of object properties is possible for selected block diagram items and it does not influence the global editor settings specified in the Appearance category of the Preferences dialog box.

State Diagram Editor

- The order of ports, generics, and parameters in generated code can be changed with the Sorting Order option accessible from the Generation | Declaration of Ports category of the Preferences dialog box. If Declaration is selected, the order is compliant with the sequence in which the objects were added to the diagram. If Legacy is selected, the items are grouped by their modes and items in each group are listed in the alphabetical order. The order can be also changed with the generationsortingorder macro command. See the Scripts section for details. (SPT80109, SPT80162)

Stimuli Window

- The Sequences dialog box has been introduced. The window allows creating keyboard shortcuts activating sequences of actions controlling stimuli. To open the Sequences dialog box, pick the Sequences option from the Tools menu. Notice that the dialog box provides the functionality that was previously available in the Hotkeys tab of the Stimulators dialog box (which was removed from the current edition). For more information, refer to the Dialog Box Reference chapter of the User's Guide.

- The Set Stimulus option has been added to the context menu of signals presented in the Watch and Advanced Dataflow windows. The option allows associating the signals with stimuli defined by using the Stimuli window or the force macro command.

- The Stimulators dialog box has been removed from the Active-HDL environment. The window was a tool for creating stimuli included in the Waveform Viewer. Currently, it is replaced by the standalone Stimuli window, the Stimulus Properties dialog box, and the Sequences dialog box which has been introduced in this version. All the actions that were possible to execute in the Stimulators dialog box can now be accomplished in these windows. The stimuli created with the Stimulators dialog box and saved to a file in previous editions can be imported. Refer to the Scripts section for details.

- The Stimulators option was removed from the context menus of signals presented in the Signal Grid pane of the Waveform Viewer window and the Structure tab of the Design Browser window (i.e. the Hierarchy Viewer). The option opened the Stimulators dialog box which was removed in the current edition. In the Assertion Viewer window, the option was replaced with the Set Stimulus option providing access to stimuli created in the Stimuli window.

- The Assign as Stimulator option assigning an editable signal as a stimulus to its original version that was working independently of the Stimuli window and was accessible from the context menu of the Signal Grid pane of the Waveform Viewer has been removed. Notice that the Assign as Stimulus option executing equivalent action in the Stimuli window is available in the context menu.

Scripts

The following changes have been introduced to the Active-HDL macro commands:

- The -aserror argument has been added to the syntax of the acom command. The argument allows raising severity of any warning message printed by the VHDL compiler to the error level.

- The -input_ports argument has been added to the syntax of the alog command. The new argument allows specifying the default kind for an input port declared with a type reg but without the use of the var keyword.

- The filepsloptions command has been implemented. The new command allows applying the global -auts argument of the acom or alog command to the specified PSL source files. The command is the equivalent of the Change the evaluation of asynchronous assertions into continuous mode option available in the Compile tab of the File Properties dialog box of a PSL source file attached to the design tree.

- The -atck argument of the alog command is no longer supported and it has been removed from the command syntax. The -assert_clock_count argument is a successor of the obsolete argument. The new argument allows enabling or disabling the clock tick counts and displaying them in a assertion/cover report. This argument has been also added to the syntax of the acom command.

- The new 1800.2-2020 parameter of the -uvmver argument has been added to the syntax of the alog command.

- The -vhdl_strict_range_check argument has been added to the syntax of the asim command. The new argument disables optimizations that can prevent the simulator from checking whether a signal value falls within the specified value range.

- The filter command and the -filter argument of the asim command support the ELBREAD_0049, RUNTIME_0155, RUNTIME_0177, RUNTIME_0222, RUNTIME_0230, and RUNTIME_0375 simulator messages. (SPT79842)

- The -vc6, -vc7, -vc8, and -vc9 arguments have been removed from the syntax of the ccomp command and they are no longer supported. The support for Microsoft Visual C++ compiler ver. 6.0-9.0 has been discontinued.

- The execution of the force command creates a new stimuli in the current active set of stimuli presented in the Stimuli window.

- The stimuli created with the force command or the Stimuli window are not applied to signals if they were set before the restart or initialization of the simulation session. The reason is that these operations deactivate the current active set presented in the Stimuli window. To make sure the user is informed about this situation, the warning message: The stimuli set <name> has been made inactive is displayed in the Console window. To apply stimuli to signals, mark the <name> set as active in the Stimuli window. Notice that this behavior can be changed in the Preferences dialog box. Refer to the Design Management section for details.

- The generationsortingorder command, which has been introduced in this edition, allows the user to choose the order of ports and generics/parameters in code generated from BDE and FSM diagrams. The command can be invoked with the declaration or legacy arguments that are equivalent to the Declaration and Legacy values of the Sorting Order option from the Active-HDL preferences, respectively. Refer to the Block Diagram Editor or State Diagram Editor sections for details.

- The importqsys and importplatformdesigner commands are no longer supported.

- The -hde argument has been removed from the syntax of the open, opendocument, and addfile commands.

- The -hideprocesses and -showprocesses arguments of the structure command are deprecated. It is recommended to use the -filter concurrent argument with the off and on parameters instead, respectively. (SPT79367)

- The stimuli created with the Stimulators dialog box or the force macro command and saved to a file in previous editions can be imported by using the force argument of the write macro command and then by executing the macro produced by this command. The exception are the legacy stimuli of the Hotkey and Predefined types which cannot be imported. For details, refer to the description of the force argument of the write command in the Macro Command Reference chapter.

- The stimulators argument of the write command exporting the legacy stimuli created in the previous editions has been replaced with the stimuli argument exporting the new stimuli created with the Stimuli window or the force macro command. The exported stimuli are written to the XML file format.

The following changes have been introduced to the predefined Active-HDL variables:

- The tclerrornotboolean variable is no longer supported.

- In previous versions, the acom, alog, asim, buildc, and edfcomp macro commands returned the execution status (0 when failed and 1 if succeeded) when they were used in Tcl scripts or DO macros executed in the Tcl/Compatibility mode, for example:

- The resume_on_error variable has been implemented. The new variable allows resuming the execution of Tcl scripts or DO macro commands run in the Tcl/Compatibility mode after they have been terminated by an error. When the variable is set to 0 or if it is not set, the error will break macro execution. Otherwise, if the variable is set to 1, a macro/script interrupted by an error will be resumed. In order to use the variable, it must be set in the DO mode.

User Interface

- The autocomplete mechanism available in the HDL Editor and the Console window has been improved. Now, autocompletion of the folder and file names also works for all the supported native Tcl commands and for the user-defined commands created by using the Tcl proc command. (SPT79963)

- The behavior of the Disable VHDL 1076-1987 syntax option available in the Preferences (Compilation|VHDL Compiler), Design Settings (Compilation|VHDL), and File Properties (Compile) dialog boxes has changed. Now, the option is only available when the Standard version option is set to either the VHDL 1076-1993 or VHDL 1076-2002 value. If any remaining value is selected, the Disable VHDL 1076-1987 syntax option is disabled.

- The Resources tab of the Design Browser window displays by default four new resource folders that allow filtering the additional design files of the following extensions:

. Coverage Databases (filters the files with the *.acdb extension)

. Matlab/Simulink Files (shows the files with the *.m, *.mdl, and *.slx extensions).

. Profiler Databases (displays the files with the *.tbp extension)

. Script Files (presents the files with the *.do, *.tcl, and *.pl extensions).

- Due to the discontinued import of simulation scripts generated by Intel's Qsys and Platform Designer system integration tools, the Altera/Intel Qsys Simulation Script and Intel Platform Designer Simulation Script options have been removed from the File | Import menu.

- The HDL Code Statistics option is no longer available from the Tools menu. To start the tool that analyzes design source files, execute the $aldec\bin\clocGui.exe program. Note also that in the future releases of Active-HDL, HDL Code Statistics will be delivered as a command-line tool only.

- The new color themes are available. Starting from this version of Active-HDL, the dark and dark high contrast themes are provided. Additionally, the new Appearance Files (*.app) are provided for the most frequently used Active-HDL windows such as HDL Editor, Block Diagram Editor, Waveform Viewer, Memory Viewer, Console window, Advanced Dataflow window, and debugging tool windows. The new theme files are grouped and stored in separate subfolders of the $aldec\preferences\color_theme directory. Note also that the previous predefined Appearance Files for the Waveform Viewer (asdb_wave_black_background.app, asdb_wave_lightgrey_background.app, and asdb_wave_white_background.app) installed to the $aldec\dat subfolder are no longer available. (SPT80254)

Installation

– The installation program of Active-HDL has been upgraded to InstallShield ver. 2021 R2.

Active-HDL Interfaces and Wizards

The following changes and improvements have been made to the built-in third-party interfaces:

- Spec-TRACER Requirements Lifecycle Management System

. The previously offered interface to Spec-TRACER Requirements Lifecycle Management System has been replaced by a new version of the Spec-TRACER tool. Active-HDL 13 includes the preliminary version of the tool. Contact Aldec Support for more information.

The following changes and improvements have been made to the import of third-party projects:

- Active-CAD Import

. The support for the import of the Active-CAD projects will be discontinued in the future editions of Active-HDL.

- Altera/Intel Import

. The import of simulation scripts coming from Altera/Intel Qsys system integration tool has been discontinued. Due to this change, the corresponding GUI options as well as dedicated Do macros and Tcl commands are no longer available. Refer to the Scripts and User Interface sections for more information.

. The import of simulation scripts coming from Intel Platform Designer is no longer supported. Due to this change, the corresponding GUI options, dedicated Do macros, and Tcl commands are no longer available. For the detailed information on using Platform Designer simulation scripts in the current version of Active-HDL, see the Performing Functional Simulation of the system created with Platform Designer in Active-HDL application note on the Aldec website. For further information about related changes of the import feature, refer to the Scripts and User Interface sections in this document.

Active-HDL is an integrated environment designed for development of VHDL, Verilog/SystemVerilog, EDIF, and SystemC designs. It comprises of several design entry tools, HDL/SystemC compiler, single simulation kernel, several standard and advanced debugging tools, graphical and textual simulation output viewers, and many auxiliary utilities designed for easy management of designs, resource files, and libraries as well as built-in interfaces that allow running simulation, synthesis, or implementation locally or on remote computers, controlling revision of source files, or communicating with third-party tools that provide simulation models.

In addition, Active-HDL provides a set of powerful wizards which facilitate creation of new workspaces, designs or design resources including VHDL, Verilog, SystemC source files, block or state diagrams, testbenches, etc.

Most operations that you perform from the graphical user interface can be also invoked through the commands of the Active-HDL macro language. By writing your own macros, you can significantly improve testing and automate design processing. Active-HDL also provides scripting engines for Perl and Tcl/Tk. By creating user-defined scripts, you can enhance Active-HDL design environment by adding additional windows, extending the macro language, and providing interfaces to external tools and software products.

The Active-HDL suite also includes VSimSA, a standalone VHDL/Verilog/SystemVerilog/EDIF/SystemC simulation environment designed for batch processing. Functionally, VSimSA is entirely independent of Active-HDL. What distinguishes VSimSA from Active-HDL is the lack of a graphical user interface (GUI). VSimSA commands and programs are issued and controlled exclusively from a command-line, which is especially useful in an automated design testing.

Active-HDL 13 provides many new features and enhancements that simplify team-based design, increase design productivity and the speed of behavioral, RTL, and timing simulation of VHDL, Verilog, SystemC, SystemVerilog and EDIF projects.

Established in 1984, Aldec is an industry leader in Electronic Design Verification and offers a patented technology suite including: RTL Design, RTL Simulators, Hardware-Assisted Verification, SoC and ASIC Prototyping, Design Rule Checking, CDC Verification, IP Cores, High-Performance Computing Platforms, Embedded Development Systems, Requirements Lifecycle Management, DO-254 Functional Verification and Military/Aerospace solutions.

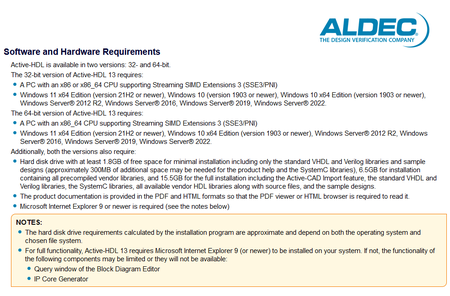

Product: Aldec Active-HDL

Version: 13.0.375.8320

Supported Architectures: x64

Website Home Page : www.aldec.com

Languages Supported: english

System Requirements: Windows *

Size: 577.5 mb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please