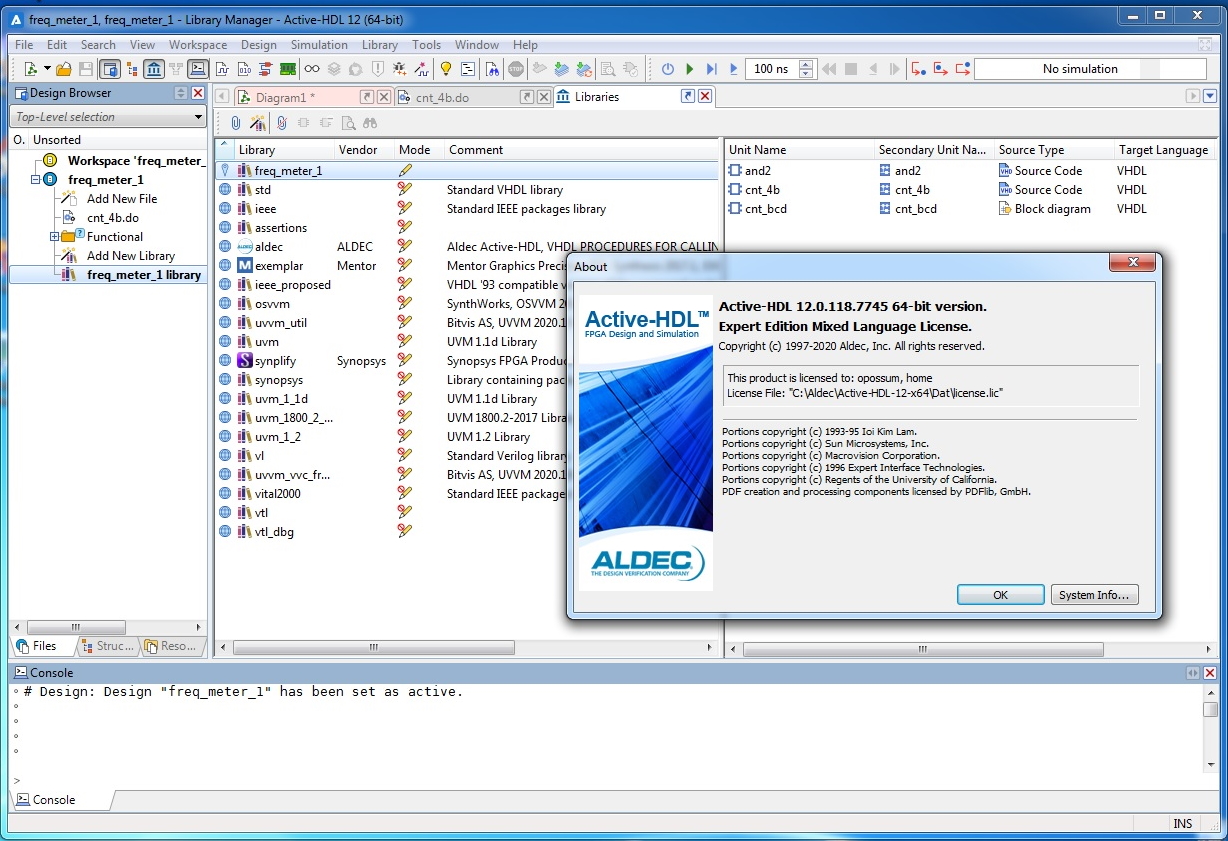

Aldec Active-HDL 12.0.118.7745 | 550.4 mb

Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification for FPGA and ASIC designs, has enhanced Active-HDL to support new features within VHDL-2019 (IEEE 1076-2019). These features simplify the language, lift certain restrictions that were present in earlier versions and introduce new application programming interfaces (APIs).

Support has also been added for release 2020.08 of the open source VHDL verification methodology (OSVVM).

Support for OSVVM 2020.08 gives users of Active-HDL access to the free and open-source methodology’s new requirements tracking, updated scripting, AXI4 full verification components, and model independent transactions.

The latest version of Active-HDL also sees SystemVerilog enhancements that include initial support for multidimensional arrays of instances, preliminary support of unresolved user-defined nettypes, and preliminary support for unique constraints.

Several non-standard extensions to SystemVerilog are present in the latest release of Active-HDL too. These include allowing variable type outputs of clocking blocks to be driven by a continuous assignment, allowing the use of foreach loops iterating over the elements of a subarray, and assigning a virtual interface with a modport to a virtual interface without a modport.

Active-HDL is an integrated environment designed for development of VHDL, Verilog/SystemVerilog, EDIF, and SystemC designs. It comprises of several design entry tools, HDL/SystemC compiler, single simulation kernel, several standard and advanced debugging tools, graphical and textual simulation output viewers, and many auxiliary utilities designed for easy management of designs, resource files, and libraries as well as built-in interfaces that allow running simulation, synthesis, or implementation locally or on remote computers, controlling revision of source files, or communicating with third-party tools that provide simulation models.

In addition, Active-HDL provides a set of powerful wizards which facilitate creation of new workspaces, designs or design resources including VHDL, Verilog, SystemC source files, block or state diagrams, testbenches, etc.

Most operations that you perform from the graphical user interface can be also invoked through the commands of the Active-HDL macro language. By writing your own macros, you can significantly improve testing and automate design processing. Active-HDL also provides scripting engines for Perl and Tcl/Tk. By creating user-defined scripts, you can enhance Active-HDL design environment by adding additional windows, extending the macro language, and providing interfaces to external tools and software products.

The Active-HDL suite also includes VSimSA, a standalone VHDL/Verilog/SystemVerilog/EDIF/SystemC simulation environment designed for batch processing. Functionally, VSimSA is entirely independent of Active-HDL. What distinguishes VSimSA from Active-HDL is the lack of a graphical user interface (GUI). VSimSA commands and programs are issued and controlled exclusively from a command-line, which is especially useful in an automated design testing.

Active-HDL 12 provides many new features and enhancements that simplify team-based design, increase design productivity and the speed of behavioral, RTL, and timing simulation of VHDL, Verilog, SystemC, SystemVerilog and EDIF projects.

Active-HDL 12 is offered in an FPGA vendor-independent edition and supports all leading C/HDL synthesis and implementation tools which can be started directly from the Active-HDL environment. The installation program automatically installs all system libraries and allows selecting both target FPGA technology and vendor-specific libraries required for running HDL simulation.

Established in 1984, Aldec is an industry leader in Electronic Design Verification and offers a patented technology suite including: RTL Design, RTL Simulators, Hardware-Assisted Verification, SoC and ASIC Prototyping, Design Rule Checking, CDC Verification, IP Cores, High-Performance Computing Platforms, Embedded Development Systems, Requirements Lifecycle Management, DO-254 Functional Verification and Military/Aerospace solutions.

Product: Aldec Active-HDL

Version: 12.0.118.7745

Supported Architectures: x64

Website Home Page : https://www.aldec.com/

Language: english

System Requirements: PC *

Size: 550.4 mb

Best PC configuration for Active-HDL

What PC configuration should I buy to run Active-HDL?

ANSWER:

1. CPU parameters

- Single core vs. dual or multi core – Active-HDL is multithreaded application, thus picking a multi-core CPU is better than a single-core one. The effect of using multi-core CPU would be seen the most in case of interactive work with Active-HDL’s GUI while the simulation is running (the simulation will occupy one processor core, while the GUI operations will run on the other). In addition the VHDL compiler takes advantage of multi-core CPU to reduce the compilation time. Even if you don’t browse the waveform or edit your code while your simulation is running, having multi-core CPU will let your other applications be more responsive while you run a simulation in the background.

- Frequency and CPU Cache size – typically the approach here is the more the better. Note that a larger CPU cache has a positive impact on the performance.

- Architecture – 32 vs 64 bit

The CPU architecture only matters if Active-HDL needs to allocate a few gigabytes of RAM to run your design. 64 bit architecture enables allocation of 4GB RAM even for the 32 bit applications (like Active-HDL), while 32 bit architecture is limited to 2GB on Windows that can be optionally increased up to 3GB. So, if simulation of your design does not require more than 2GB of RAM then feel free to select any architecture.

2. Graphical card – we don’t have any special recommendations here but the faster the card the more responsive GUI operations such as Waveform will be (in case of scrolling through large files, zooming, etc.).

3. RAM size – On 32 bit Windows we recommend at least 3GB of RAM. On 64 bit OS we recommend 4GB or more. Note that these recommendations are considered for running one instance of Active-HDL on the machine at a time. If you plan to run more than one, than multiply the above numbers accordingly.

What PC configuration should I buy to run Active-HDL?

ANSWER:

1. CPU parameters

- Single core vs. dual or multi core – Active-HDL is multithreaded application, thus picking a multi-core CPU is better than a single-core one. The effect of using multi-core CPU would be seen the most in case of interactive work with Active-HDL’s GUI while the simulation is running (the simulation will occupy one processor core, while the GUI operations will run on the other). In addition the VHDL compiler takes advantage of multi-core CPU to reduce the compilation time. Even if you don’t browse the waveform or edit your code while your simulation is running, having multi-core CPU will let your other applications be more responsive while you run a simulation in the background.

- Frequency and CPU Cache size – typically the approach here is the more the better. Note that a larger CPU cache has a positive impact on the performance.

- Architecture – 32 vs 64 bit

The CPU architecture only matters if Active-HDL needs to allocate a few gigabytes of RAM to run your design. 64 bit architecture enables allocation of 4GB RAM even for the 32 bit applications (like Active-HDL), while 32 bit architecture is limited to 2GB on Windows that can be optionally increased up to 3GB. So, if simulation of your design does not require more than 2GB of RAM then feel free to select any architecture.

2. Graphical card – we don’t have any special recommendations here but the faster the card the more responsive GUI operations such as Waveform will be (in case of scrolling through large files, zooming, etc.).

3. RAM size – On 32 bit Windows we recommend at least 3GB of RAM. On 64 bit OS we recommend 4GB or more. Note that these recommendations are considered for running one instance of Active-HDL on the machine at a time. If you plan to run more than one, than multiply the above numbers accordingly.

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please